## Exploring New Frontiers of High-Performance Verification with UVM-AMS

Tim Pylant, Cadence Design Systems, UVM-AMS WG Vice-Chair

### What Does DMS/AMS Refer To?

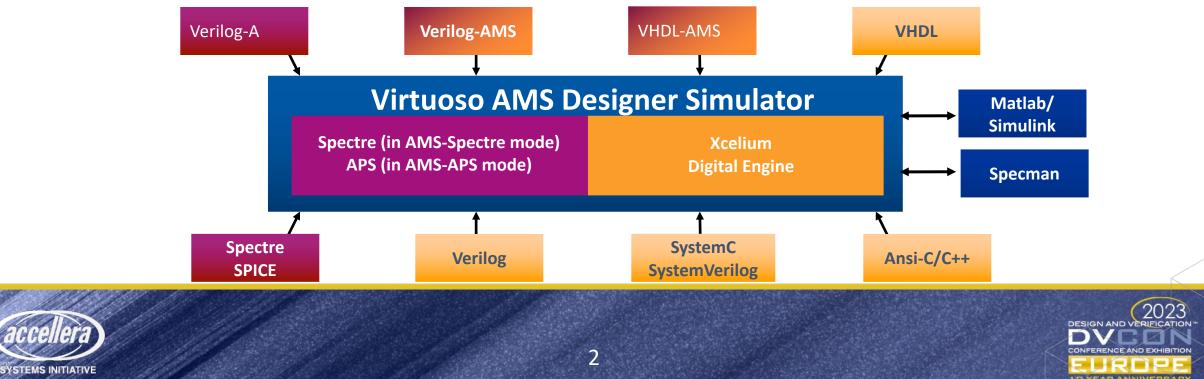

- AMS: Mixed signal with electrical (includes schematics/Spice, Verilog-AMS, Verilog-A) Spectre and Xcelium

- DMS: Mixed signal with discrete real numbers (no electrical) Xcelium only

- Pure Digital: Only logic (SystemVerilog/Verilog/VHDL) Xcelium only

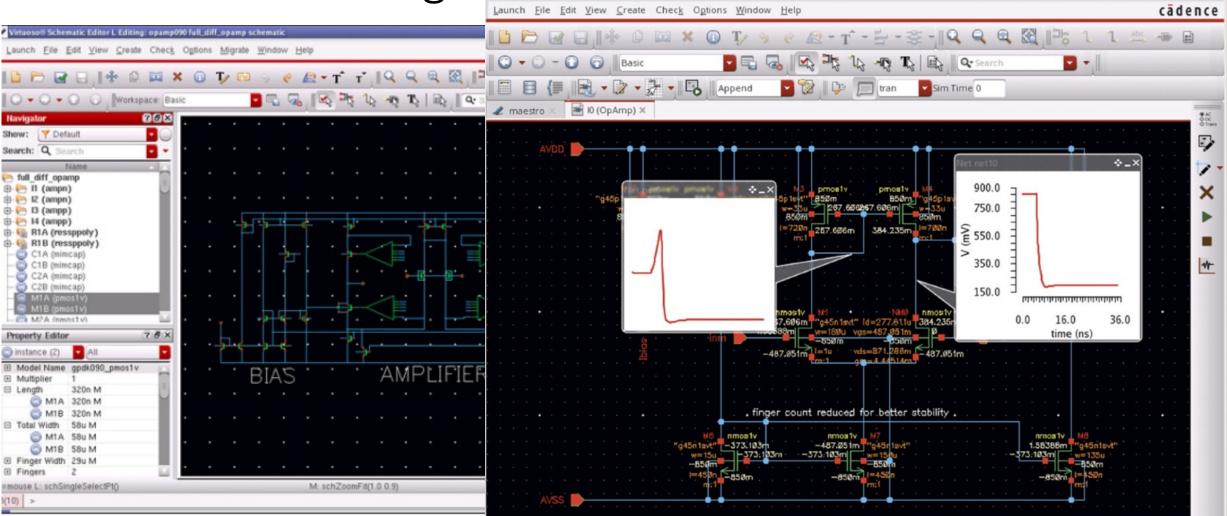

### Traditional MS Design

🔗 Virtuoso & ADE Explorer Reading: Two\_Stage\_Opamp OpAmp schematic\_Config: Two\_Stage\_Opamp OpAmp\_TF 🗕 🗖 >

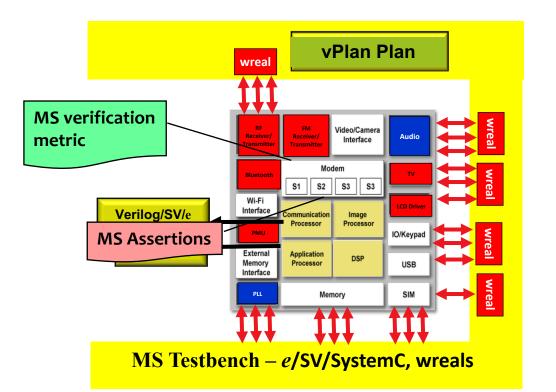

### Cadence View of Mixed-signal Verification Issues

- Mixed-signal verification issues in today's flow

- Performance vs. accuracy of analog models

- Transistor models execute too slow for SoC verification

- Verilog behavioral models have higher performance but do not accurately represent analog models

- Verilog model not kept in sync with analog model

- Working with digital designs

- Connectivity errors not being caught

- Spec assumptions not verified between analog and digital

- Lack of coverage of the analog design across MS boundary

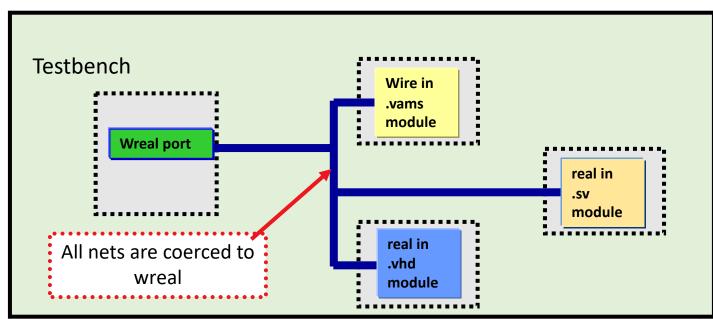

### Real-wire Coercion

- When a wire or interconnect is connected to a net of the type wreal, SystemVerilog real, or VHDL real, it is coerced (forced) to wreal

- Coercion can occur across multiple hierarchical levels

- The coercion process allows a seamless connection of devices without worrying about the interconnects and their types

- Different configuration or interconnect might be used to connect electrical ports

- It allows for different design/ model abstractions without recoding interconnects

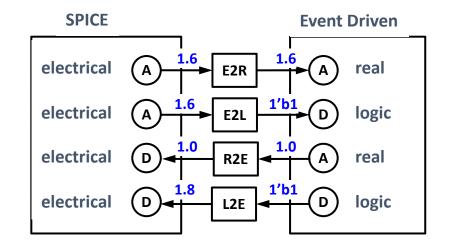

### Auto-Inserted Connect Modules (AICM)

- The concept of automatic inserted connect modules applies

- Between discrete (logic and real) and continuous, such as electrical domain (E2L/L2E, R2E/E2R)

- Between two discrete domains, such as real to logic connection (R2L/L2R)

- CMs allow design blocks to be seamlessly switched without needing to recode the interconnect Hand-coded conversion Auto-Inserted Connect Module or port types. It supports MixedSig electrical logic Conversion logic electrical multiple power supply AICM Block sensitivities used in value conversion Digital Analog Digital Analog Block Block Block Block

6

### Disciplines

- Continuous disciplines

- electrical

- Potential and flow

- Kirchhoff's laws KCL/KVL

- voltage

- Only potential

- Discrete disciplines

- logic

- Discipline resolution algorithm

- Incompatible boundaries have CM/IEs auto-inserted during elaboration phase

- Types of IEs: E2R/R2E, L2R/R2L, E2L/L2E, Bidirectional RNM, Bidirectional conservative flow

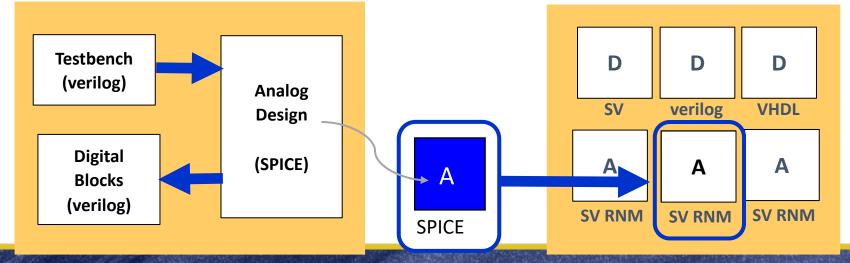

### AMS Xcelium Use Model

- Sign off analog IP with AVUM flow

- Schematics => Generate SPICE netlist

- Plug and play into SV UVM testbench (TB re-use)

- Verify critical path scenarios, i.e. POR, timing, dynpower, power seq, etc.. Analog/AMS Design Verification Digital Design Verification

### AMS Control File (amsd block)

The "heart of the AXUM flow" ease of use

- Create and configure with the AMS Control file(amscf.scs)

- Spice block substitution (portmap card)

- Cell, instance Bindings (config card)

- Interface element declarations (ie card)

- Multiple supplies (ie card)

- Verilog-Spice-Verilog sandwiching(use=spice, use=hdl)

- Includes Spice file pointers and analog control file

- Read directly by xrun:

- % xrun amscf.scs <other\_files\_and\_options>

- amsd block settings assign cell and instance bindings using AMS xrun binding engine

If we have automated technologies that take care of coercion and inter-discipline connections,

## why do we need UVM-AMS?

### MS-SoC: Mixed simulation env using RNMs & analog models

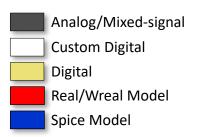

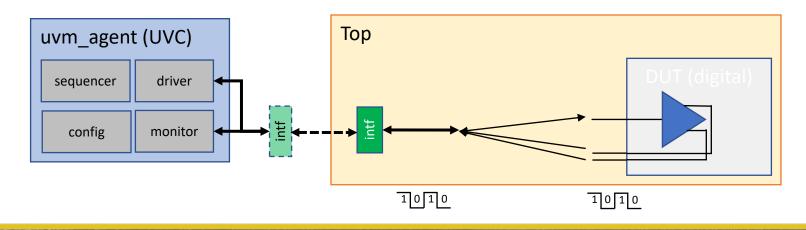

### Classical UVM Example

### What Is UVM-MS?

- Define a way to extend UVM to AMS/DMS

- Modular and reusable testbench components

- Sequence-based stimulus

- Take advantage of UVM infrastructure as much as possible

- Reuse as much UVM as possible as DUT is refined from digital to AMS

- Use extension/factory as much as possible

- Support UVM architecture for DMS/AMS DUT from the start

- Define standard architecture for D/AMS interaction

- Minimize traffic across the boundary

- Enable development of D/AMS VIP libraries and ecosystem

## Generating/Driving Continuous Analog Signals

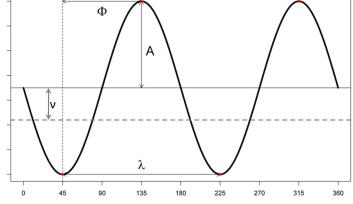

- An analog signal that is not simple DC or a slow-changing signal must be a periodic waveform like a sine wave, a sawtooth, or some composition of such sources.

- For example, a signal generator for a sine wave can be controlled by four control values, determining the freq(1/λ), phase(Φ), amplitude(A), and DC bias(v) of the generated signal.

- The properties of the analog signal being driven are controlled by real values generated by the sequencer.

- A UVM sequence\_item contains fields for all the control parameters.

- The driver converts the transaction to a setting for the signal generator.

### Requirements

- Minimal changes to UVC to add MS capabilities (driver, monitor, sequence item) that can be applied using set\_type\_override\_by\_type

- Define analog behavior based on a set of parameters defined in a sequence item and generate that analog signal using an analog resource (MS Bridge)

- Measure the properties of the analog signal, return them to a monitor, and package those properties into a sequence item

- Drive and monitor configurations, controlled by dedicated sequence items and support easy integration into multi-channel test sequences

- Controls can also be set by way of constraints for pre-run configurations.

- Collect/check coverage in the monitor based on property values returned from the analog resource or add checkers in the analog resource

# EEnet Modeling

### SystemVerilog 2012 Extended Nettype Capabilities

- Definition of "nettype" construct applicable to any datatype

- Application to real datatype provides construct equivalent to VAMS "wreal"

- Cadence package "cds\_rnm\_pkg" defines nettypes for SV identical in name & operation to VAMS wreal flavors: wreal1driver, wreal4state, wrealavg, wrealsum, etc

- User Defined Type (UDT) can use a struct of multiple values to define a net

- User Defined Resolution (UDR) functions can define how the net should merge multiple drivers of the UDT format to define the resultant net value

- This extends the possibilities of how interfaces between blocks are defined

- Cadence "EE\_pkg" defines a nettype to define an electrical interface

- Multiple drivers can each drive the net with voltage or current and resistance values

- Resolution function computes resulting net voltage

net

Blk2

### How Is an EEnet Defined?

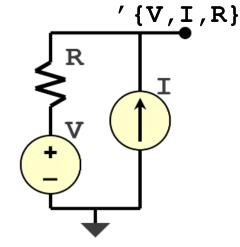

- The "EEnet" UDT specifies three fields:

- V = voltage driving net

- I = current driving the net

- R = resistance driving the net

- This allows lots of options for how the net can be driven:

- Specify  ${\mathbb V}$  and  ${\mathbb R}$  with  ${\tt I=0}$  for voltage with series resistance

- Specify I and R with V=0 for current with parallel resistance

- Specify V with R=0 for ideal voltage source

- Specify I with R=`wrealZState for ideal current source

- Resolution with included UDR function provides:

- V = resolved node voltage, or `wrealXState if multiple ideal voltage drivers

- I = 0 normally, or current through voltage source if driven by ideal voltage source

- R = effective impedance at node (parallel combination of all connected resistances)

- Re-evaluated whenever any driver changes

#### Format of EEnet Driver Definition

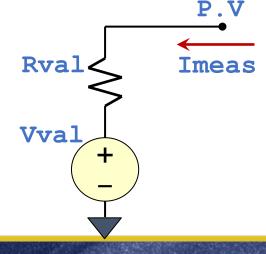

### Simple example of an EEnet driver code: V+R driving a node

```

assign Imeas = (Rval==0)? P.I : (P.V-Vval)/Rval; // measure current

```

endmodule

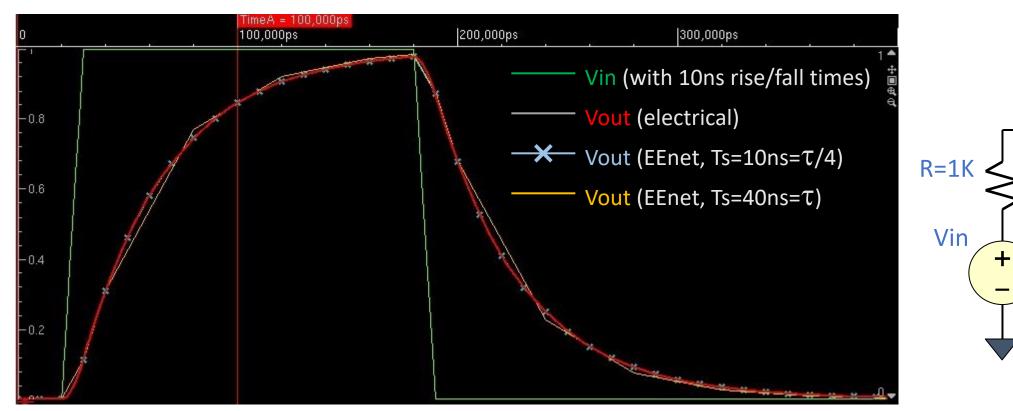

## Simple RC response using CapGeq model

- Sample rate of  $\tau/4$  generates points typically within 0.1% of analog waveform

- Sample rate equal to au still has well-controlled error considering large step size

Vout

C=40pF

## I<sup>2</sup>C example Using EEnet

```

import EE_pkg::*;  // access the definitions in EE_pkg

module i2c_target (

inout EEnet SDL,  // I<sup>2</sup>C SDA pin

inout EEnet SDL  // I<sup>2</sup>C SCL pin

);

assign SDA = '{Vval,0.0,Rval}; // drive voltage & resistance onto net

assign SCL = '{Vval,0.0,Rval}; // drive voltage & resistance onto net

endmodule

```

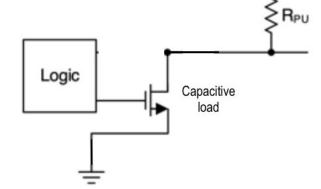

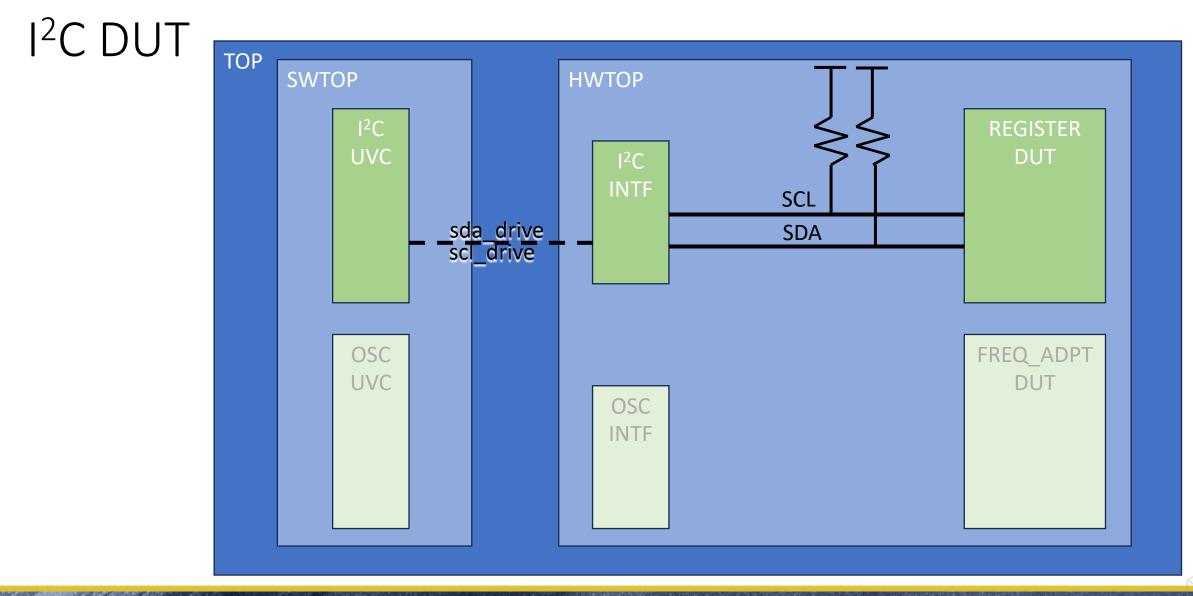

### Why Do We Need UVM-MS for $I^2C$ ?

• Cannot create analog behaviors from UVM class-based objects

- Need mechanism to control analog parameters

- Parameters not part of interface

# Applying UVM-MS to EEnet Model

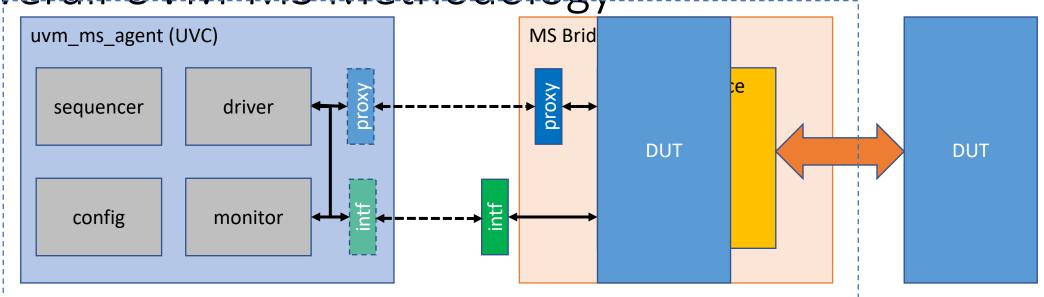

### **Overall UVM-MS Methodology**

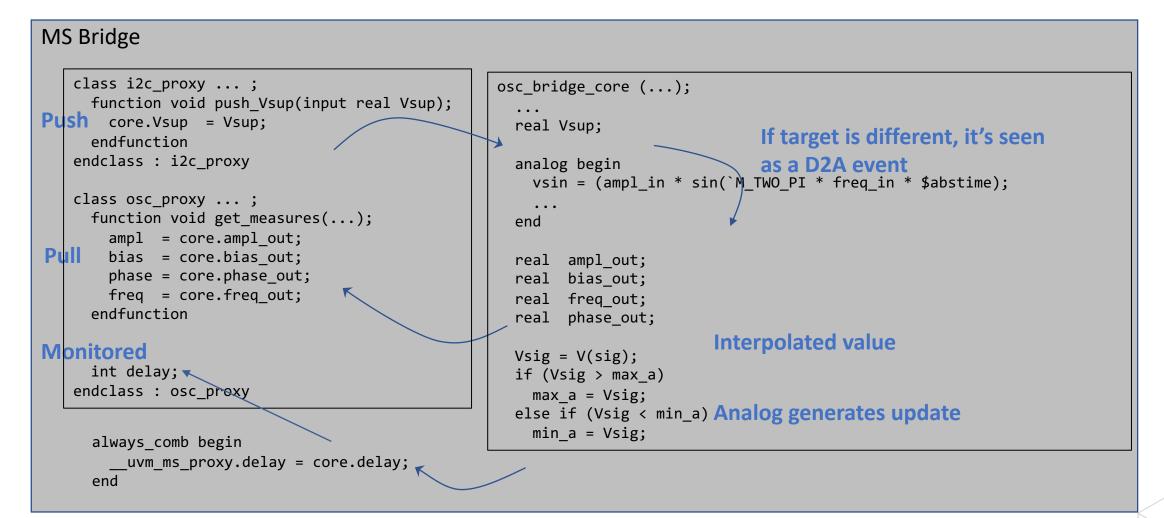

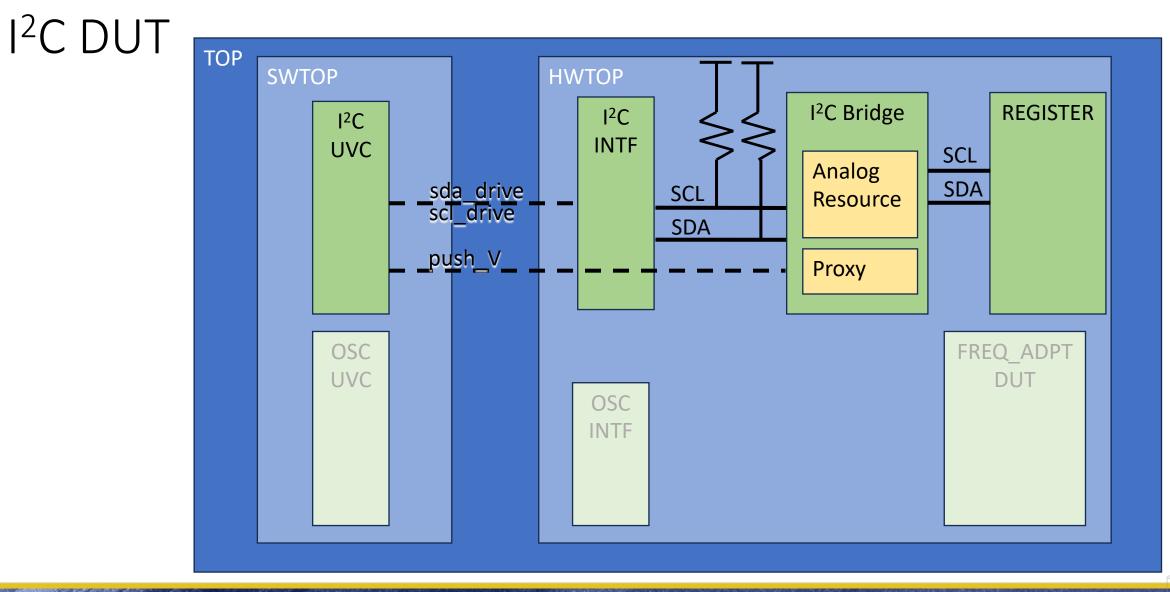

- MS Bridge is the proposed layer that sits between the UVC and the (A)MS DUT

- MS Bridge is a SV module that consists of a proxy API, SV interface, and an analog resource module

- The 'proxy' is an API that conveys analog attributes between the UVC and the MS Bridge

- The SV 'intf' passes digital/discrete signal values (logic, real, nettype/RNM) between UVC and MS Bridge

- The analog resource (SV, Verilog, or Verilog-AMS)

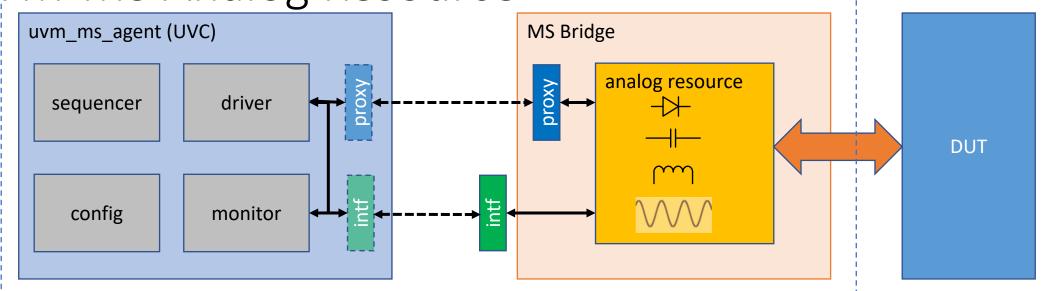

### **UVM-MS** Analog Resource

- MS testbench may require the behavior and presence of analog components that a typical UVM-RTL testbench could not include. These could be:

- Capacitors, Resistors, Inductors, Diodes, current/voltage sources etc. Or a complex passive network for multiple DUT pins.

- A piece of Verilog-AMS code

- Such components will be used to model the analog behavior of PADs, lossy transmission lines, loads/impedances, or any other voltage/current conditioning required to accurately model the signals connecting to the ports of DUT

- Those components can be placed inside the analog resource to be controlled by proxy.

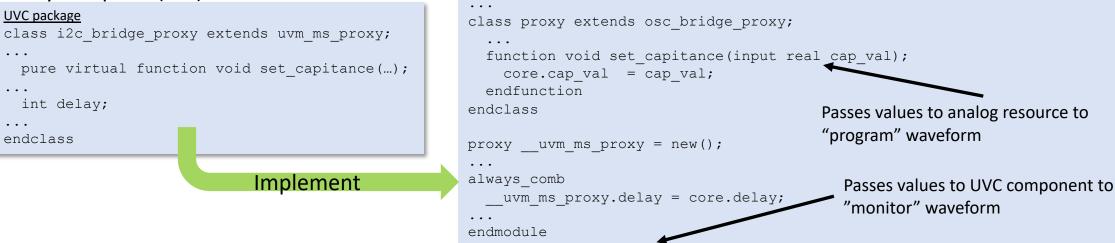

### Proxy "Hook-Up"

#### Proxy Template (API)

module osc bridge(...);

Proxy instance in MS Bridge module

osc bridge core #(...) core (...); // AMS model ←

#### UVM config setting

Instance of analog

resource

### $\mathsf{Proxy} \longleftrightarrow \mathsf{Analog} \ \mathsf{Resource}$

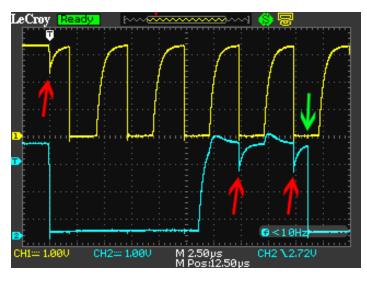

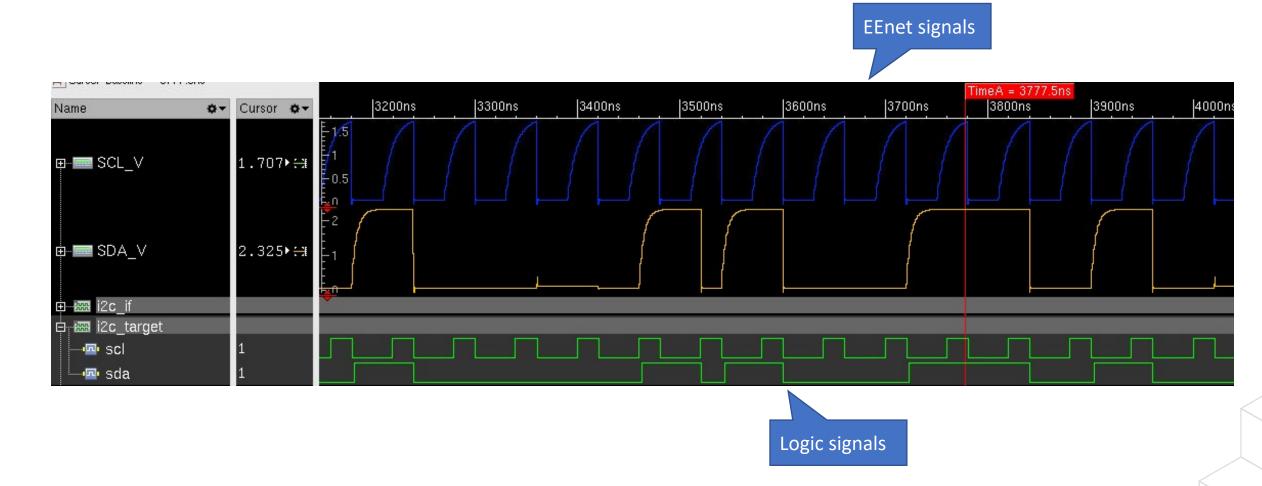

### I<sup>2</sup>C Waveforms

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

10 YEAR ANNIVERSARY

0

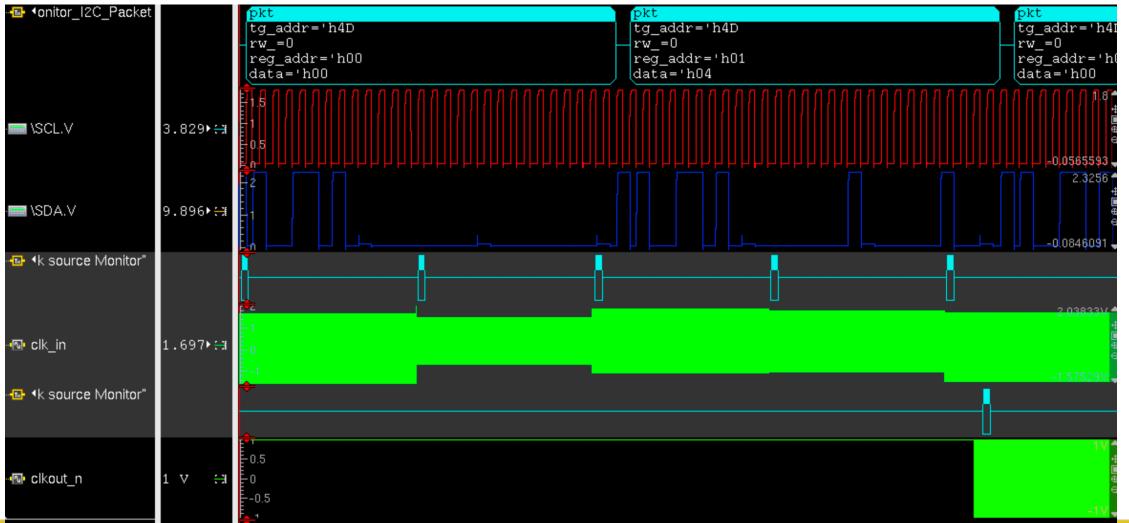

### Freq Adapter Waveforms

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

10 YEAR ANNIVERSARY

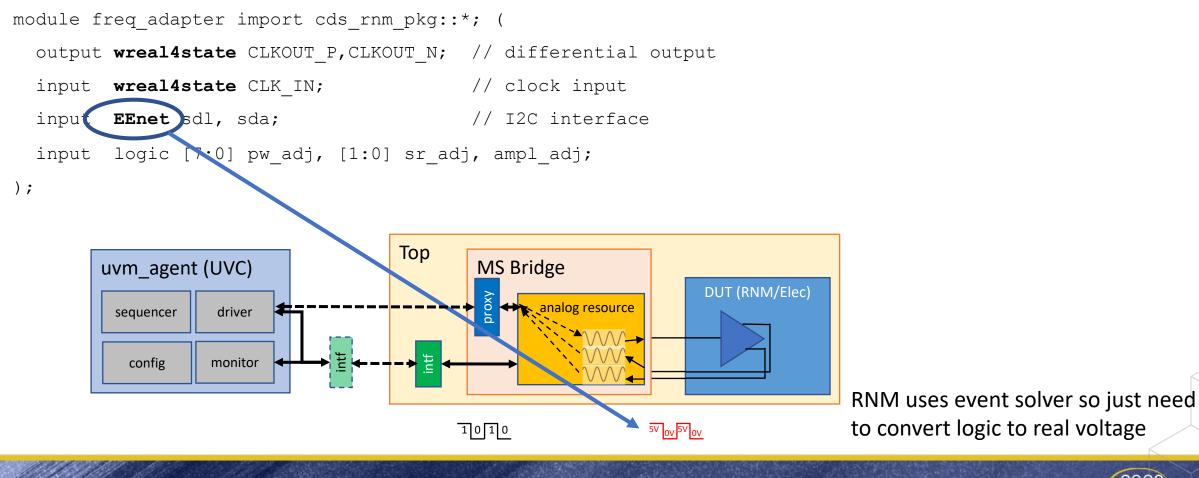

## Model of Frequency Adapter Ports in SV

```

module freq_adapter (

output logic CLKOUT_P,CLKOUT_N; // differential output

input logic CLK_IN; // clock input

input logic sdl, sda; // I2C interface

input logic [7:0] pw_adj, [1:0] sr_adj, ampl_adj;

);

```

## Model of Frequency Adapter Ports in SV RNM

# Example Walkthrough

UVM digital to UVM-MS

### Steps to Create a UVM-MS UVC

- Create Bridge module

- Contains Analog Resource and Proxy

- Extend classes for Driver

- Use set\_type\_override\_by\_type to use extended classes

#### i2c\_bridge 3 module i2c bridge import EE pkg::\*; ( input wire scl drive, // digital signal from driver 4 inout wire sda drive, // digital signal from driver 5 inout EEnet SDA, SCL // EEnet signals connected to DUT б 7 ); 8 9 parameter real Vsup p = 1.8; parameter real Rout = 100.0; 10 11 12 //UVM + MS extras 13 import uvm pkg::\*; import uvm ms pkg::\*; 14 `include "uvm macros.svh" 15 `include "uvm ms.svh" 16 17 //UVM package for this component 18 19 import i2c pkg::\*; 20 21 //Create an instance of a component that can be used with uvm info context to print // messages from analog resource using uvm ms info macro/function 22 23 `uvm ms reporter 24 25 //Class proxy extends the osc bridge proxy included in osc pkg.sv //The implementation for the config wave push function is defined here 26 class proxy extends i2c proxy; 27 function new(string name = "proxy"); 28 29 super.new(name); endfunction : new 30 31 32 // implementation of function to push Vsup value to analog resource 33 function void push Vsup(input real Vsup); 34 core.Vsup = Vsup; 35 endfunction 36 37 enactors 38 39 proxy uvm ms proxy = new(" uvm ms proxy"); 40 //Analog resource instantiation 41 i2c analog resource #(.Vsup p(Vsup p), .Rout(Rout)) core ( 42 43 .sda drive, .scl drive, .SDA, .SCL 44 ); 45

46 endmodule

SYSTEMS INITIATIVE

i2c driver  $\rightarrow$  i2c ms driver class i2c ms driver extends i2c driver; 1 class i2c driver extends uvm driver #(i2c packet); `uvm component utils(i2c ms driver) `uvm component utils(i2c driver) virtual interface i2c if vif; virtual interface i2c if vif; i2c proxy base i2c proxy p; real Vsup = 1.8; real Vsup = 1.8; function new(string name = "i2c driver", uvm component parent); function new(string name = "i2c ms driver", uvm component parent); super.new(name, parent); super.new(name, parent); endfunction endfunction virtual task run phase(uvm phase phase); virtual task run phase(uvm phase phase); forever begin seq item port.get next item(req); i2c proxy p.push Vsup(Vsup); `uvm info(get type name(), \$sformatf("Sending Packet :\n%s", r forever begin void'(begin tr(reg, "Input I2C Packet")); seg item port.get next item(reg); `uvm info(get type name(), \$sformatf("Sending Packet :\n%s", req.sprint()), UVM LOW) vif.send to dut(.regAddr(reg.reg addr), .data(reg.data), void'(begin tr(req, "Input I2C Packet")); .id(reg.tg addr), vif.send to dut(.regAddr(reg.reg addr), .rw (req.rw )); .data(reg.data), end tr(reg); .id(reg.tg addr), `uvm info(get type name(), "Packet sent", UVM DEBUG) .rw (req.rw )); seq item port.item done(); end tr(reg); end `uvm info(get type name(), "Packet sent", UVM DEBUG) endtask seq item port.item done(); end function void connect phase(uvm phase phase); endtask if (!uvm config db#(virtual i2c if)::get(this, "", "vif", vif()) `uvm error("NOVIF", {"vif not set for: ", get full name(),".vi function void connect phase(uvm phase phase); endfunction If (:uvm config db#(virtual i2c if)::get(this, "", "vif", vif)) `uvm error("NOVIF", {"vif not set for: ", get\_full\_name(),".vif"}) function void start of simulation phase(uvm phase phase); if (!uvm config db#(i2c proxy base)::get(this, "", "i2c proxy p", i2c proxy p)) `uvm info(get type name(), "Call i2c driver", UVM HIGH); uvm error("NOPROXY", {"i2c proxy not set for: ", get full name(),".i2c proxy p"}) endfunction endfunction 36 endclass

2

3 4

5

6 7

8

9

10

11

12 13

14

15

16

17

18 19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

## $freq_adpt_tb \rightarrow freq_adpt_ms_tb$

UVM

endfunction : connect\_phase

freq\_detector.agent.monitor.item\_collected\_port.connect(freq\_adpt\_sb.sb\_osc\_det);

###

| <pre>class freq_adpt_tb extends uvm_env;</pre>                                                                                                                                          | <pre>class freq_adpt_ms_tb extends freq_adpt_tb;</pre>                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>// component macro</pre>                                                                                                                                                           | 58<br>59 // component macro                                                                                                                                                                                 |

| <pre>`uvm_component_utils(freq_adpt_tb)</pre>                                                                                                                                           | <pre>60 `uvm_component_utils(freq_adpt_ms_tb)</pre>                                                                                                                                                         |

|                                                                                                                                                                                         | 61<br>62 //freq_adpt_ms_scoreboard_freq_adpt_sb;                                                                                                                                                            |

| registers_env registers;                                                                                                                                                                | 63                                                                                                                                                                                                          |

| <pre>osc_env freq_generator;<br/>osc env freq detector;</pre>                                                                                                                           | 64 // Constructor                                                                                                                                                                                           |

| osc_env freq_detector,                                                                                                                                                                  | <pre>65 function new (string name, uvm_component parent=null);</pre>                                                                                                                                        |

| <pre>freq_adpt_scoreboard freq_adpt_sb;</pre>                                                                                                                                           | 66 super.new(name, parent);<br>67 endfunction : new                                                                                                                                                         |

|                                                                                                                                                                                         | 67 endfunction : new                                                                                                                                                                                        |

| // Constructor                                                                                                                                                                          | 69 // UVM build() phase                                                                                                                                                                                     |

| <pre>function new (string name, uvm_component parent=null);</pre>                                                                                                                       | <pre>70 function void build phase(uvm_phase phase);</pre>                                                                                                                                                   |

| <pre>super.new(name, parent); endfunction : new</pre>                                                                                                                                   | 71 `ifdef UVM AMS                                                                                                                                                                                           |

| endrunction : new                                                                                                                                                                       | 72 // set up bridge proxy pointer references to generator and detector UVCs<br>73 uvr config db #(osc bridge proxy)::set(this,"freq generator.agent.*","bridge proxy", top.generator bridge. uvm ms proxy); |

| // UVM build() phase                                                                                                                                                                    | 74 dv config db #(osc bridge proxy)::set(this, "freq detector.agent.*", "bridge proxy", top.detector bridge. dvm ms proxy",                                                                                 |

| <pre>function void build_phase(uvm_phase phase);</pre>                                                                                                                                  | 75 `endif                                                                                                                                                                                                   |

| <pre>`uvm_info("MSG","In the build phase",UVM_MEDIUM)</pre>                                                                                                                             |                                                                                                                                                                                                             |

|                                                                                                                                                                                         | <pre>77   `ifdef DMS_I2C 74    uvm config db #(uvm ms proxy)::set(this,"i2c.agent.*","i2c proxy", top.i2c bridge. uvm ms proxy);</pre>                                                                      |

| <pre>// set up virtual interfaces for UVCs and scoreboard</pre>                                                                                                                         | 79 `endif                                                                                                                                                                                                   |

| <pre>uvm_config_db#(virtual osc_if)::set(this,"freq_generator*","vif", top.generator_if);<br/>uvm_config_db#(virtual osc_if)::set(this,"freq_detector*", "vif", top.detector_if);</pre> | 80                                                                                                                                                                                                          |

| uvm_config_db#(virtual osc_if)::set(this,"req_detector*", "vir", top.detector_if);<br>uvm_config_db#(virtual registers_if)::set(this,"registers.reg_agent.*", "reg_vif", top.reg_i      | (F). 81 // override driver, monitor, and scoreboard with UVM-AM <u>S</u> versions                                                                                                                           |

| dwm_conrig_dbw(virtudtriegisters_ir).iset(tills) registersireg_dgentrw ; reg_vir ; topireg_i                                                                                            | 82 Set_type_override_by_type(12c_driver::get_type(),12c_ms_driver::get_type());                                                                                                                             |

| <pre>// config the value of diff_sel for freq_generator to 0 - single-ended clock generation</pre>                                                                                      | <pre>83 set_wpe_override_by_type(osc_transaction::get_type(),osc_ms_transaction::get_type());<br/>84 set_type_werride_by_type(osc_driver::get_type(),osc_ms_source_driver::get_type());</pre>               |

| <pre>uvm_config_int::set(this,"freq_generator.agent.*","diff_sel", 0);</pre>                                                                                                            | set type override by type(osc monitor::get type(),osc ms_source monitor::get type());                                                                                                                       |

| <pre>// config the value of diff_sel for freq_detector to 1 - differential clock detection</pre>                                                                                        | <pre>86 set_type_override_by_type(freg_adpt_scoreboard::get_type(),freq_adpt_ms_scoreboard::get_type());</pre>                                                                                              |

| <pre>uvm_config_int::set(this,"freq_detector.agent.*","diff_sel", 1);</pre>                                                                                                             | 87                                                                                                                                                                                                          |

| <pre>super.build_phase(phase);</pre>                                                                                                                                                    | <pre>88 super.build_phase(phase); 89</pre>                                                                                                                                                                  |

| super.bulto_phase(phase);                                                                                                                                                               | 90 endfunction                                                                                                                                                                                              |

| // create the envs for the generator, detector, registers and scoreboard                                                                                                                | 91                                                                                                                                                                                                          |

| <pre>freq_generator = osc_env::type_id::create("freq_generator", this);</pre>                                                                                                           | 92 endclass : freq_adpt_ms_tb                                                                                                                                                                               |

| <pre>freq_detector = osc_env::type_id::create("freq_detector", this);</pre>                                                                                                             |                                                                                                                                                                                                             |

| <pre>registers = registers_env::type_id::create("registers", this);</pre>                                                                                                               |                                                                                                                                                                                                             |

| <pre>freq_adpt_sb = freq_adpt_scoreboard::type_id::create("freq_adpt_sb", this);</pre>                                                                                                  |                                                                                                                                                                                                             |

| endfunction : build phase                                                                                                                                                               |                                                                                                                                                                                                             |

| endranector r bazte_pridot                                                                                                                                                              |                                                                                                                                                                                                             |

| // UVM connect_phase                                                                                                                                                                    |                                                                                                                                                                                                             |

| <pre>function void connect_phase(uvm_phase phase);</pre>                                                                                                                                | (accellera)                                                                                                                                                                                                 |

| // Connect the TLM ports from the UVCs to the scoreboard                                                                                                                                |                                                                                                                                                                                                             |

| <pre>registers.reg_agent.monitor.item_collected_port.connect(freq_adpt_sb.sb_registers_in);</pre>                                                                                       |                                                                                                                                                                                                             |

| <pre>freq_generator.agent.monitor.item_collected_port.connect(freq_adpt_sb.sb_osc_gen);</pre>                                                                                           | SYSTEMS INITIATIVE                                                                                                                                                                                          |

## Demo

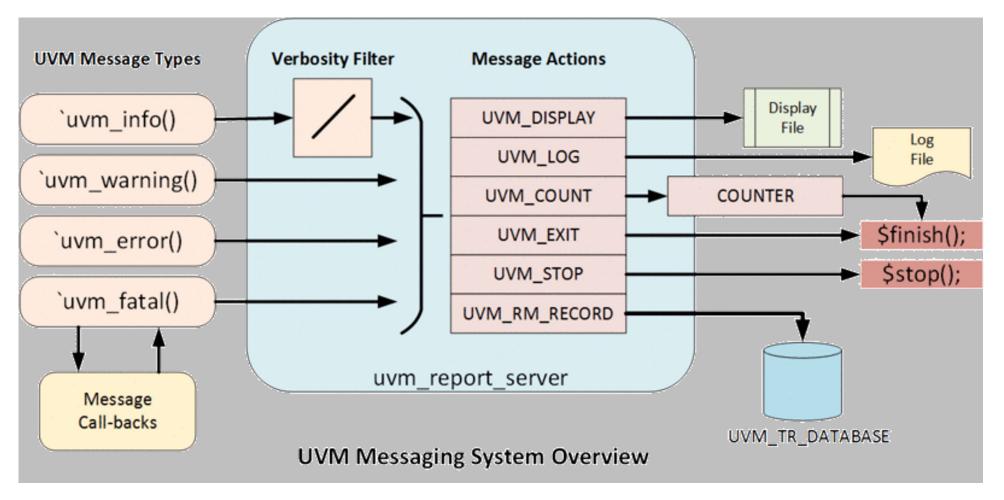

# UVM Messaging

## Messages for Debug and Error Reporting

- Debugging activity inside a large environment with many UVCs is critical

- Need to report:

- Errors

- Debug

- Progress

- Messages need to be categorized via severity:

- Fatal, Error, Warning, Info

- Need to link actions with messages

- Stop simulation on fatal or after four errors

- Summarize number of messages reported

- Need a different mechanism than simulator messages to avoid filtering effects

### UVM Messaging System

### UVM Messaging from Analog Resource

- UVM Reporting macros not supported in Verilog-AMS modules

- Take advantage of up-scoping to access SV bridge

- `include ``uvm\_ms.vamsh" in Verilog-AMS analog resource or `include ``uvm\_ms.vdmsh" in SystemVerilog analog resource

- localparams to define UVM Verbosity levels as integers to match UVM enum

- Macros to wrap the <code>uvm\_ms\_\*</code> reporting function calls defined in <code>uvm\_ms.svh</code>

- `include ``uvm\_ms.svh" in MS Bridge (SV)

- Definitions of the functions called by analog resource

- Provides macros for `uvm\_ms\_[info|warning|error|fatal] (...)

- Utilizes the <u>"\_uvm\_ms\_proxy</u>" declaration as the originating path for analog resource UVM messages

### UVM Messaging Example for Verilog-AMS Resource

- Use analog domain to detect the issue and toggle a flag

- Flag is detected by absdelta to then report the message via the digital engine

- Example

```

analog begin

if((I_PLUS > 1.0) && !I_thr_triggered) I_thr_triggered = 1;

else if(I_PLUS < 0.9) I_thr_triggered = 0;

end

//Convert the detection in the analog block to a UVM report.

string message;

always@(absdelta(I_thr_triggered,1,0,0,1)) begin

$sformat(message,"The Current is above the thresholds @ %e",I_PLUS);

if(I_thr_triggered) `uvm_ms_error(P_TYPE,message)

end

```

45

### UVM Message – Analog block

`uvm\_ms\_info("FREQ\_UPDATE",\$sformatf("freq=%e Hz period=%e ns", freq\_in, out\_period),\ UVM\_MEDIUM)

### "uvm\_ms.svh"

function void uvm\_ms\_info(id,message,uvm\_verbosity,uvm\_path, `\_\_FILE\_\_, `\_\_LINE\_\_);

uvm component CTXT;

CTXT=uvm\_ms\_get\_bridge\_path(uvm\_path); // get path to uvm\_component in top.bridge CTXT.uvm\_report\_info(id,message,uvm\_verbosity'(verbosity\_level),file,line);

endfunction: uvm\_info

### osc\_bridge.sv

`include "uvm\_ms.svh"

`uvm\_ms\_reporter // instantiates uvm\_ms\_reporter component to be used with messaging

UVM\_INFO ../uvc\_lib/osc/vams/osc\_bridge\_core.vams(98) @ 52001.098068ns: top.detector\_bridge [FREQ\_UPDATE] The Current is above the threshold @ 1.178812e+00A

### Conclusion

- There is a need for more advanced, standard methodologies for scalable, reusable and metric-driven mixed-signal (AMS/DMS) verification

- The UVM-AMS WG proposal addresses the gaps in current verification methodology standards

- Extend UVM class-based approach to seamlessly support the modulebased approach (MS Bridge) needed for mixed-signal verification

- Targeting analog/mixed-signal contents (RNM, electrical/SPICE)

- Application and extension of existing UVM concepts and components

- Sequencer, Driver, Monitor

- MS Bridge / Analog resources

- UVM Messaging System

## Questions?