Expediting the Code Coverage Closure Using Static Formal Techniques – A Proven Approach at Block and SoC Levels

Questa Formal team and friends

2015 DVCon India D1A2.1-DV

# Agenda

### Introduction

- Coverage Backgrounder

- Targeting Unreachable Coverage with Formal

- Reaching Coverage Closure Faster

- Conclusion

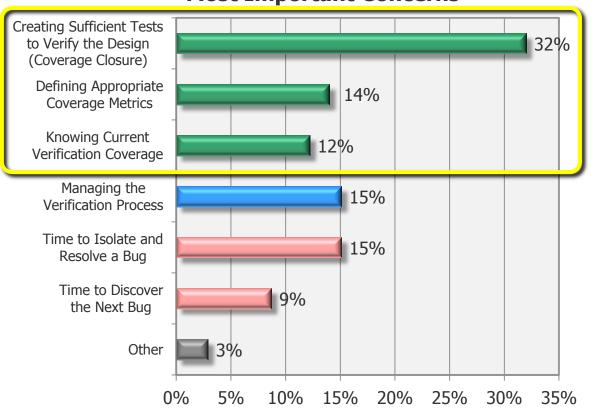

# **Functional Verification Challenges**

Coverage Ranks at the Top of Project Management's Concerns

#### Most Important Concerns

Source: Wilson Research Group and Mentor Graphics, 2014 Functional Verification Study

© Mentor Graphics Corp. Company Confidential **www.mentor.com**

Wilson Research Group 2010 Functional Verification Study

### Industry Trends: ASIC D&V Use of Code Coverage

Source: Wilson Research Group and Mentor Graphics, 2014 Functional Verification Study

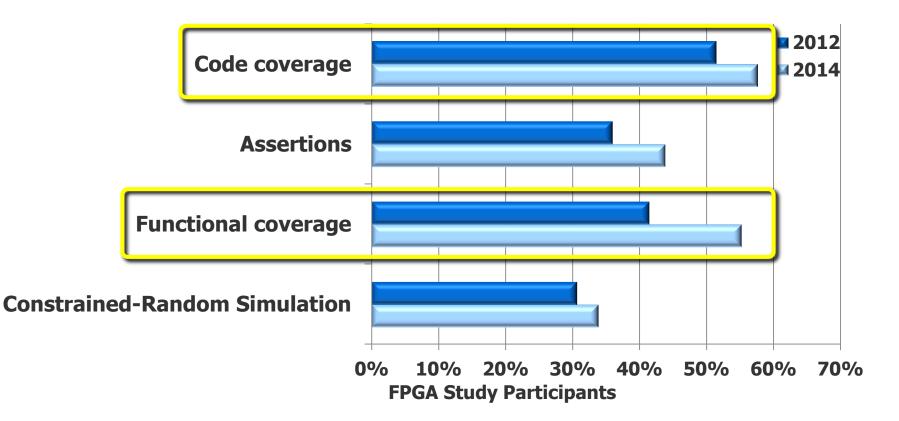

## **FPGA** Verification Technique Trends

Source: Wilson Research Group and Mentor Graphics, 2014 Functional Verification Study

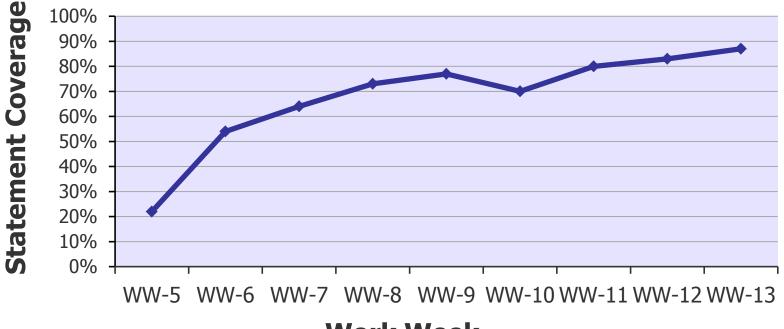

# **Code Coverage Challenge**

Are we there yet?

#### Work Week

Data & graph from 2011 customer paper

- ✓ 270 man weeks to do coverage waiver analysis for one design

- 180 man weeks to write missing tests

- That's almost 9 man-years!

### **Verification Management Challenge**

# What You Will Learn Today

- Primer on coverage types and how coverage is recorded

- How to rapidly identify "unreachable" coverage areas

- How to reach your coverage goals faster

# Agenda

### Introduction

- Coverage Backgrounder

- Targeting Unreachable Coverage with Formal

- Reaching Coverage Closure Faster

- Conclusion

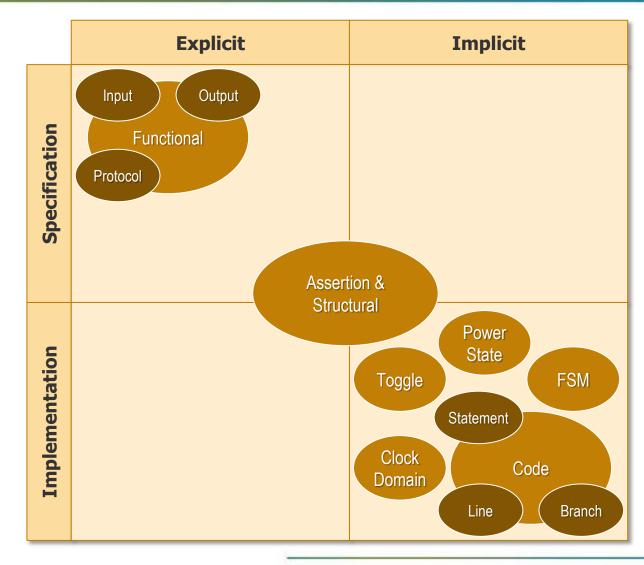

# **Types of Coverage**

- Origin of Source

- Specification

- Implementation

- Method of Creation

- Explicit

- Implicit

- Both are Required

- Functional

- Structural

# **Coverage: Implementation**

What areas of the design have been touched by verification

### Code Coverage

- Did these lines/branches of code get exercised?

- Automated in the simulation environment

- One of the basic design verification signoff metrics

- A basic measure with little correlation to functionality

### FSM Coverage

- Did all the states and transitions get exercised?

- Automated in the simulation environment

- One of the basic design verification signoff metrics

- Typically included with code coverage

## **Code Coverage: Statement (s)**

Counts the execution of each statement on a line

— Even if multiple statements

Example:

| always @(posedge                           | clk or | negedge | rstn) 🗲 | -                            |  |  |

|--------------------------------------------|--------|---------|---------|------------------------------|--|--|

| •••                                        |        |         |         |                              |  |  |

| reg <= dat;                                | I      |         |         | the statements the number of |  |  |

| C <= A && B;                               | I      |         | times   | each one is hit              |  |  |

| Report style based on number of Statements |        |         |         |                              |  |  |

| Enabled Coverage                           | Active | e Hits  | Misses  | % Covered                    |  |  |

|                                            |        | ·       |         |                              |  |  |

| Stmts                                      | 415    | 387     | 28      | 93.2                         |  |  |

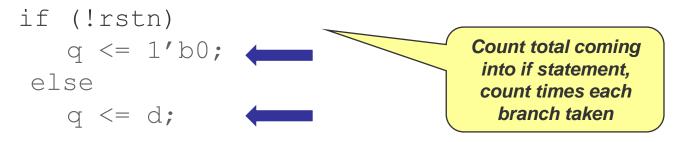

# Code Coverage: Branch (b)

- Counts the execution of each conditional "if/then/else" and case statement

- All true and false branches are considered

- Each (if/else if/else | case) element counts as a branch

- Example (if statement):

Report style based on number of Branches

| Enabled Coverage | Active | Hits | Misses % Covered |

|------------------|--------|------|------------------|

|                  |        |      |                  |

| Branches         | 47     | 45   | 2 95.7           |

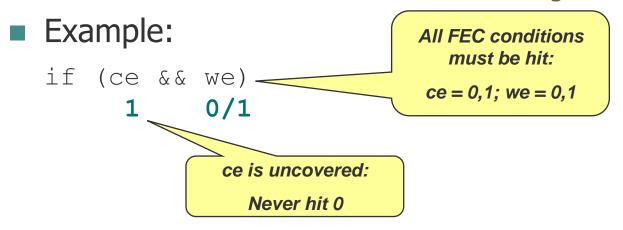

# **Code Coverage: Condition (c)**

Analyzes the decision made in "if" and ternary statements

— Considered extension of branch coverage

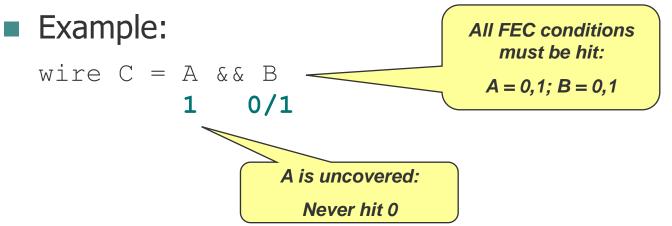

Report style based on Focused Expression Coverage

| Enabled Coverage    | Active | Hits | Misses | % Covered |

|---------------------|--------|------|--------|-----------|

|                     |        |      |        |           |

| FEC Condition Terms | 16     | 13   | 3      | 81.2      |

# **Code Coverage: Expression (e)**

Analyzes expressions on the right hand side of an assignment

Report style based on Focused Expression Coverage

| Enabled Coverage    | Active | Hits | Misses | % Covered |

|---------------------|--------|------|--------|-----------|

|                     |        |      |        |           |

| FEC Condition Terms | 25     | 14   | 11     | 56.0      |

15

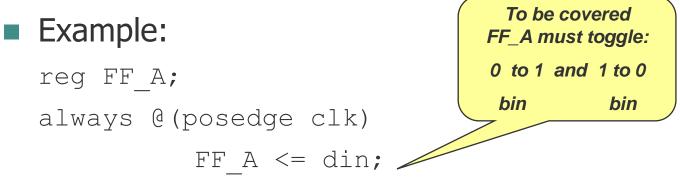

# Code Coverage: Toggle (t)

Counts each time a logic node transitions one state to another

### Report style based on Toggle Bins

| Enabled Coverage | Active | Hits | Misses | % Covered |

|------------------|--------|------|--------|-----------|

|                  |        |      |        |           |

| Toggle Bins      | 356    | 351  | 5      | 98.5      |

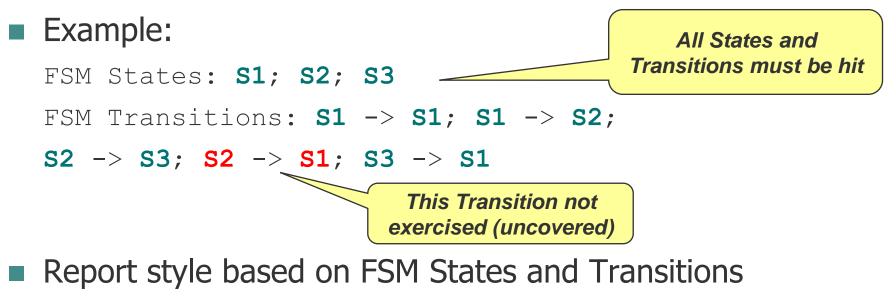

# Code Coverage: FSM (f)

Counts the states and transitions of a FSM

| Enabled Coverage | Active | Hits | Misses | % Covered |

|------------------|--------|------|--------|-----------|

|                  |        |      |        |           |

| States           | 3      | 3    | 0      | 100.0     |

| Transitions      | 5      | 4    | 1      | 80.0      |

### **Coverage: Structural**

How much verification has stressed the design

#### Assertion Coverage

- How many times did the assertion get evaluated, pass, fail

- Automated in the simulation environment

- Doesn't answer the questions:

- Is the assertion implemented correctly? (check anything of value)

- Are there enough assertions?

### Structural Coverage

- Measures corner case type activity

- How many times was my FIFO empty, full, hit high water mark

- Implementation specific, can be automated with assertions

- How well is the TB environment stressing the design?

### **Cover Statements/Properties**

Properties and Sequences can be "covered"

Useful for checking temporal behavior of your design

- SVA/PSL designed for describing temporal behavior

- Cover statements typically target a sequence of events

- Can also target single cycle events

- Simulation will count the number of occurances

- Formal will tell you if it's reachable or unreachable

#### Examples:

cov\_sm\_trans: cover property (@(posedge clk) cstate == TRANS ); cov\_ddr\_wr: cover property (@(posedge clk) ddr\_act ##[1:20] ddr\_wr); sequence apb\_wr;

pselx && pwrite && !penable ##1 pselx && pwrite && penable; endsequence

```

cov_b2b_wr: cover property (@(posedge clk) apb_wr ##1 apb_wr);

cov_seq: cover property (@(posedge clk) a ##2 b ##[1:3] c[*4] ##1 a );

```

## **Coverage: Functional**

What features of the design have been tested

### Transactional Coverage

- Measures interface type transactions

- Have I covered all my AHB/AXI transactions?

- Typically implemented with cover groups/points

- Often used with complex TB environments (TLA, CR, iTBA)

### Functional Coverage

- Measures occurrence of functional events

- Did my design do back-to-back writes?

- Typically implemented with cover groups and cover directives

- Used in complex TB environments, correlate function to spec

20

# **Functional Coverage**

- Must be specified by the user and cannot be automatically inferred from design

- Validates actual functionality

- Formal specification of verification plan

Direct correlation between requirements and verification

- Measures verification completeness against specification

- Have I verified all functional requirements?

- Have I covered the entire verification plan?

- Are my tests adding values to my verification goal?

- Have I exercised all corner cases in my design?

- Am I done?

- Counts how many times "interesting" things occur

### CoverGroups

#### System Verilog CoverGroups

- coverpoints and coverbins used to categorize/display data

- Must be instantiated

#### ■ Example: CG in module module cover\_pci\_master32\_sm ( input clk\_in, input [3:0] cur\_state); covergroup cg\_cur\_state @ (posedge clk\_in); cp: coverpoint cur\_state { bins s\_idle = {1}; bins s\_tran = {4}; bins s\_end = {8}; endgroup : cg\_cur\_state; cg\_cur\_state cg\_cur\_state\_inst = new; endmodule

## **CoverGroups Example: FSM, Arbiters**

```

covergroup cg cstate @ (posedge clk);

cp: coverpoint cstate {

bins s valid [5] = {1,2,4,8,16};

bins s illegal = {0,3,5,6,7,[9:15]}; }

endgroup : cg cstate;

cg cstate cg cstate inst = new;

Ŧ

G

wire [1:0] enables = {wr en,rd en};

wire en = $changed(enables);

req len;

always @*

if (!clk) len <= en;</pre>

wire gclk = clk & len;

covergroup cg enables @ (posedge gclk);

cp: coverpoint enables {

bins reads = \{1\};

bins writes = \{2\};

illegal bins bad = {3};

bins idle = default; }

endgroup : cg enables;

cg enables cg enables inst = new;

```

| 🔀 Covergroups 🖂 🚽 👘       |          |      |           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|----------|------|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                      | Coverage | Goal | % of Goal | Status | Inc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                           |          |      |           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🚊 🧾 TYPE cg_cstate        | 83.3%    | 100  | 83.3%     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🗊 🗾 CVP cg_cstate::cp     | 83.3%    | 100  | 83.3%     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🚊 🗾 💵 Vtb_axi4lite_2_ap   | 83.3%    | 100  | 83.3%     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🚊 🗾 СVР ср                | 83.3%    | 100  | 83.3%     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B bin s_valid[0]          | 189      | 1    | 100.0%    |        | _√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B bin s_valid[1]          | 7        | 1    | 100.0%    |        | _√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B bin s_valid[2]          | 8        | 1    | 100.0%    |        | -√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B bin s_valid[3]          | 8        | 1    | 100.0%    |        | _√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B bin s_valid[4]          | 8        | 1    | 100.0%    |        | -√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 🔤 <b>bin</b> s_illegal    | 0        | 1    | 0.0%      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 🚊 🛒 TYPE cg_enables       | 100.0%   | 100  | 100.0%    |        | -√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 🛓 🗾 CVP cg_enables::arb   | 100.0%   | 100  | 100.0%    |        | _√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 🚊 🗾 💵 Vtb_axi4lite_2_ap   | 100.0%   | 100  | 100.0%    |        | _√                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 🚊 🛒 CVP arb               | 100.0%   | 100  | 100.0%    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B illegal_bin bad         | 0        | -    | -         |        | <ul> <li>Image: A second s</li></ul> |

| B bin reads               | 8        | 1    | 100.0%    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 📲 🕒 bin writes            | 8        | 1    | 100.0%    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>B</b> default bin idle | 17       | -    | -         |        | - 🗸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### **Coverage: Metrics**

- Basic: Code/FSM/Assertion Coverage

- Checks that all RTL has been exercised

- All assertions have been exercised

- Semi-Automated: Transaction/Structural Coverage

- Checks that all types of transactions have occurred

- Ensures that the tests have sufficiently stressed the design

- Advanced: Functional Coverage

- Checks that all the requirements for the design have been tested

- Does the design work in all scenarios?

- All these coverage types are measured and tracked to determine when verification is complete and the chip can tape out

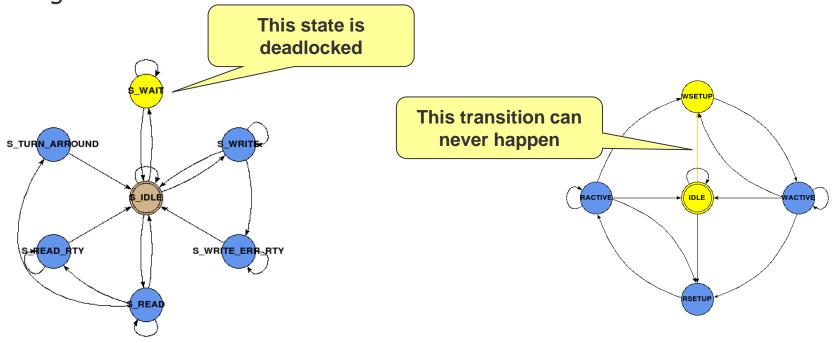

## **Coverage: Metric Holes**

- Code/FSM/Assertion Coverage

- Functional dead code and unreachable FSM states/transitions

- Modes of the design that create dead code

- Time can be wasted trying to hit these holes!

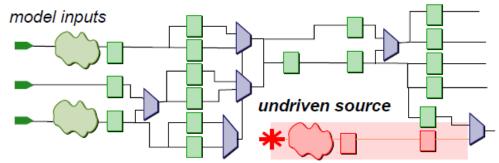

- Transaction/Structural Coverage

- TB doesn't stress the design enough

- Incomplete models don't exercise all transactions

- Functional Coverage

- Incomplete spec or planning, lack of knowledge/time

- Proper test planning can mitigate some of these challenges

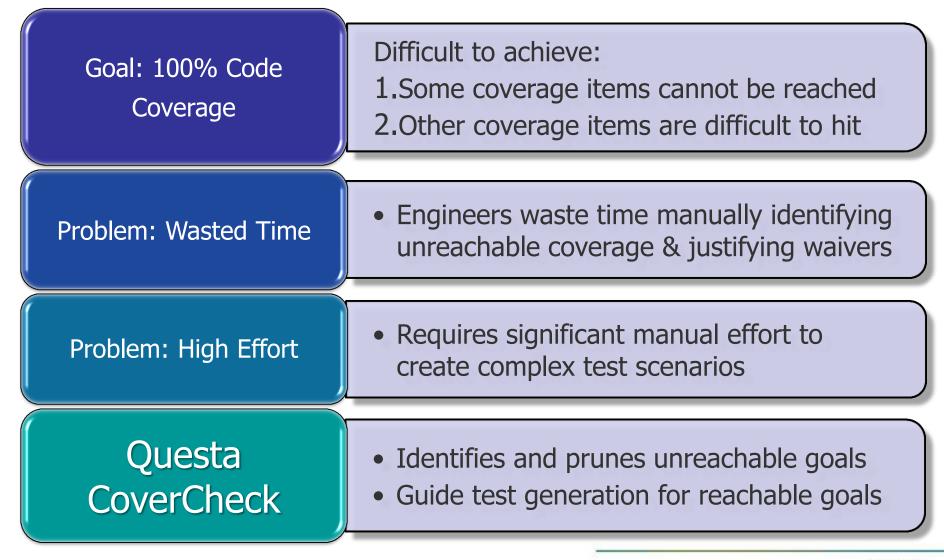

- Making use of automated formal techniques such as Questa CoverCheck can minimize time to closure

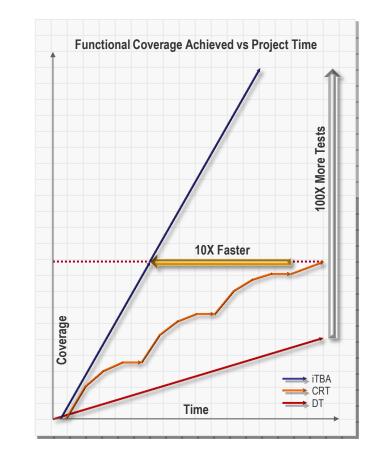

# **Common Methods to Achieve Coverage**

#### Directed Tests

- Can target specific areas

- Less setup typically

#### Constrained Random Tests

- More sophisticated setup

- More automated to coverage

#### Intelligent Testbench Automation

- >10X Faster Coverage Than CRT

- >100X More Tests Than DT

#### Goals

- Achieve total coverage faster

- With fewer resources

- In less time

# **Typical Coverage Closure Methods**

- Fix design issues that prevent code coverage from being achieved

- Run more vectors to hit missing code coverage

- Directed tests

- Constrained random

- Intelligent test bench generation

- Spend a lot of time analyzing and applying new vectors

- Apply formal methods to determine coverage reachability

- Add exclusions by hand

- Sometimes the simulator can add automated exclusions

- Use an automated flow to generate exclusions for unreachable coverage elements

## **Coverage Backgrounder Summary**

- There is no "silver bullet" structural and functional coverage methodology or metric

- Multifaceted simulation and formal-based automation, guided by the D&V engineer's judgment, is required

# Agenda

### Introduction

- Coverage Backgrounder

- Targeting Unreachable Coverage with Formal

- Reaching Coverage Closure Faster

- Conclusion

### **Coverage Closure Challenges**

Today coverage-driven verification is a well established methodology

Question: What if certain parts of the design simply cannot be reached?

Answer: You will run extra constrained-random tests to try to cover these parts

### This can lead to a lot of wasted effort!

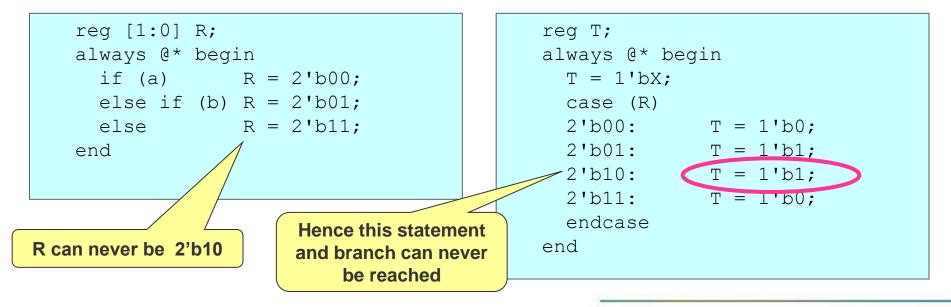

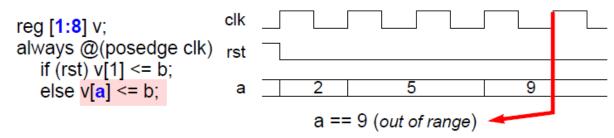

# **Example: Branch/Statement Coverage**

- Dead code easily slips into the design

Especially after changes are made

- Dead code often identifies incorrect assumptions

- Leading to critical bugs due to differing interpretation of design requirements

- Possibly synthesizes into logic that is not needed

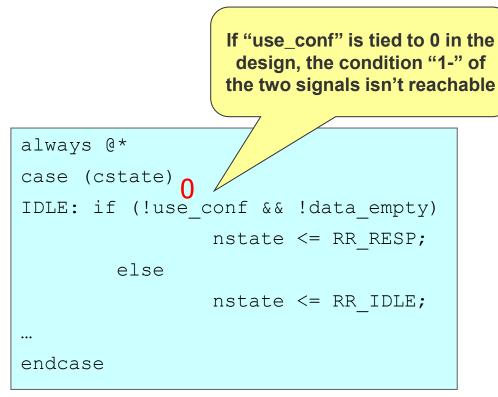

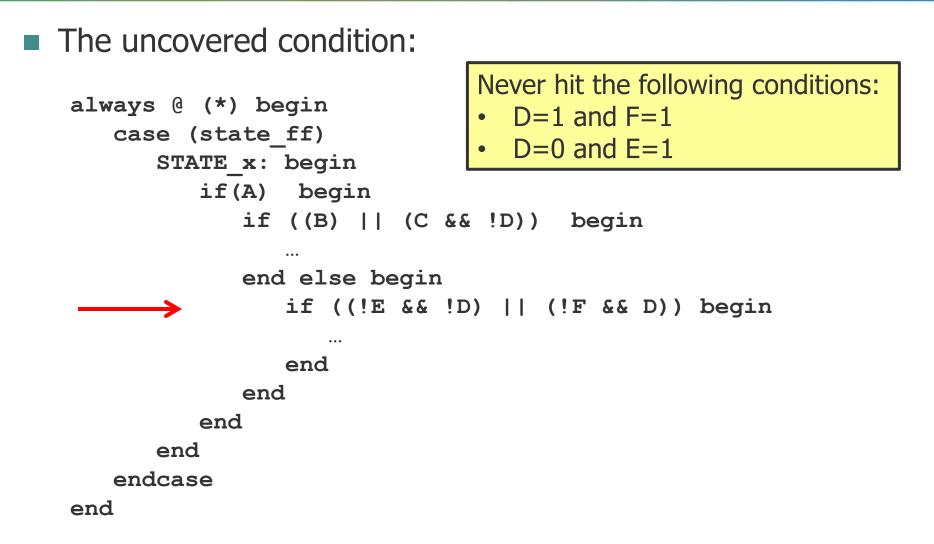

# **Example: Condition/Expression Coverage**

Design configuration can have a large impact here

- Has every combination of signals been exercised?

- Is every combination of signals possible?

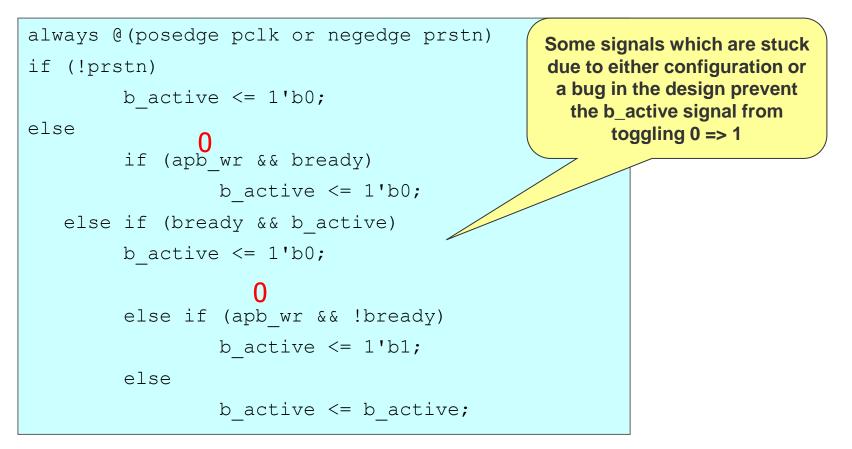

# **Example: Toggle Coverage**

Typically registers and signals can't toggle due to configuration or some other constraint/bug in the design

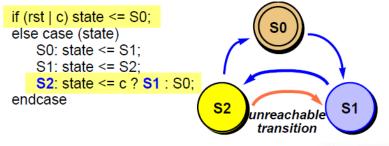

# **Example: FSM Coverage**

- Indicates an over specified state machine

May lead to unused logic

- Easily overlooked in simulation

- Info is passed to simulation for exclusion in the set of coverage goals

## **Traditional Coverage Closure**

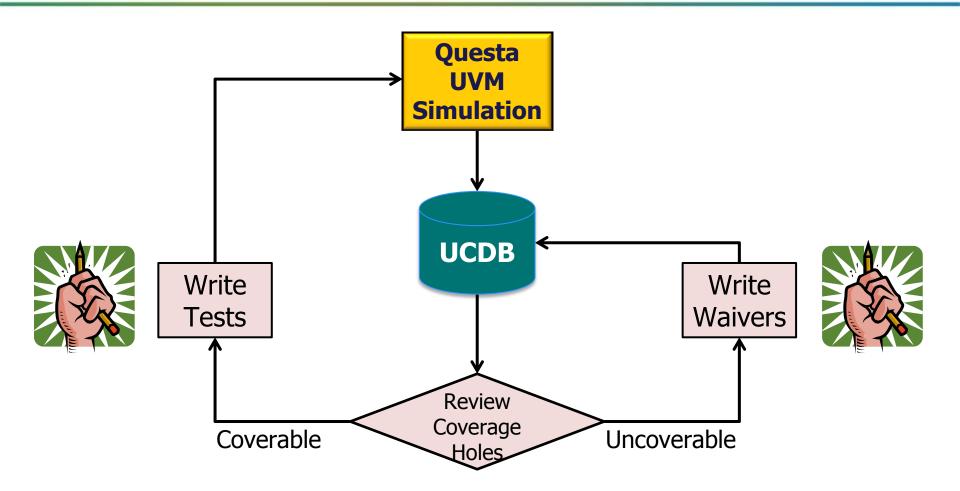

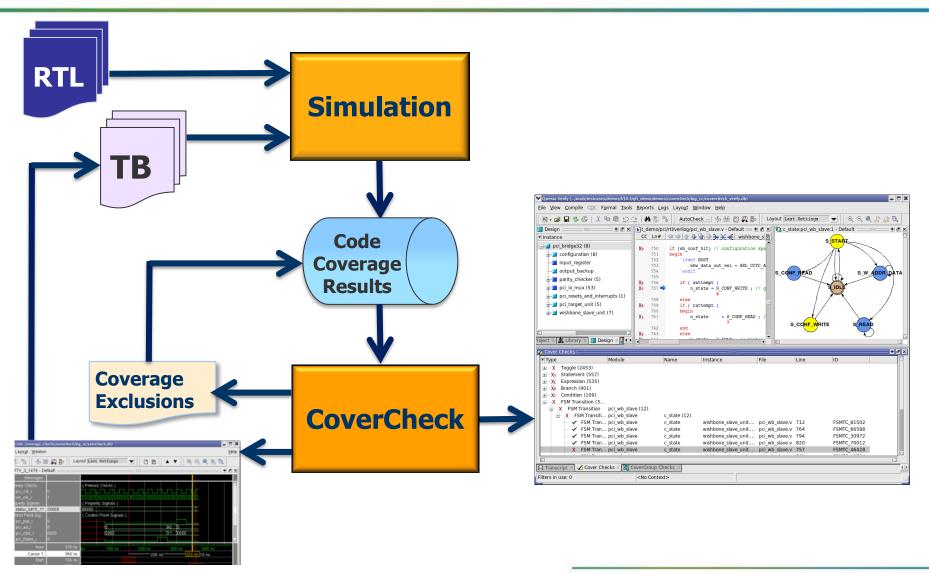

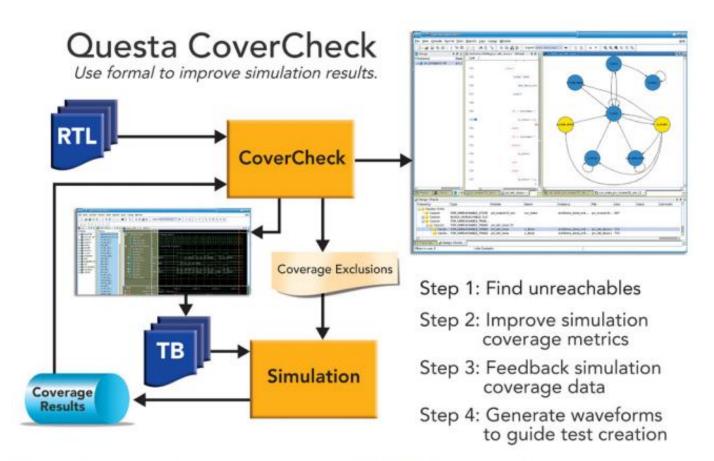

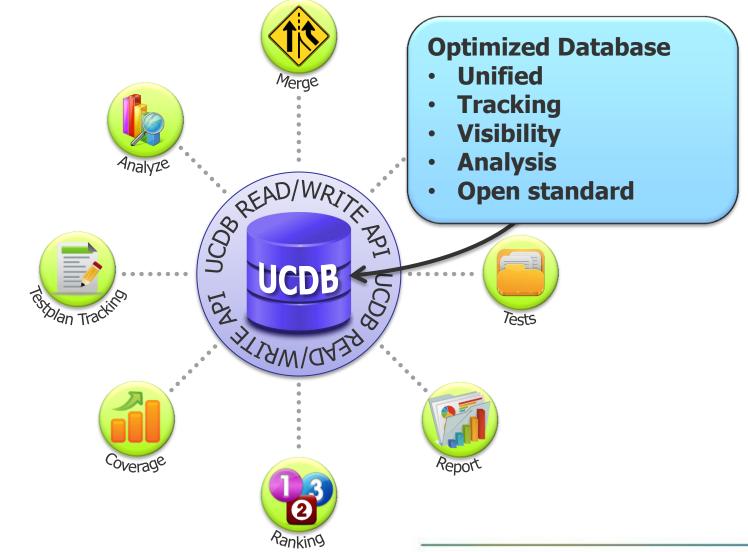

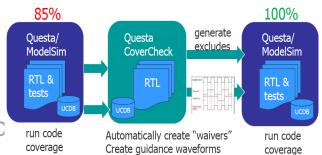

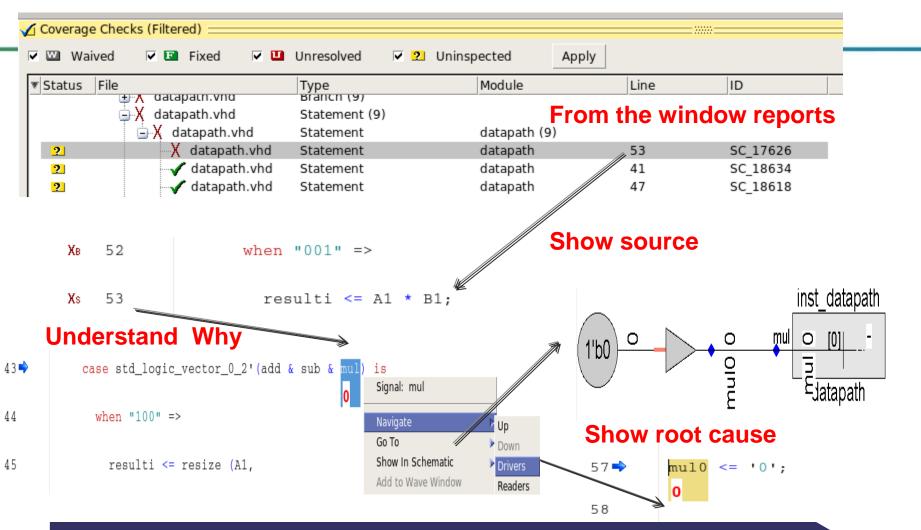

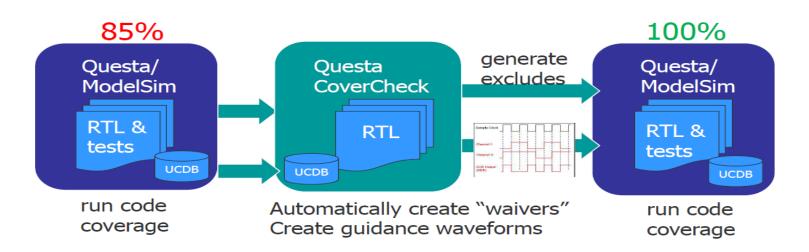

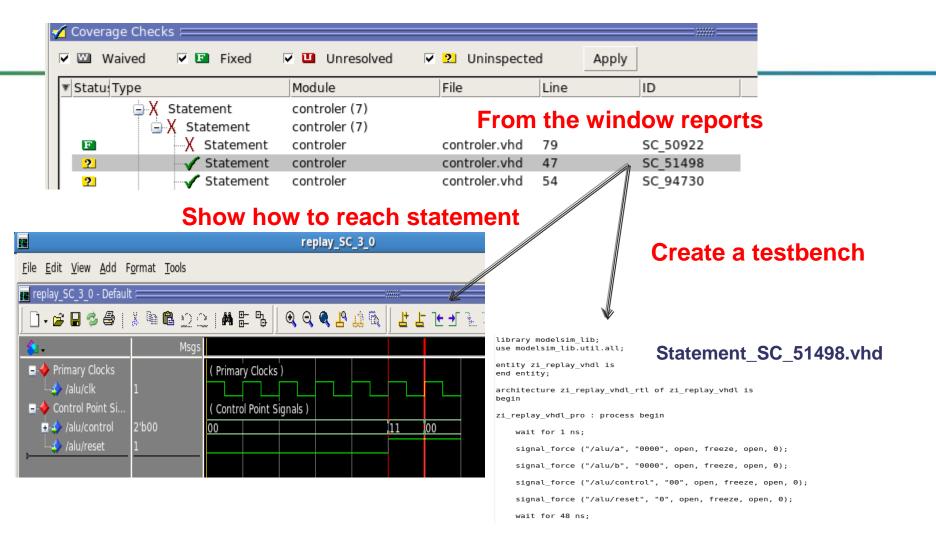

# **Questa CoverCheck**

Automatic code coverage enhancement solution

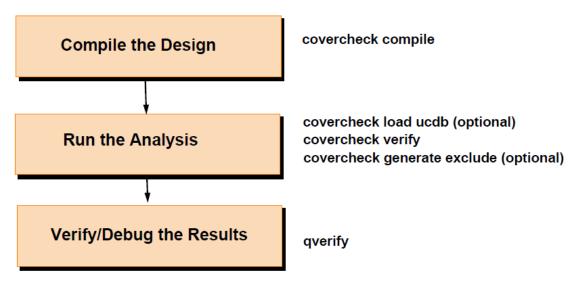

#### The Questa CoverCheck Methodology

#### No more is time wasted to try to cover unreachable code

38 Code Coverage Closure Tutorial, DVCon 2015

© Mentor Graphics Corp. Company Confidential **www.mentor.com**

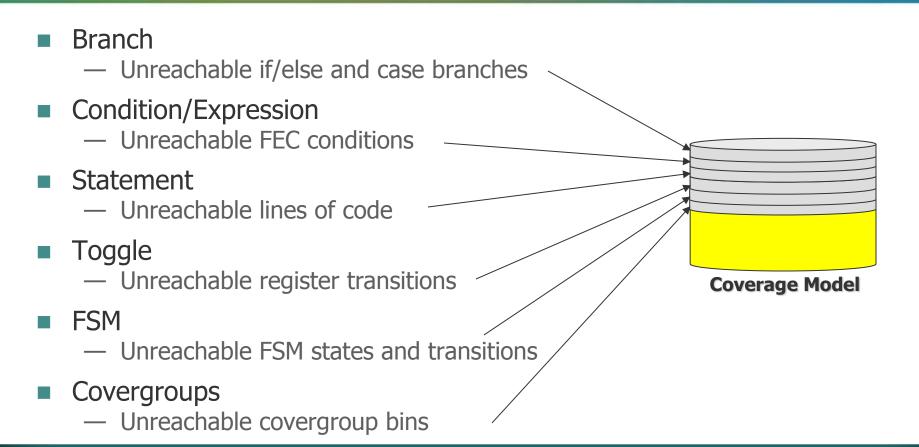

### **Checks for Coverage Exclusions**

# Unreachable items are automatically excluded from your coverage model

#### **The Coverage Improvement Process**

- 1. Generate Final UCDB file from simulations

- 2. Run Questa CoverCheck reading final UCDB

- Target uncovered code coverage elements

- Run major blocks

- 3. Generate the exclude file

- 4. Apply exclusions to your simulation results

Update existing .ucdb file with exclude file

- 5. Report coverage

- Track and manage coverage data

#### **Questa CoverCheck Verification Flow**

Use static analysis to improve simulation results!

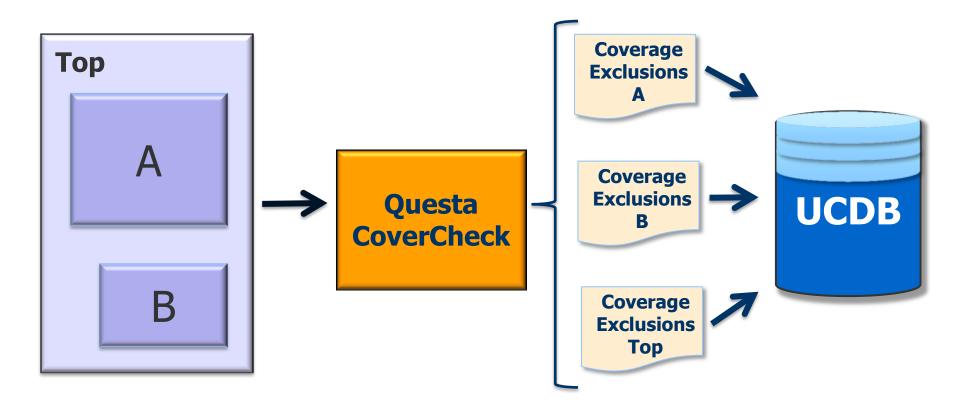

#### **Scaling Unreachable Analysis to the SoC Level**

#### **Improved Code Coverage Scores**

| istance Coverage :==================================== | Stmt count | Stmts hit | Stmt % | Stmt graph | Toggle nodes | Toggles hit | Toggle % | Toggle graph | States 호 States hi | t State % | State graph       |

|--------------------------------------------------------|------------|-----------|--------|------------|--------------|-------------|----------|--------------|--------------------|-----------|-------------------|

| /SYSTEM/bridge32_top/bridge/wishbone                   | 130        | ) 98      | 75.49  | 6          | 111          | 646         | 57.9%    |              | ] 9                | 3 33.3    | %                 |

| /SYSTEM/bridge32_top/bridge/i_pci_targ                 | . 397      | , 111     | 289    |            | 78           | i 9         | 1.15%    |              | 7                  | 1 14.3    | %_ <mark>_</mark> |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 58         | 3 56      | 96.69  | 6          | 621          | 508         | 81.2%    |              | 4                  | 4 🔵 100'  | %                 |

| /SYSTEM/bridge32_top/bridge/i_pci_targ                 | . 72       | 2 67      | 93.19  | 6          | 57           | ) 497       | 87.2%    |              | ] 3                | 3 100     | %                 |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | <b></b> i    | 3 3         | 37.5%    |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 2          | 2 2       | 100%   | 6          | 144          | 46          | 31.9%    |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 2          | 2 2       | 1009   | 6          | 144          | 49          | 34%      |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 1009   | 6          | 39;          | 2 117       | 29.8%    |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 1005   | 0          | 1            | ) 8         | 80%      |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | -            | 8 8         | 100%     |              | 8                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | 1            | ) 6         | 60%      |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | -            | 36          | 75%      |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | 1            | ) 8         | 80%      |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | 1            | ) 8         | 80%      |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | 1            | ) 8         | 80%      |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 1          | 1         | 100%   | 6          | -            | 3 8         | 100%     |              | 8                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 107        | 7 102     | 95.33  | 6          | 112          | 6 717       | 63.7%    |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 4          | 4         | 100%   | 6          | 43           | ) 246       | 56.4%    |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | 21           | ) 19        | 95%      |              | 0                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | 21           | ) 19        | 95%      |              | 0                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 32         | 2 32      | 100%   | 6          | 14           | 6 140       | 95.9%    |              | 0                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 4          | 4         | 100%   | 6          | 43           | 3 222       | 50.9%    |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | 21           | ) 19        | 95%      |              | 0                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 24         | L 21      | 87.5%  | 6          | 11           | ) 106       | 96.4%    |              | 0                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | 1            | ) 15        | 93.8%    |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 18         | ) 18      | 1009   | 6          | 80           | ) 717       | 89%      |              | ]                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 2          | 2 2       | 1009   | 6          | I) 71        | ) 3         | 4.29%    |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 1009   | 6          |              | 3 3         | 50%      |              | ן                  |           |                   |

| /SYSTEM/bridge32_top/bridge/wishbone                   | 3          | 3 3       | 100%   | 6          | <b>_</b>     | ) 3         | 50%      |              | ן                  |           |                   |

|                                                        |            |           |        |            |              |             |          |              |                    |           |                   |

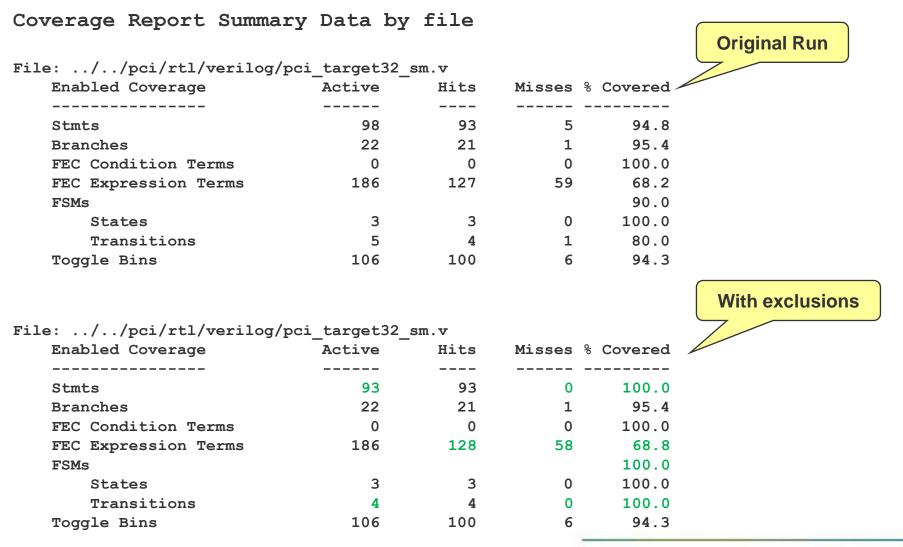

#### **Simulation Coverage Before/After Exclusions**

#### **CoverGroup Coverage Before/After Exclusion**

Coverage Report Summary

TOTAL COVERGROUP COVERAGE: 28.18 COVERGROUP TYPES: 4

TOTAL ASSERTION COVERAGE: 80.0% ASSERTIONS: 5

Total Coverage By File (code coverage only, filtered view): 39.1%

TOTAL COVERGROUP COVERAGE: 48.2% COVERGROUP TYPES: 4

TOTAL ASSERTION COVERAGE: 80.0% ASSERTIONS: 5

Total Coverage By File (code coverage only, filtered view): 42.3%

**Original Run**

With exclusions

## **Calculating Your ROI from Using CoverCheck**

- Calculating the amount of time saved in your coverage closure flow by using CoverCheck is fairly easy:

- N = the number of unreachable coverage elements

- T = the time it would have taken you to manually analyze it

- ROI = total amount of time saved automating your exclusion flow

ROI = N x T

- Example: In one of the above examples there were over 3000 unreachable coverage elements in the design

- Let's be generous and estimate it would have taken 15 minutes on average to analyze each unreachable item and exclude it

- ROI = 3000 X 15 min

- ROI = 45000 min (750 hr)

- ROI = ~4.5 man months of effort saved

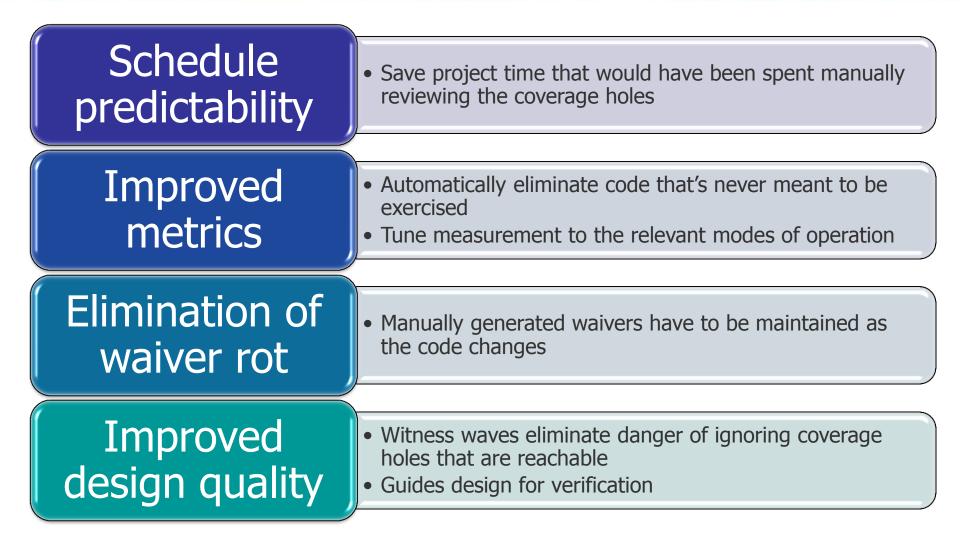

#### **Summary: CoverCheck Benefits**

## Using Questa CoverCheck To Speed Up RTL Freeze of PCIe IP

Sundararajan Haran Engineering Manager Microsemi

## **Section Agenda**

- Questa Covercheck

- PCIe evaluation bench approach

- Results

- Benefits

- References

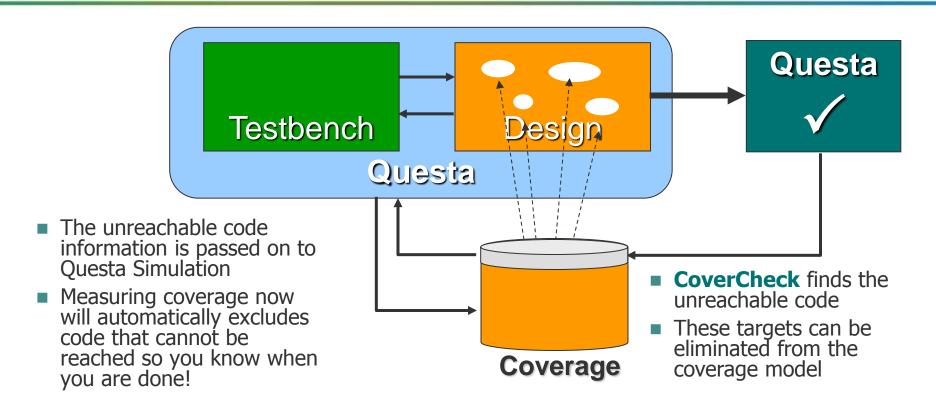

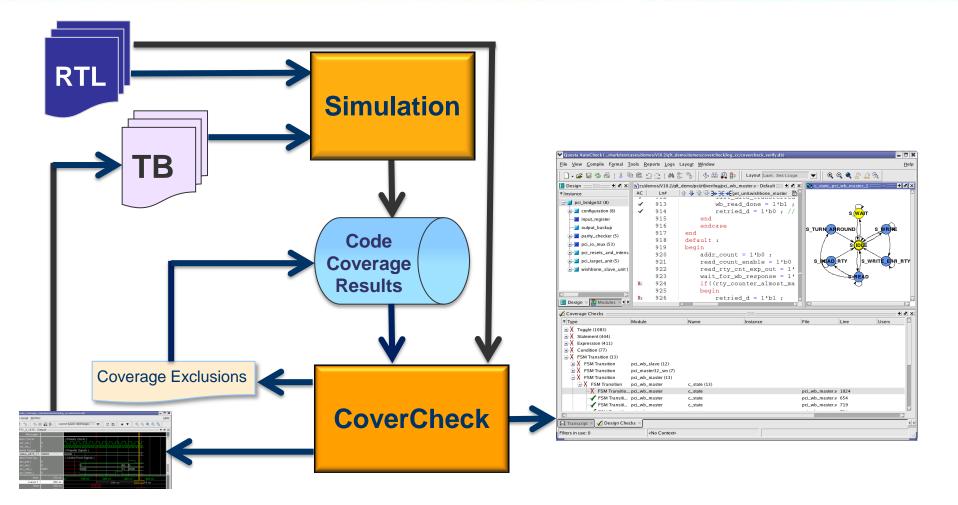

#### **Questa CoverCheck Details**

- CoverCheck analyzes coverage items that are found to be:

- Unreachable through simulation using a QuestaSim Universal Coverage Database (UCDB)

- Or through a formal analysis

- CoverCheck can run without a simulation UCDB

- App automatically runs formal analysis on the entire design to determine and analyze the unreachable items

- Downside: this takes a long time (several hours).

#### **Out-of-the-Box CoverCheck Flow**

Questa CoverCheck methodology. The tool applies formal methods to target code that's unreached by the simulator.

#### **Section Agenda**

- Questa Covercheck

- PCIe evaluation bench approach

- Results

- Benefits

- References

#### **PCIe Evaluation Bench Approach**

- We used PCIe block level environments for this exercise

- CoverCheck was chosen and used at the block level

### **Section Agenda**

- Questa Covercheck

- PCIe evaluation bench approach

- Benefits

- References

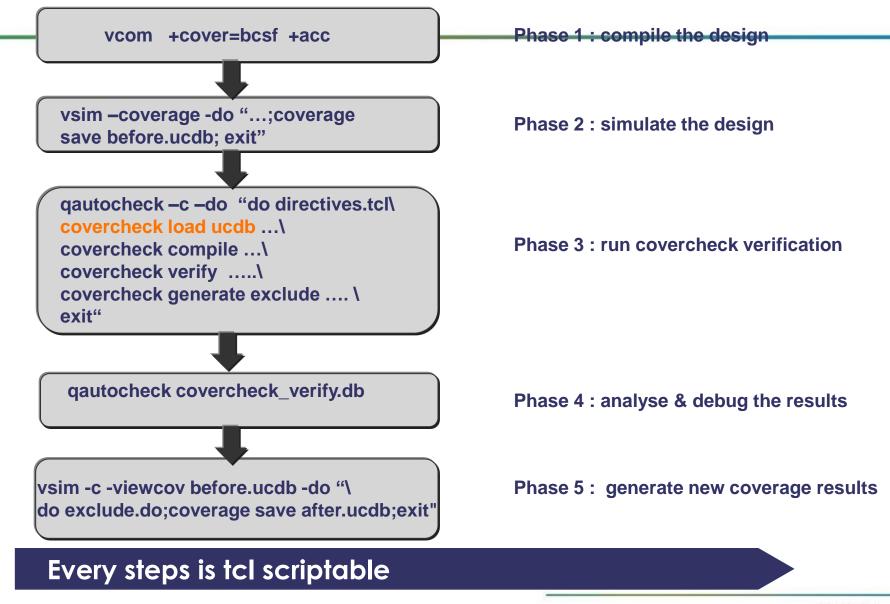

#### **CoverCheck was run on the final merged coverage database of PCIe block**

| ▼ qautocheck_cmds.tcl (/verifyESS/trunk/main/scripts) - GVIM7                                      |

|----------------------------------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit <u>T</u> ools <u>S</u> yntax <u>B</u> uffers <u>W</u> indow <u>H</u> elp |

|                                                                                                    |

| 1 covercheck load ucdb//reports/final.ucdb                                                         |

| 2 vlog -f/compileRTL. <b>list</b>                                                                  |

| 3 netlist clock clk 50mhz -period 20 ns -waveform 0 10 ns                                          |

| 4 netlist clock PCIE_CORE_CLK -period 4 ns -waveform 0 2 ns                                        |

| 5 netlist clock APB CLK -period 20 ns -waveform 0 10 ns                                            |

| <pre>6 netlist clock AXI_AHB_CLK -period 8 ns -waveform 0 4 ns</pre>                               |

| 7 covercheck compile -d pcie_system_top                                                            |

| 8 <mark>n</mark> etlist constant LT TCK 0                                                          |

| 9 netlist clock LT SCK -period 10 us                                                               |

| 10 covercheck generate exclude covercheck_verify.db covercheck_exclude.do                          |

| 11 covercheck verify -effort low -witness waveforms                                                |

| 12 covercheck verify -effort high -witness waveforms                                               |

|                                                                                                    |

#### **CoverCheck generated the exclusion list after running formal analysis with UCDB and RTL**

| ▼ cover_e                 | exclude_qautocheckrunk/main/scripts) - GVIM8 _ 🛛 🗸 🗸 🗸 🗸 🖉               |

|---------------------------|--------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> dit | <u>T</u> ools <u>S</u> yntax <u>B</u> uffers <u>W</u> indow <u>H</u> elp |

|                           | - 二 二 今 (今 ) 米 雪 (論 ) 段 中 午 ) 🏣 🔛 拳 ! 🍕 🖩 🍬 ) 🔯 🔯                        |

| 9591                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntb_sm int_state_intassert -comment "CoverCheck:FSM"</pre>          |

| 9592                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntb_sm int_state_inton -comment "CoverCheck:FSM"</pre>              |

| 9593                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntb_sm int_state_intdeassert -comment "CoverCheck:FSM"</pre>        |

| 9594                      |                                                                          |

|                           | <pre>ntc_sm int_state_intassert -comment "CoverCheck:FSM"</pre>          |

| 9595                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntc_sm int_state_inton -comment "CoverCheck:FSM"</pre>              |

| 9596                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntc_sm int_state_intdeassert -comment "CoverCheck:FSM"</pre>        |

| 9597                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntd_sm int_state_intassert -comment "CoverCheck:FSM"</pre>          |

| 9598                      | <pre>coverage exclude -du pciexp64_multifunc_confctrl -fstate i</pre>    |

|                           | <pre>ntd_sm int_state_inton -comment "CoverCheck:FSM"</pre>              |

| 9599                      |                                                                          |

|                           | <pre>ntd_sm int_state_intdeassert -comment "CoverCheck:FSM"</pre>        |

| 9600                      | <pre>coverage exclude -du pciexp64_rxvc _fstate ct_sm ct_state_</pre>    |

|                           | ct_proceed -comment "CoverCheck:FSM <mark>"</mark>                       |

|                           | 9600,94 Bot                                                              |

- Generated exclusion list was then reviewed by Design Team for Sign-off.

- Saved approx. 3 weeks which involves (reviewing the coverage database for each uncovered item.)

## **Section Agenda**

- Questa Covercheck

- PCIe evaluation bench approach

- Results

References

## The CoverCheck tool saved time in coverage exclusion analysis

- > It only took 3 hours to run

- But it saved ~3 weeks of analysis/debug and design team interaction effort!

## **Section Agenda**

- Questa Covercheck

- PCIe evaluation bench approach

- Results

- Benefits

#### References

- PCIe block internal specification

- <u>http://www.mentor.com/products/fv/questa-formal/</u>

- Questa CoverCheck User Guide, v10.3a

## **THANK YOU**

© 2011 Mentor Graphics Corp. **www.mentor.com**

## Agenda

- Introduction

- Coverage Backgrounder

- Targeting Unreachable Coverage with Formal

- Reaching Coverage Closure Faster

- Conclusion

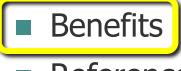

## **Coverage Closure Process**

- Verification Planning

- Requirements Mapping

- Coverage Planning

- Testbench Creation

- Coverage Modeling

- Stimulus Modeling

- Verification IP

- Achieving Coverage

- Regression Management

- Simulation-Based Techniques

- Formal-Based Techniques

- Analysis & Reporting

- Analyzing

- Ranking & Merging

- Reporting

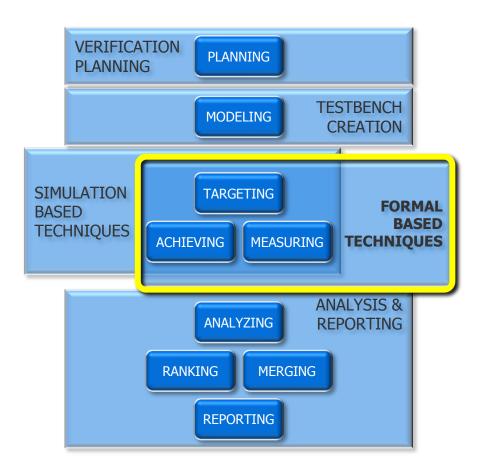

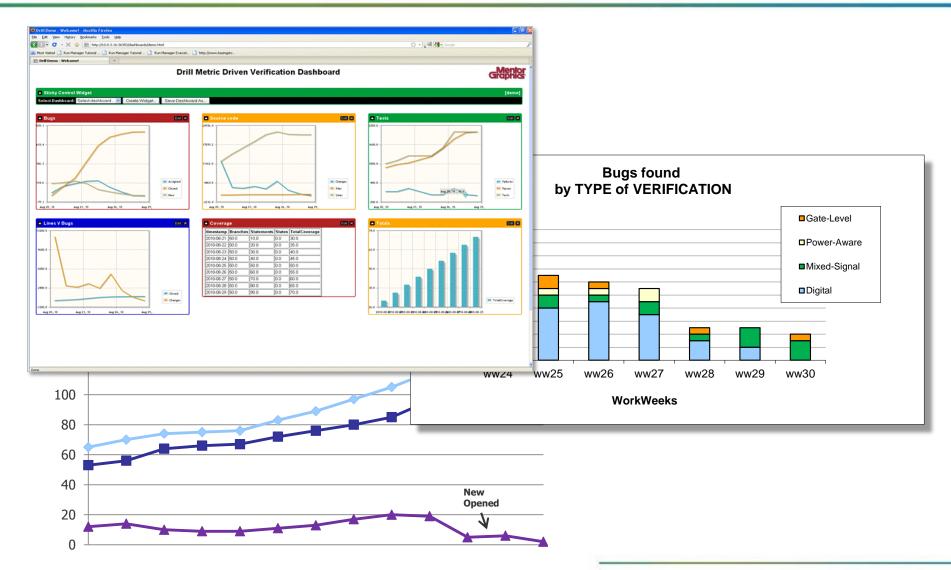

#### **Coverage Data Management is the Key to Reaching Overall Coverage Closure Faster**

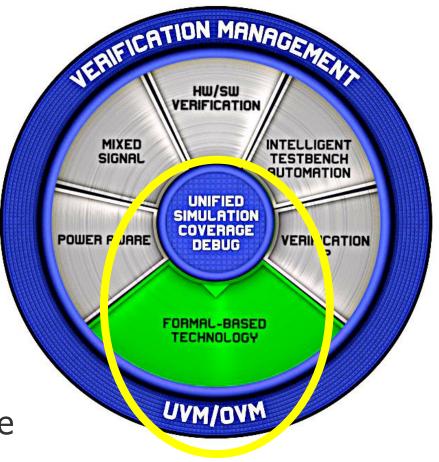

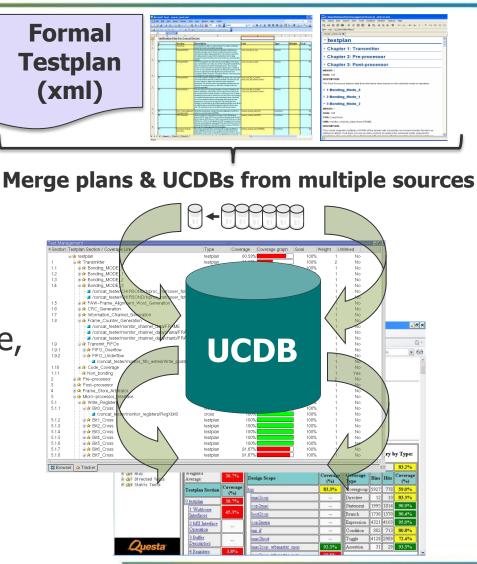

#### **Questa Verification Management** *The intersection of Process, Tools and Data*

- Built around a high performance Unified Coverage Database

- Electronic Coverage Closure with Testplan Tracking

- Improve Regression time-to-debug with Results Analysis

- "Are we getting closer to done?" Trend Analysis

- Improve Regression Productivity with Run Management

- Improve Code Coverage Closure with Questa CoverCheck

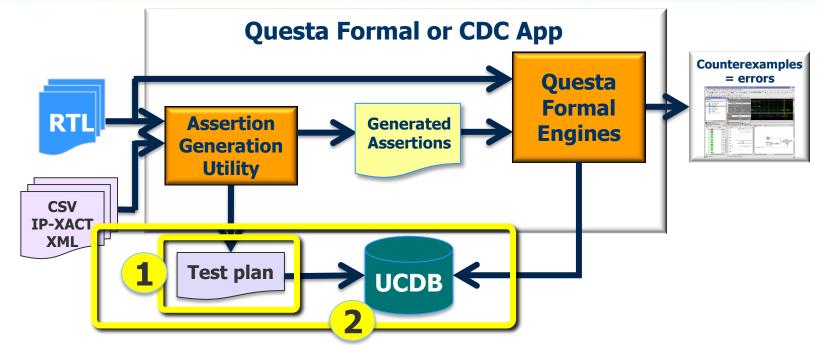

#### **Automated Test Plan Flow**

#### Create a "test plan" from your spec

- 1. An XML file generated from your CSV/IP-XACT/XML containing test plan entries for all checks & coverage

- 2. Can be converted to a UCDB and viewed/merged into the Questa Verification Management environment

#### **Formal Integration with Project Testplan**

Testplan flow provides [multi-tech] management, tracking, & analysis

✓ Formal data includes coverage, proofs, and property checks

#### Manage and Comprehend Volume of Results with **Powerful Analysis and Reporting Capabilities**

| Code Coverage Analysis                                                                                                                                                                    | + @ ×                                                                                                 |                                               |                                                                             | 🐮 Covergroups 🖂 🔤                                                                                                                                                   |                                                           |                                                      |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|--------|

| 3ranch Analysis - by instance (/concat_tester/CHIPBOND/postproc_                                                                                                                          |                                                                                                       | and the state state.                          | 4 <b>1</b>                                                                  | ▼ Name                                                                                                                                                              | Coverage Go                                               | oal % of Goal                                        | Status |

| Post. vhd<br>66 if RESET = '0' then<br>58 elsif PRELOAD = '1' then<br>70 elsif DECREMENT = '1' then<br>73 if RESET = '0' then<br>75 elsif PRELOAD = '1' then<br>77 elsif DECRE Assertions | 📕 Verification Test Analysis - Rai                                                                    |                                               | testplan/Transn<br>Coverage<br>15<br>67<br>72<br>72<br>72<br>73<br>73<br>73 | <ul> <li>/concat_tester</li> <li>TYPE monitor_CRC</li> <li>TYPE monitor_tests</li> <li>TYPE monitor_chan</li> <li>CVP monitor_ch</li> <li>CVP monitor_ch</li> </ul> | 33.3% 10<br>40.0% 10<br>87.5% 10<br>50.0% 10<br>100.0% 10 | 0 33.3%<br>0 40.0%<br>0 87.5%<br>0 50.0%<br>0 100.0% |        |