# Data-Driven Approach to Accelerate Coverage Closure on Highly Configurable ASIC Designs

Tulio Pereira Bitencourt, Rasadhi Attale, Samuel Man-Shun Wong,

Po-Shao Cheng, Anton Tschank

Tessent Embedded Analytics – Siemens

**SIEMENS**

# Agenda

1. Introduction – Tesson Embedded Analytics

2. Challenges of Working with Highly Configurable IPs

3. Requirement Management and Verification Planning

4. Structure for Effective Regressions

5. Accumulated Coverage Structure

6. Traffic Light System & Unreachability

7. Real-time and Interactive Dashboards

8. Early Bug Detection – Conclusion

# Tessent Embedded Analytics functional monitoring

Observing non-intrusively if your SoC behaves as it was meant to

Full visibility into HW/SW interactions in deployed systems enabling optimizations and debugging throughout the entire system lifecycle from lab to deployment

- Real-time debug and trace environment

- Optimize software to achieve better performance and efficiency

- Use historical performance data to inform designs of next generation designs

Bus Monitor

Status Monitor

Trace Encoder

Static Instrumentation

CPU Debug Module

NoC Monitor

Direct Memory Access

Trace Receiver

AI

Data Centre

Automotive

5G/6G

Storage

Audio

# Introduction – Tessent Embedded Analytics

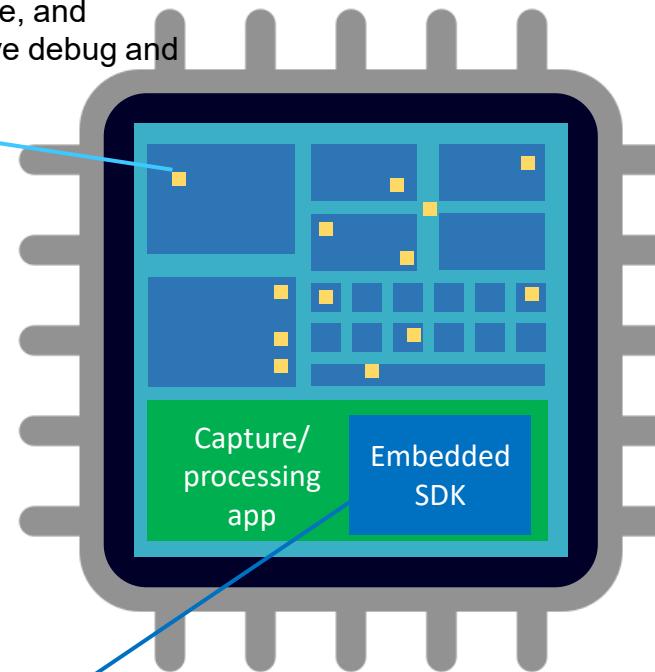

## Smart monitors

Range of ~40 IP blocks including run-time configurable monitors, infrastructure, and interfaces that enables non-intrusive debug and performance monitoring

1

2

## Software for interactive debug and optimization

Debug software running on a separate PC is used to interact with the EA smart monitors

## Edge analytics enablement

Applications developed using the Embedded SDK interact with the monitors, capture, and process results

3

4

## Fleet monitoring enablement

Applications developed using Host Suite can automate data orchestration and analytics from one or multiple devices

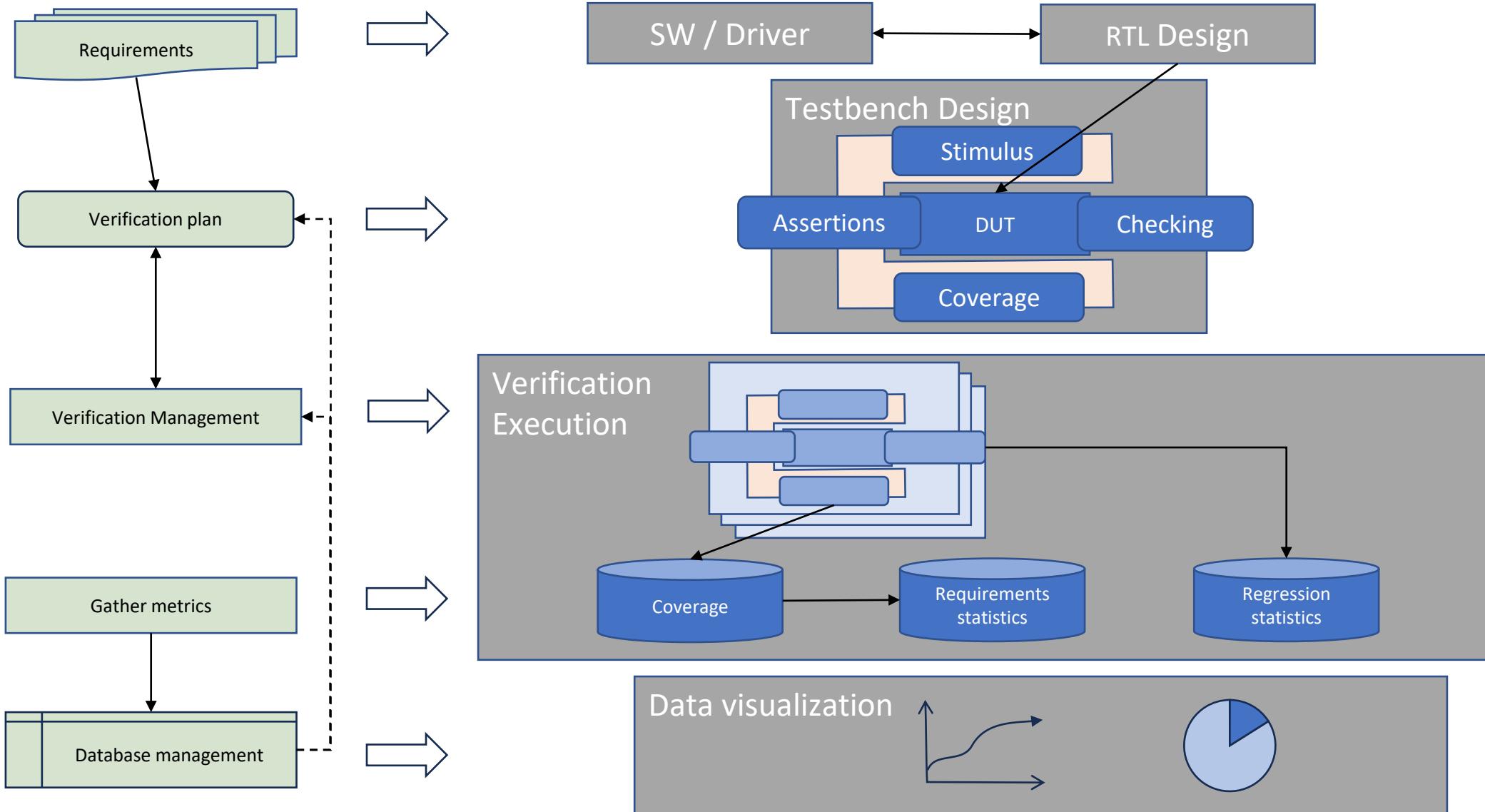

# Tools & Requirements

- **Requirement tracking tool** (documentation) (e.g., Polarion)

- **Verification management tool** (e.g., VIQ)

- **Digital simulation tool** (e.g., QuestaOne)

- **Regression running tool** (e.g., VRM)

- **Coverage visualization & merging tool** (e.g., Visualizer)

- **Regression scheduler & CI/CD** (e.g., Jenkins)

- **Metrics, data visualization and dashboards** (e.g., VIQ)

**Vendor-agnostic flow!**

# Challenges of Working with Highly Configurable IPs

# Highly-Configurable IPs

## "Highly-Configurable"

- Designs with many RTL parameters

- Compile-time constant, large impact on synthesis results

- “CONFIG” = “set of parameters”

## Who

- IP vendors must provide configurable designs

- Standard protocols, AXI, USB etc.

- Optional features/optimisation

- E.g. Tessent Embedded Analytics has extremely high configurability

- Scaling up means increasingly modular designs

- Accumulates wider range of configurability

- More inter-dependencies that result in bugs or invalid configurations

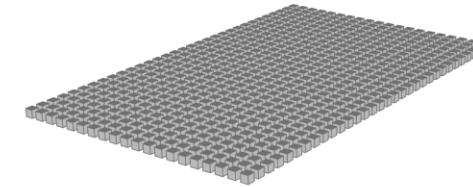

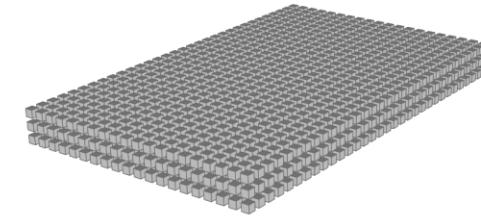

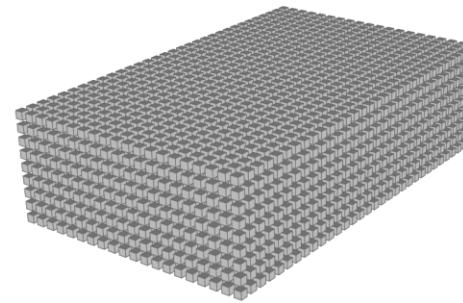

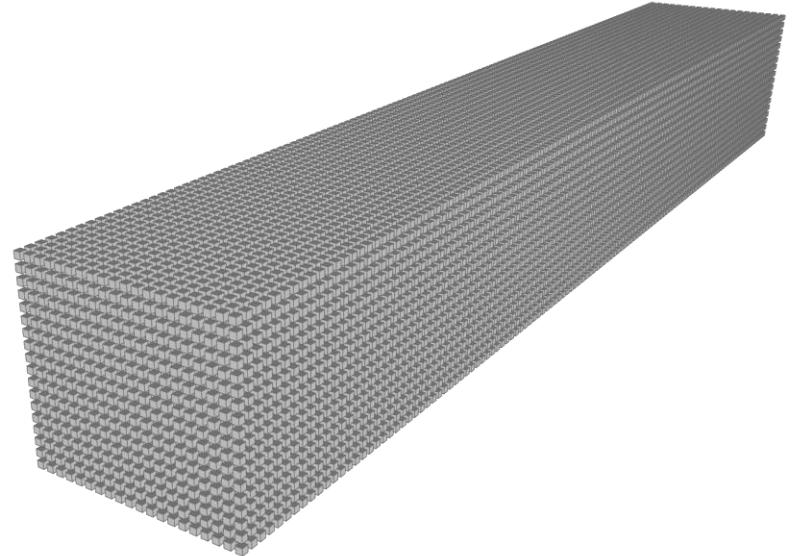

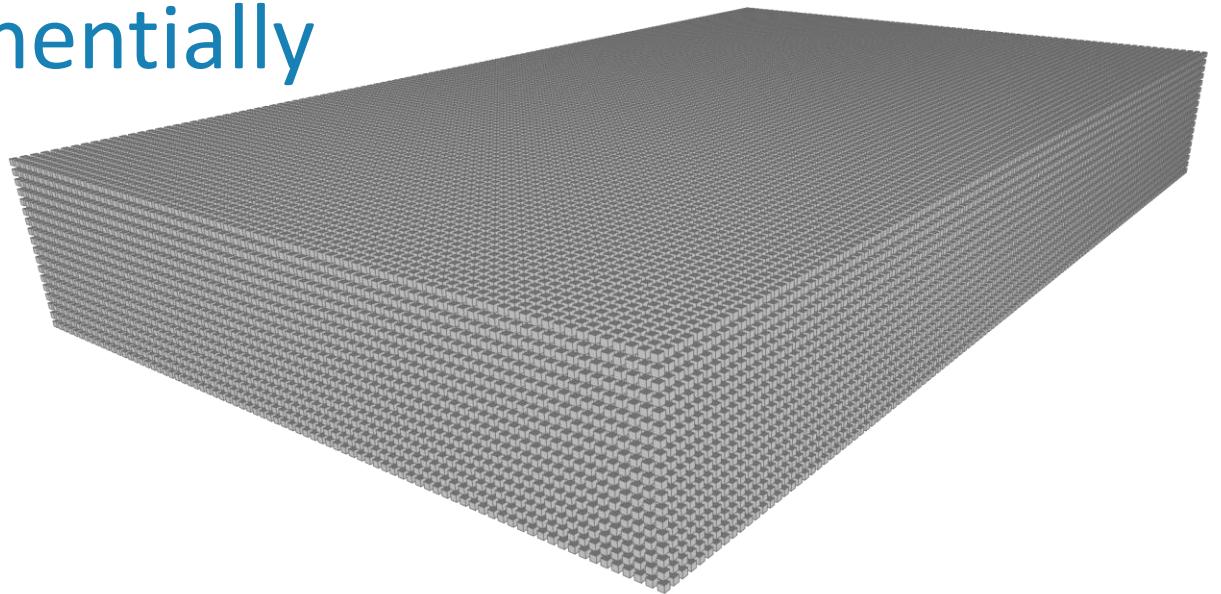

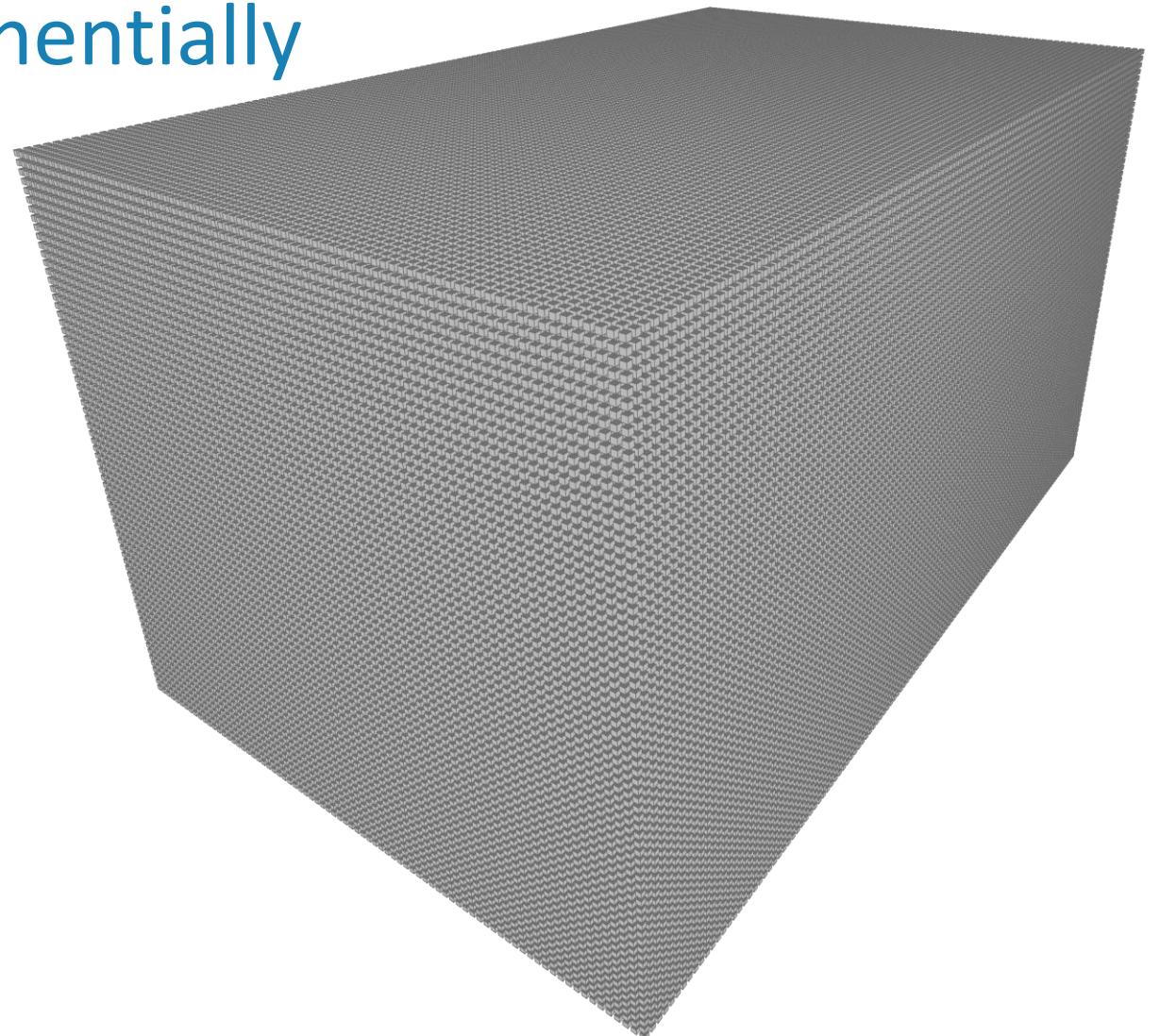

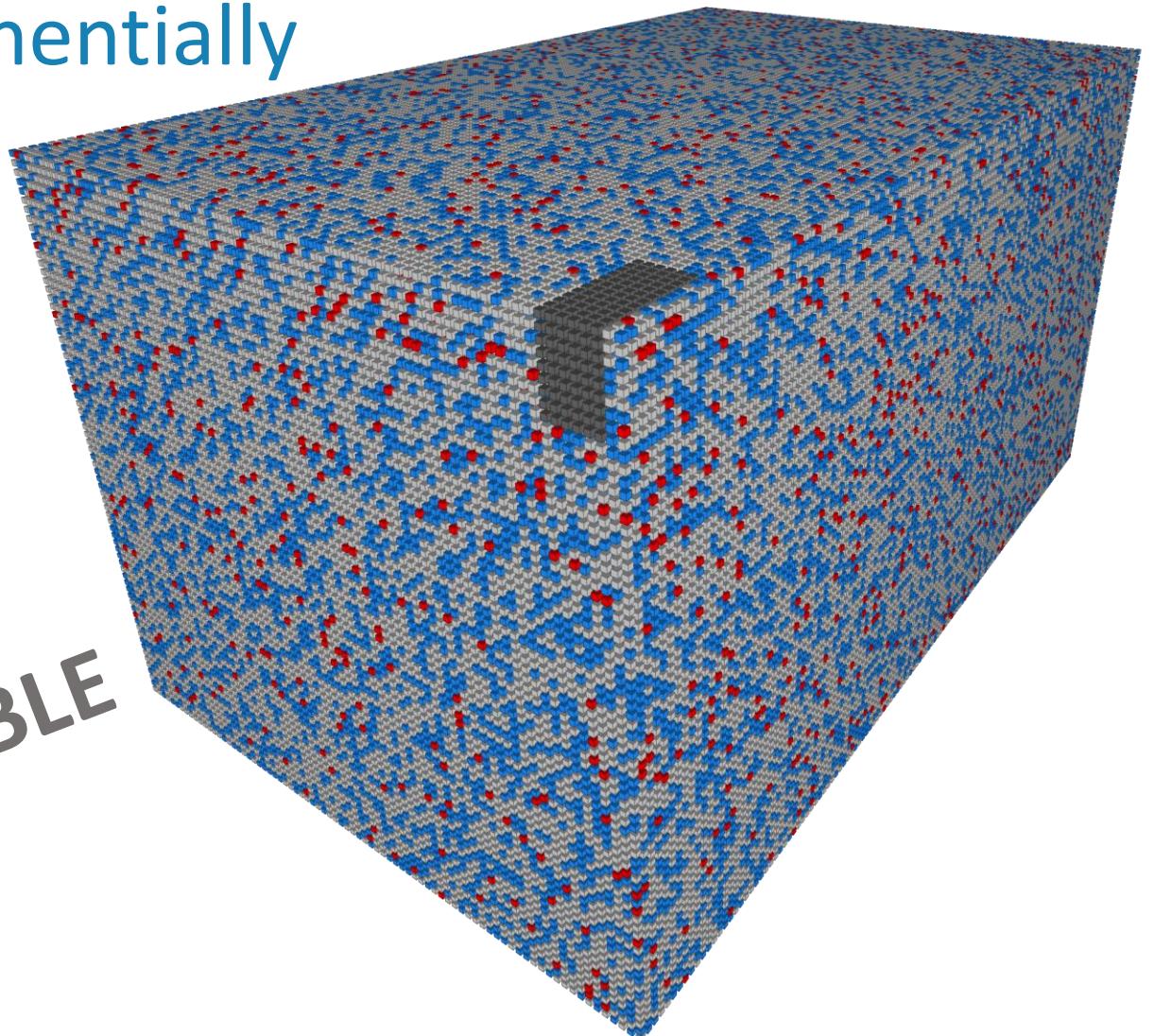

# Parameter-space Scales Exponentially

`protocolA_channel_width`

# Parameter-space Scales Exponentially

`protocolA_channel_width`

`protocolA_num_channels`

# Parameter-space Scales Exponentially

`protocolA_channel_width`

`protocolA_num_channels`

`protocolB_data_width1`

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

```

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

```

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

```

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

```

BUGS

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

buffer_size

num_buffers

```

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

```

```

buffer_size

num_buffers

retiming_options

reset_value

```

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

```

```

buffer_size

num_buffers

retiming_options

reset_value

optional_optimisation

more_feature_support

```

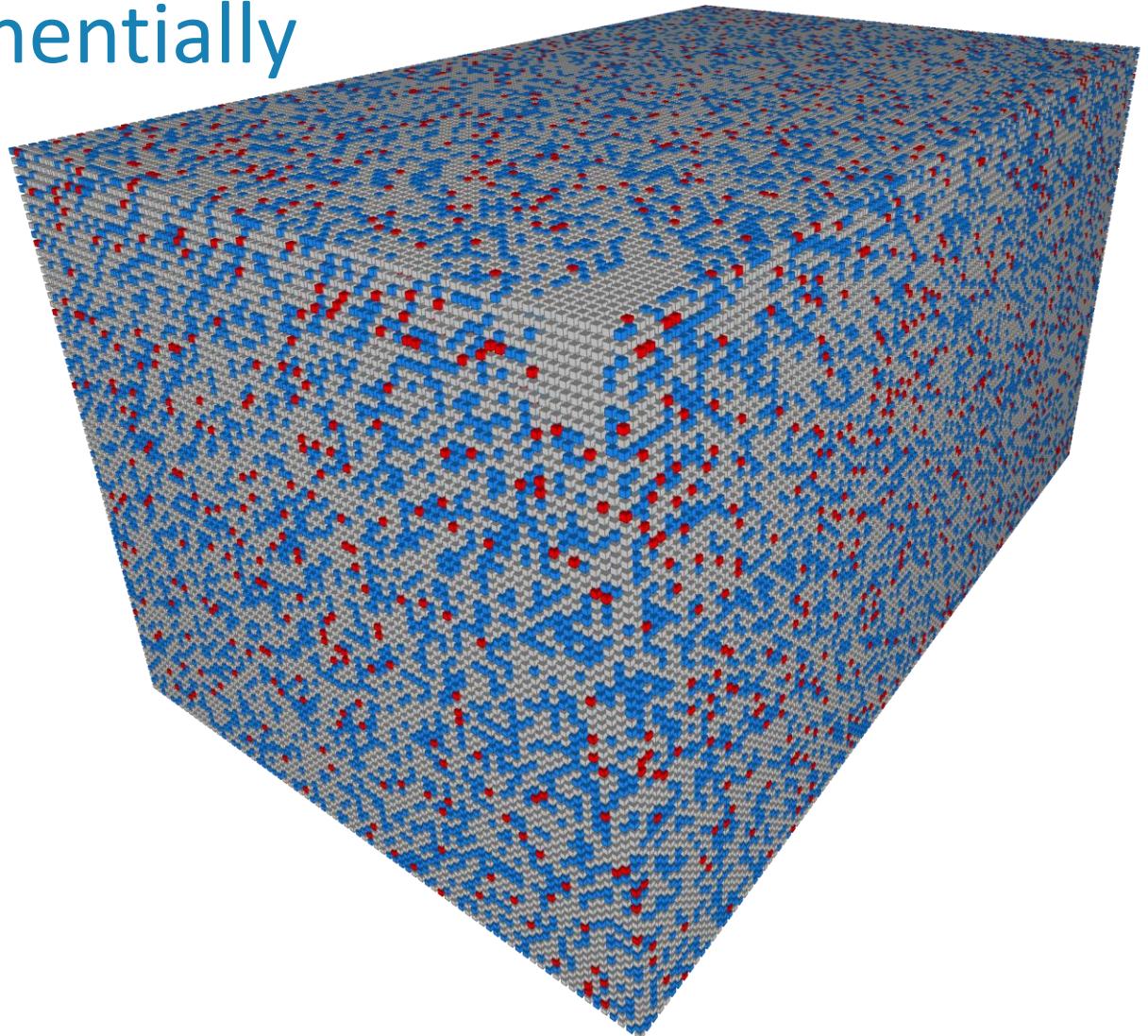

# Parameter-space Scales Exponentially

protocolA\_channel\_width

protocolA\_num\_channels

protocolB\_data\_width1

protocolB\_data\_width2

protocolB\_option1

protocolB\_option2

buffer\_size

num\_buffers

retiming\_options

reset\_value

optional\_optimisation

more\_feature\_support

BUGS

COVERAGE

# Parameter-space Scales Exponentially

```

protocolA_channel_width

protocolA_num_channels

protocolB_data_width1

protocolB_data_width2

protocolB_option1

protocolB_option2

```

```

buffer_size

num_buffers

retiming_options

reset_value

optional_optimisation

more_feature_support

```

BUGS

COVERAGE

UNREACHABLE

# Verification Challenges

Verification complexity scales exponentially with design ...

... So a data-driven methodology is needed.

Many more test scenarios to cover

Many more bugs to find

Incomplete insight into verification progress

Unclear where best to invest resources

Time-to-market scales drastically

Trace and track progress of many configurable requirements in documentation

Managing complex verification plans for both shared and unique features

Manage compatibility of verification execution with all parameter sets

Gather metrics to give confidence of high verification quality across all configurable functionality

Visualizing verification metrics across all configurations for quick feedback

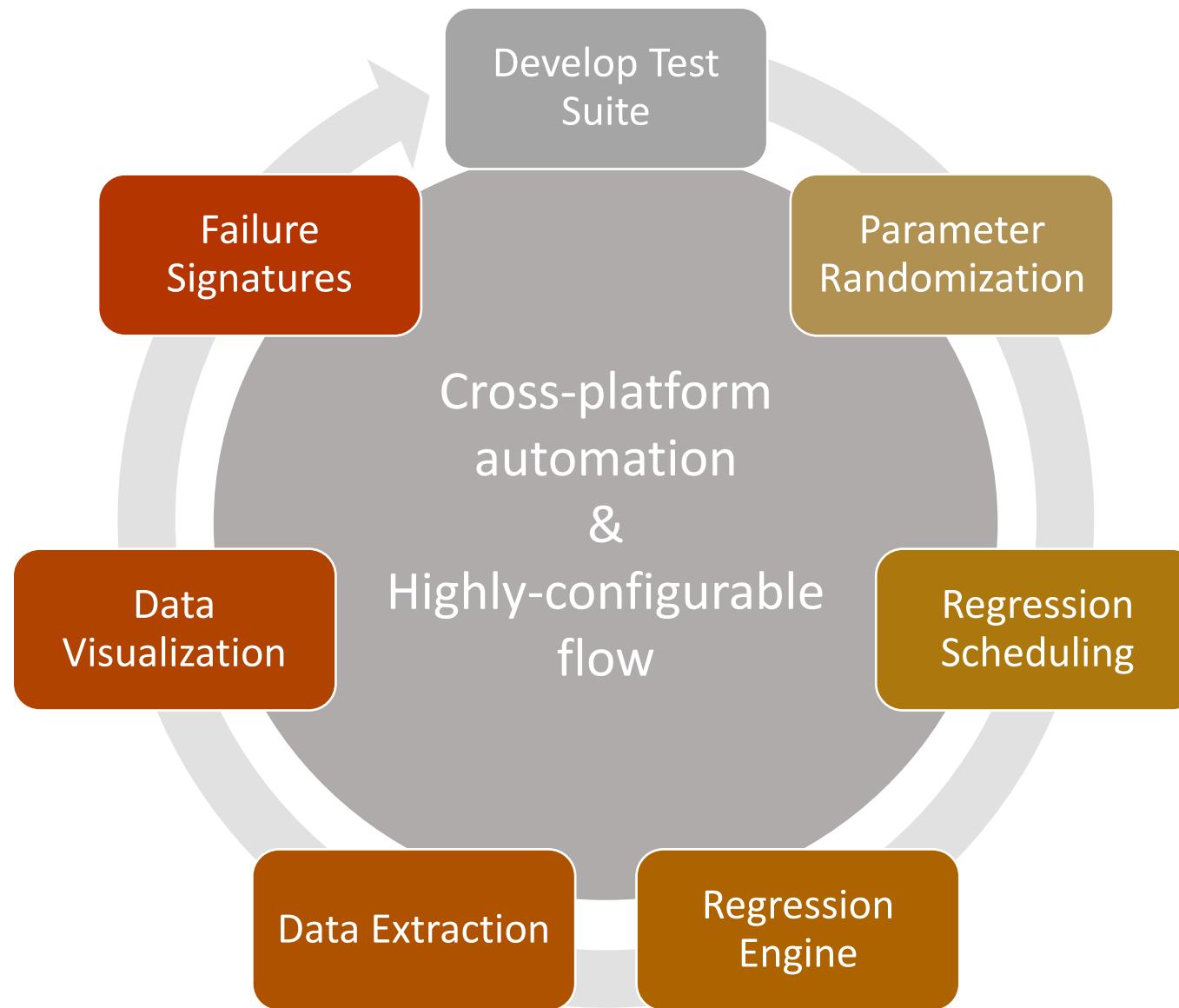

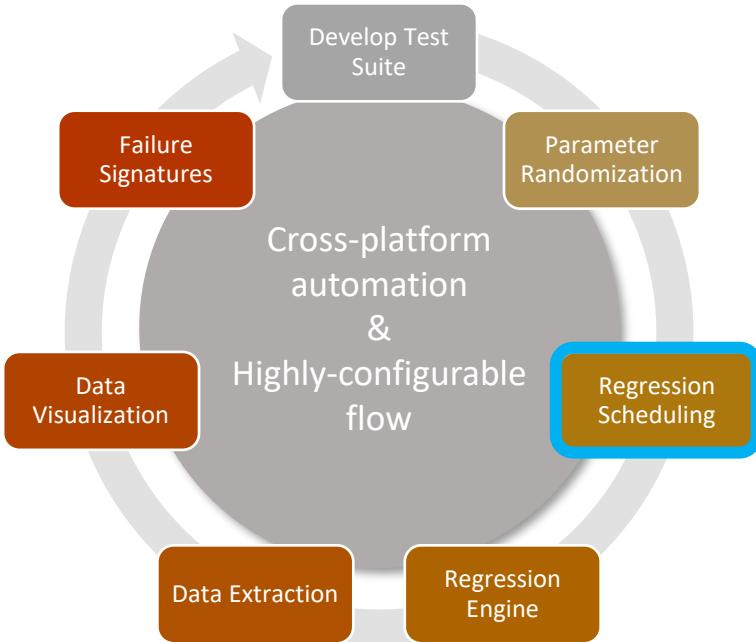

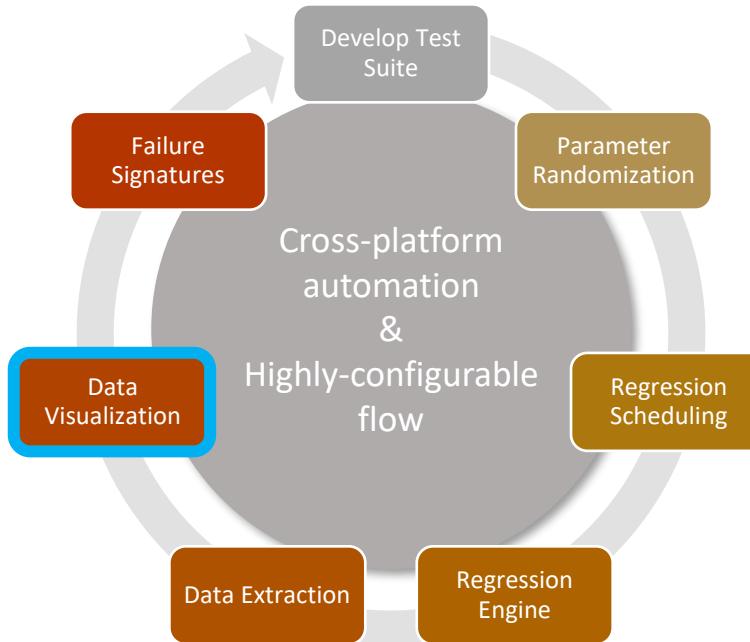

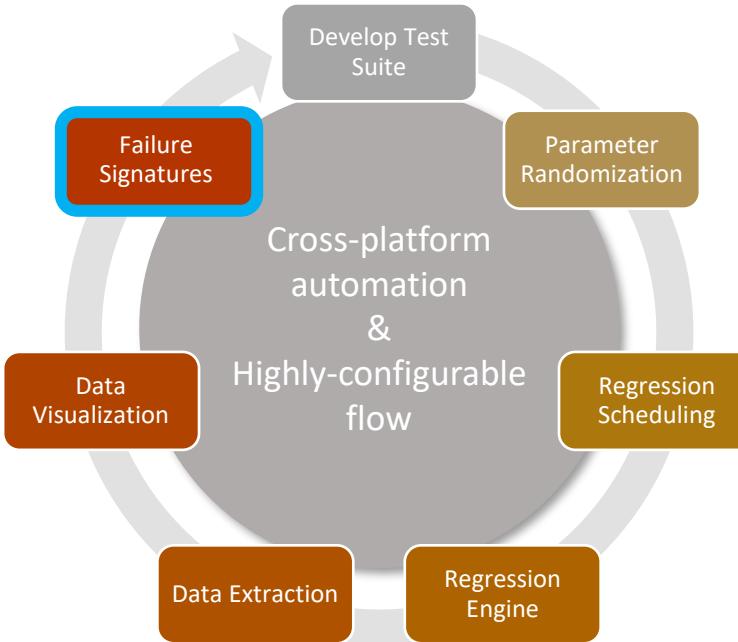

# Summary of the proposed flow

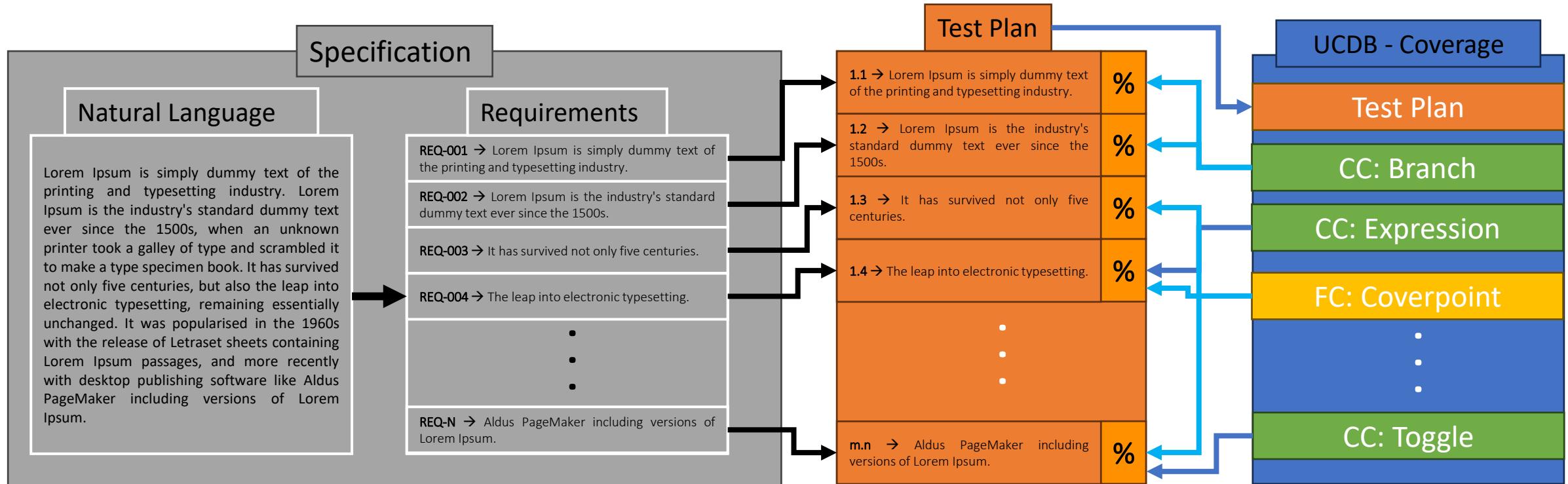

# Requirement Management and Verification Planning

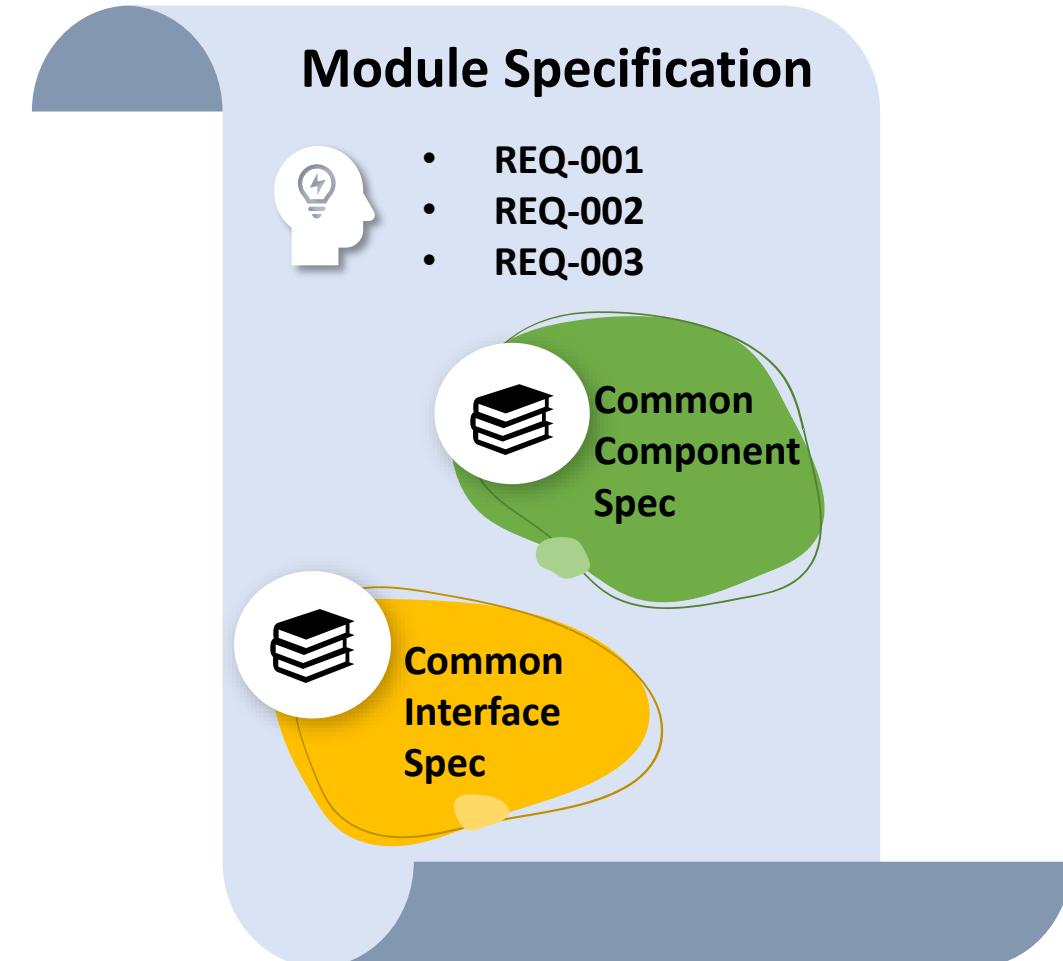

# Specification Management

- Itemised requirements for each IP module

- Referenced specification from common components/interface/module

- Maximise reusability

- Easier to maintain

- Only need to be formally reviewed once

- Customised approval flow/work items/scripts, baseline, branching, and much more ...

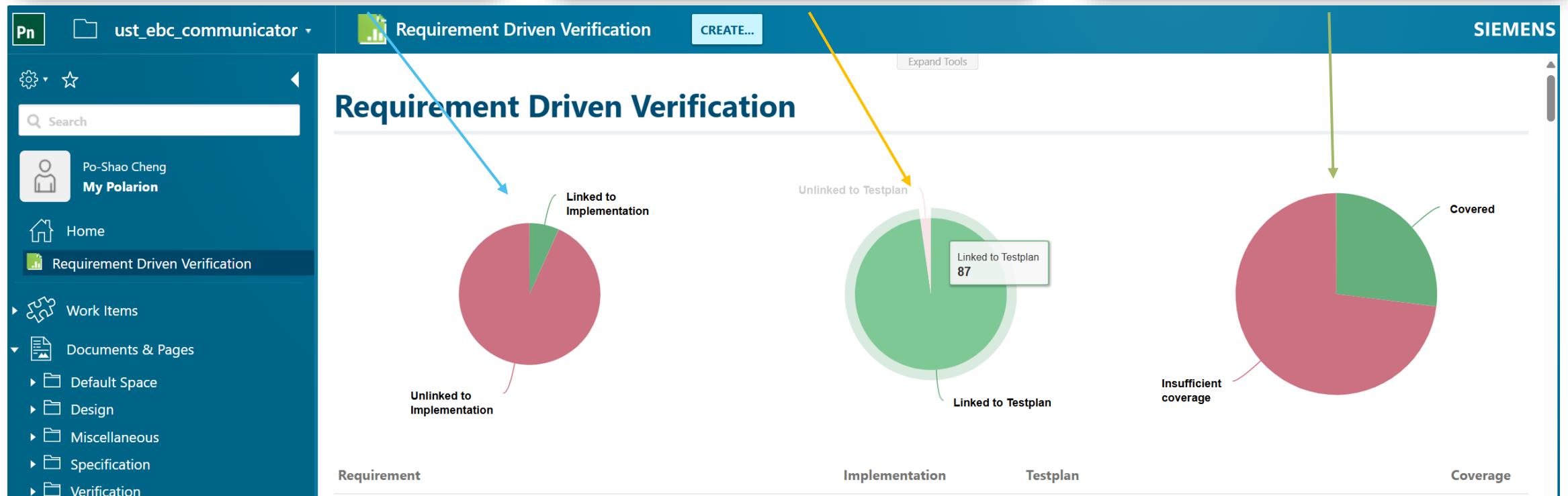

# Requirement Traceability

- Ensure every requirement is linked to the test plan

- Traceability is straight forward and easy to read

- Window pop-out showing details of the test plan item

- Crucial aspect of adhering to industry standards e.g. ISO 26262 and DO-254

**5.1 Parameters**

| Wiki Content                                                     | Parameter Name                 | Description                                                                                                                             | Default Value | Legal Values |

|------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|

| <b>EBC Communicator Implementation Parameters (All variants)</b> |                                |                                                                                                                                         |               |              |

|                                                                  | <a href="#">index_strip_p</a>  | Index Stripping in downstream frame packing:<br>'0' = Index Stripping Disabled<br>'1' = Index Stripping Enabled (if index_length_p > 7) | 0             | 0            |

| <b>Message Interface</b>                                         |                                |                                                                                                                                         |               |              |

|                                                                  | <a href="#">index_length_p</a> | The length in bits of the message index.                                                                                                | 8             | 1 : 16       |

|                                                                  | <a href="#">ds_msg_sz_p</a>    | Width of downstream message pathway is $2^{ds\_msg\_sz\_p}$                                                                             | 5             | 3 : 9        |

|                                                                  | <a href="#">us_msg_sz_p</a>    | Width of upstream message pathway $2^{us\_msg\_sz\_p}$                                                                                  | 3             | 3 : 9        |

Project: **ust\_ebc\_communicator** Testplan: **ebc\_d2\_tp**

Section: **2.1.1.1.1 ds\_buffers\_p**

Coverage: **100.00%**

Goal %:

**100%**

Achieved Goal %: **100.00%**

Weight:

**1**

Description:

Unimplemented:

AtLeast:

Link Status:

**Clean**

**Work Records**

**Approvals**

Approving User: State

Anton Tschanck Approved

honyau8b Approved

Iain Robertson Approved

**Linked Revisions**

**Linked Work Items**

| Suspect         | Role                                     | Title |

|-----------------|------------------------------------------|-------|

| has parent      | <a href="#">UST_EBC-450 - Param</a>      |       |

| is validated by | <a href="#">2.1.1.1.1 - ds_buffers_p</a> |       |

| is validated by | <a href="#">2.1.1.1.1 - ds_buffers_p</a> |       |

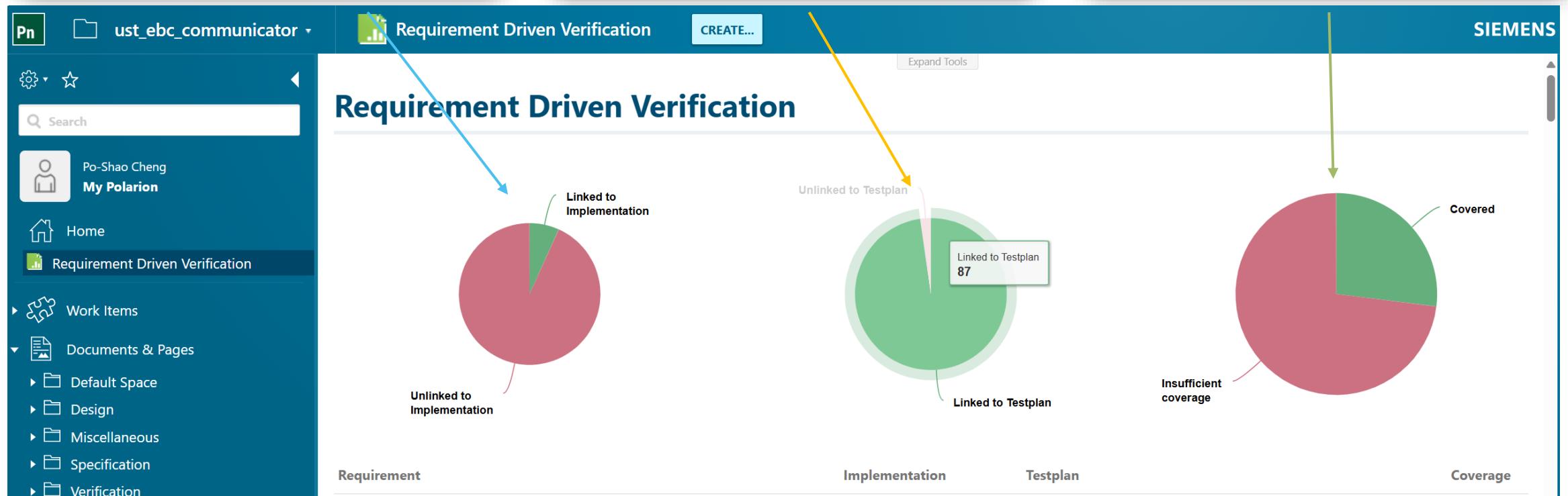

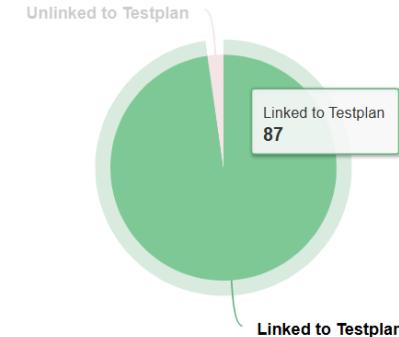

# Requirement Traceability Dashboards

- 01** **RTL Implementation**

Requirements linked to the actual RTL implementation e.g. VHDL, Verilog using pragmas.

- 02** **Test Plan**

Requirements linked to the Test Plan.

- 03** **Coverage Results**

Shows coverage number for each test plan items that the requirements are linked to.

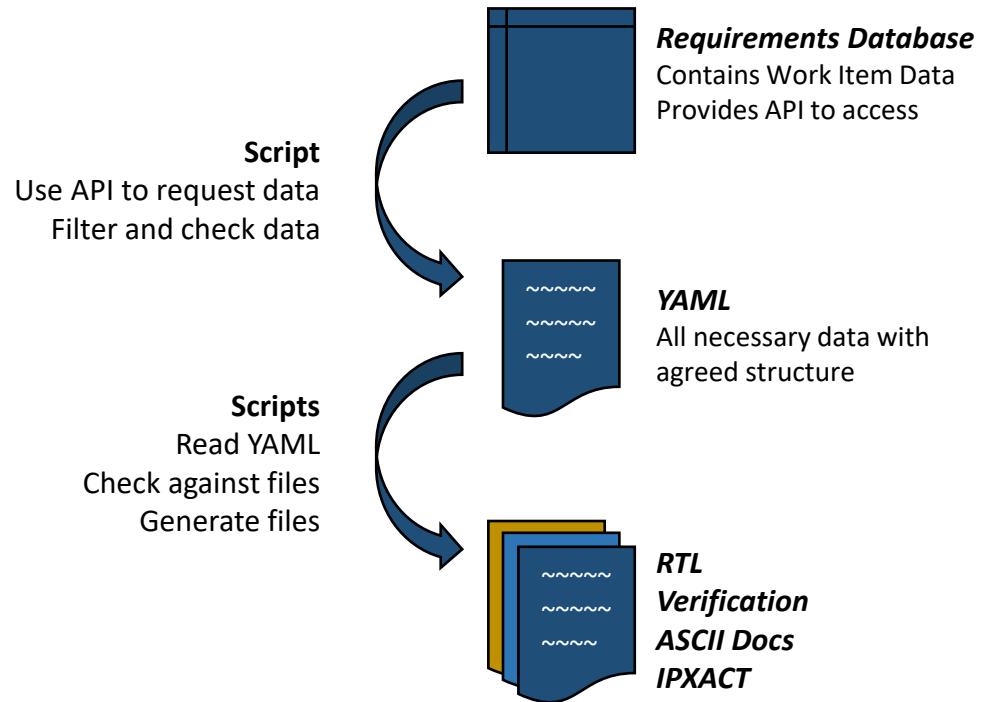

# Exporting Data from Specification

- Single source of truth

- API to access its database

- Auto-generated YAML files

- Further automated process

- Auto-generated RTL sub-components

- Auto-constraining parameters of the designs

```

1 module_defns:

2 - name: ust_aurora_communicator

3 short_name: aurora

4 module_type: communication_module

5 param_groups:

6   Aurora Communicator Implementation Parameters:

7     ds_lanes_p: {value: 1, legal_values: {min: 1, max: 8}, comment: 'Number of SerDes lanes'}

8     ds_lane_width_p: {value: 10, legal_values: [10, 20, 40, 80], comment: 'Width of data interface per lane'}

```

# VIQ - Testplan Author

- Parameters used in the test plan – highly configurable reuseable

- Maximise reusability across multiple IP modules for common components, interfaces, protocols

- Strong emphasis on collaboration and effective communication

- Comment, reuse of other testplans, coverage analyzer looking at UCDBs

| #     | Section                              | External Links                                      | T | Weight                                                          |

|-------|--------------------------------------|-----------------------------------------------------|---|-----------------------------------------------------------------|

| ► 1   | Ports                                |                                                     |   | (%PORTS%)                                                       |

| ► 2   | Parameters                           |                                                     |   | (%PARAMETERS%)                                                  |

| ► 2.1 | index_length_p                       | ✗ <a href="#">UST_MSGIF-34</a> - index_length_p     | ✗ | (%INDEX_LENGTH_agnostic%)                                       |

| ► 2.2 | (%MESSAGE_ENGINE_PREFIX%)ds_msg_sz_p | ✗ <a href="#">UST_MSGIF-79</a> - ds_msg_sz_p        | ✗ | 1                                                               |

| ► 2.3 | (%MESSAGE_ENGINE_PREFIX%)us_msg_sz_p | ✗ <a href="#">UST_MSGIF-78</a> - us_msg_sz_p        | ✗ | 1                                                               |

| ► 2.4 | (%MESSAGE_ENGINE_PREFIX%)retime_p    | ✗ <a href="#">UST_MSGIF-82</a> - retime_p           | ✗ | 1                                                               |

| ► 2.5 | msg_pack_support_p (high perf)       | ✗ <a href="#">UST_MSGIF-84</a> - msg_pack_support_p | ✗ | (%DISASSEMBLE_MESSAGE_PACKS%)*(%HIGH_PERFORMANCE_PACK_SUPPORT%) |

| ► 2.6 | msg_pack_support_p (low perf)        | ✗ <a href="#">UST_MSGIF-85</a> - msg_pack_support_p | ✗ | (%DISASSEMBLE_MESSAGE_PACKS%)*(%LOW_PERFORMANCE_PACK_SUPPORT%)  |

| 2.7   | msg_pack_sz_p                        | ✗ <a href="#">UST_MSGIF-86</a> - msg_pack_sz_p      | ✗ | (%ASSEMBLE_MESSAGE_PACKS%)                                      |

| 2.8   | auth_p                               | ✗ <a href="#">UST_MSGIF-305</a> - auth_p            | ✗ | (%ANALYTIC_MODULE%)*(%AUTHENTICATION_SUPPORT%)                  |

| ► 3   | Features                             |                                                     |   | (%FEATURES%)                                                    |

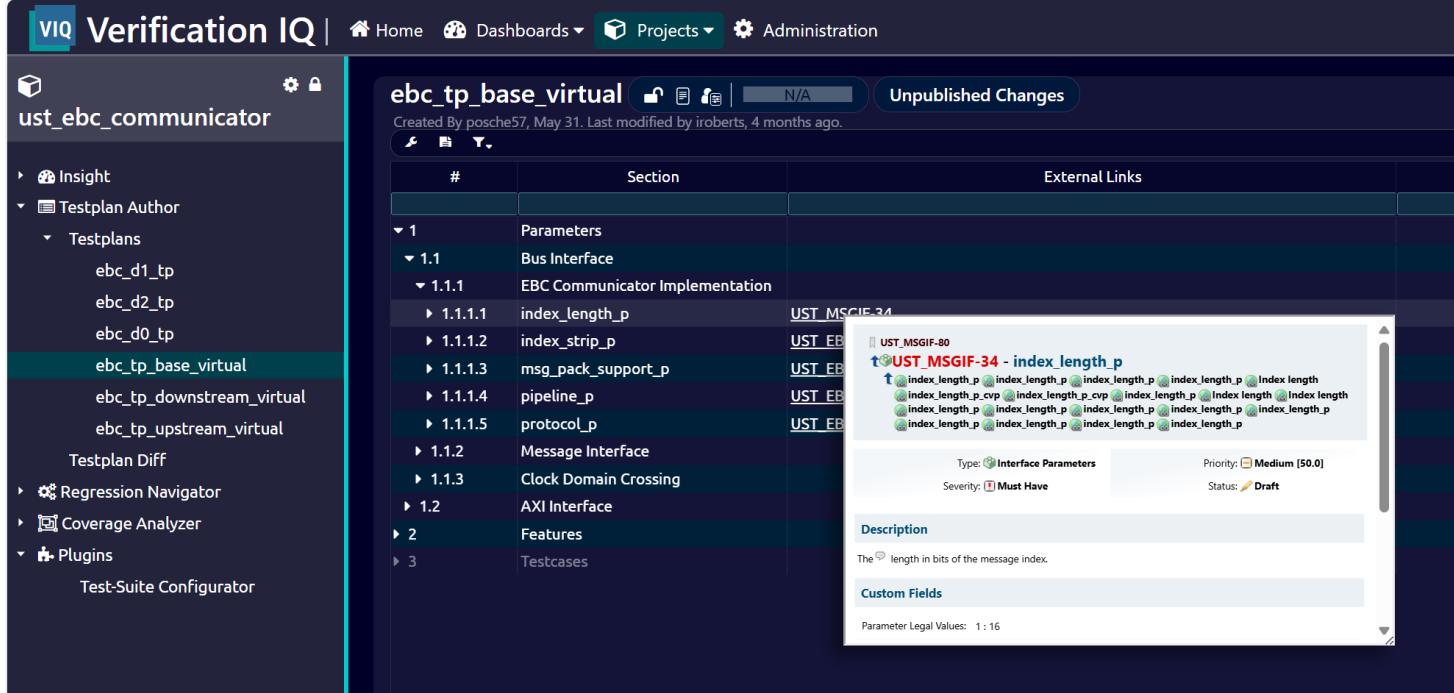

# Test Plan Traceability

- Shows the requirement linked to the test plan item

- Window pop-out showing details of the requirement

The screenshot shows the Verification IQ software interface. On the left, a sidebar for the project "ust\_ebc\_communicator" lists various tools and components: Insight, Testplan Author (with sub-items Testplans, ebc\_d1\_tp, ebc\_d2\_tp, ebc\_d0\_tp, ebc\_tp\_base\_virtual, ebc\_tp\_downstream\_virtual, ebc\_tp\_upstream\_virtual), Testplan Diff, Regression Navigator, Coverage Analyzer, Plugins, and Test-Suite Configurator. The "ebc\_tp\_base\_virtual" item is highlighted with a teal bar. The main pane shows a table for the "ebc\_tp\_base\_virtual" test plan, with sections for Parameters, Bus Interface, Message Interface, Clock Domain Crossing, AXI Interface, Features, and Testcases. The "index\_length\_p" requirement (UST\_MSGIF-34) is selected, and a detailed pop-up window displays its description: "The length in bits of the message index." The pop-up also shows the requirement's details: Type: Interface Parameters, Severity: Must Have, Priority: Medium [50.0], and Status: Draft. It also lists "Parameter Legal Values: 1:16" and "Custom Fields".

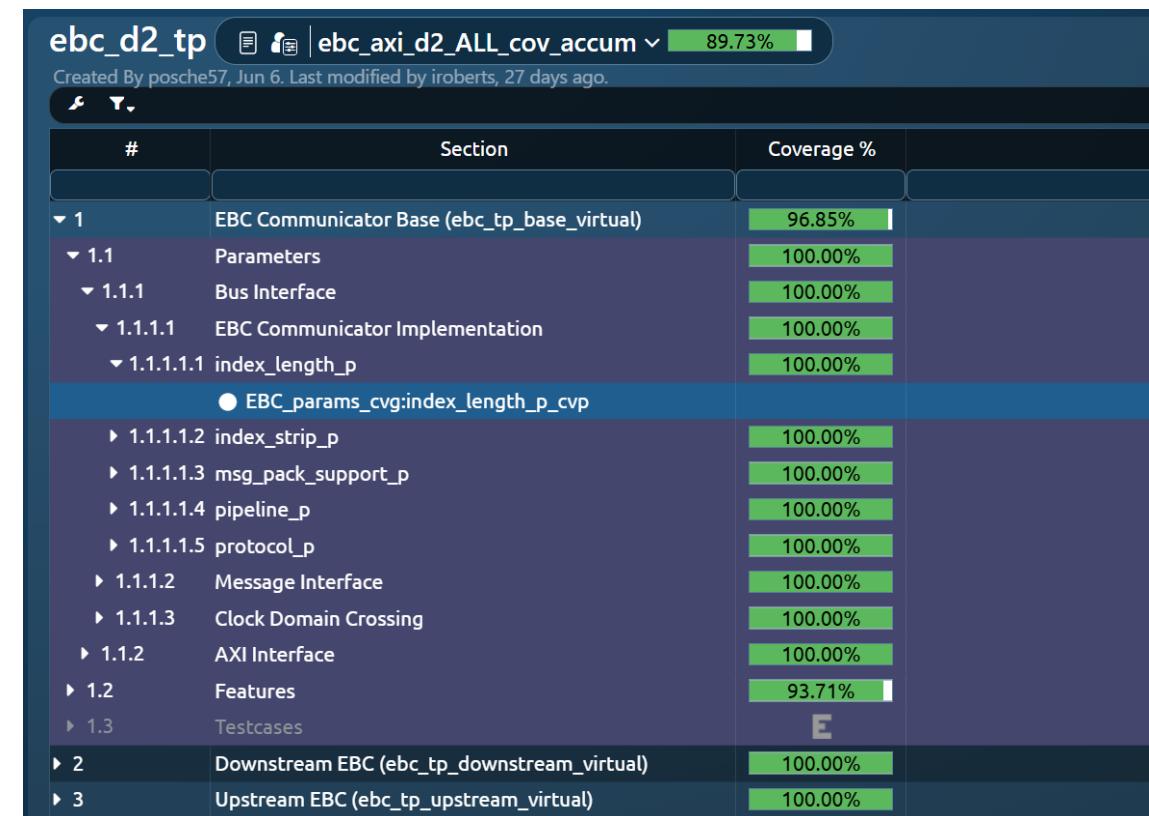

# Coverage Tracking in Test Plan

- Coverage Database linked to the test plan

- Functional coverage

- Test plan is linked to covergroup and/or coverpoints

- Code coverage

- Ports in test plan are linked to toggle coverage

- Test plan coverage

- Shows overall progress of the test plan

- How well the test plan is executed

- Exclusion option available in test plan

# Test Plan Coverage Tracking in UCDB

- Test plan merged to the UCDB

- UCDB = Unified Coverage Database

- Automatically merged at the end of each nightly regression run

- Accumulated UCDB reflected in test plan

- UCDB flow and VIQ dashboards covered in later topics

| Testplan Tracker |                                |            |                                     |           |      |  |

|------------------|--------------------------------|------------|-------------------------------------|-----------|------|--|

| Sec#             | Testplan Section/Coverage Link | Type       | Status                              | Coverage% | Goal |  |

| 0                | ebc_d2_tp                      | Testplan   | <div style="width: 89.44%;"></div>  | 89.44%    | -    |  |

| 1                | EBC Communicator Base          | Testplan   | <div style="width: 96.85%;"></div>  | 96.85%    | 100% |  |

| 1.1              | Parameters                     | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1            | Bus Interface                  | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1          | ...municator Implementation    | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.1        | .../index_length_p             | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.2        | .../index_length_p_cv          | CoverPoint | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.3        | index_strip_p                  | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.4        | msg_pack_support_p             | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.5        | pipeline_p                     | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

| 1.1.1.1.6        | protocol_p                     | Testplan   | <div style="width: 100.00%;"></div> | 100.00%   | 100% |  |

# Specification vs. Test Plan vs. Coverage

# Structure for Effective Regressions

# Parameter Randomization

- Essential for covering param-space

- Seed-based randomization for reproducibility

- Constraints for inter-dependencies (improves efficacy of batch-runs)

```

module_defns :

- name : ust_me_route_decode_m

params :

msg_sz_p          : { value:  3, legal_values: { min: 3, max: 9 } }

index_length_p    : { value:  8, legal_values: { min: 2, max: 16 } }

max_index_length_p: { value: 24, legal_values: { min: 24, max: 24 } }

upper_p           : { value:  1, legal_values: { 0, 1 } }

internal_p         : { value:  0, legal_values: [ 0, 1 ] }

num_inputs_p       : { value:  2, legal_values: { min: 2, max: 5 } }

```

```

complex_constraints_code : |

constraint required_constraints {

smb_connected_p -> upper_p      == 0;

smb_connected_p -> cm_support_p == 2;

internal_p       -> upper_p      == 1;

internal_p       -> cm_support_p > 0;

{internal_p[0], smb_connected_p[0]} dist { 2 }

```

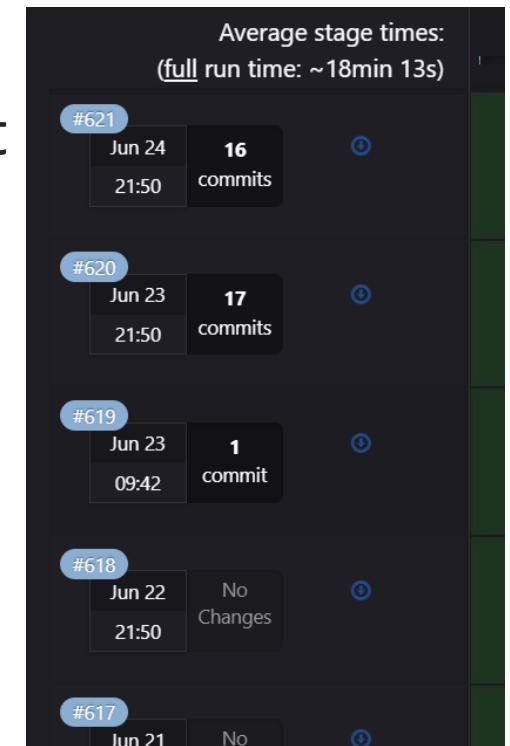

# Regression Scheduling

- Frequency: continuous integration, nightly & weekends

- Different regression lists for different purposes:

- Mini (5mins), nightly, long (weekend), formal, PSS

- Fully flexible for custom test lists e.g. for specific configurations

Pipeline #18415 running

Pipeline running for b4089975 on fix\_reset\_routine\_m...

8✓ **Approve** Approval is optional

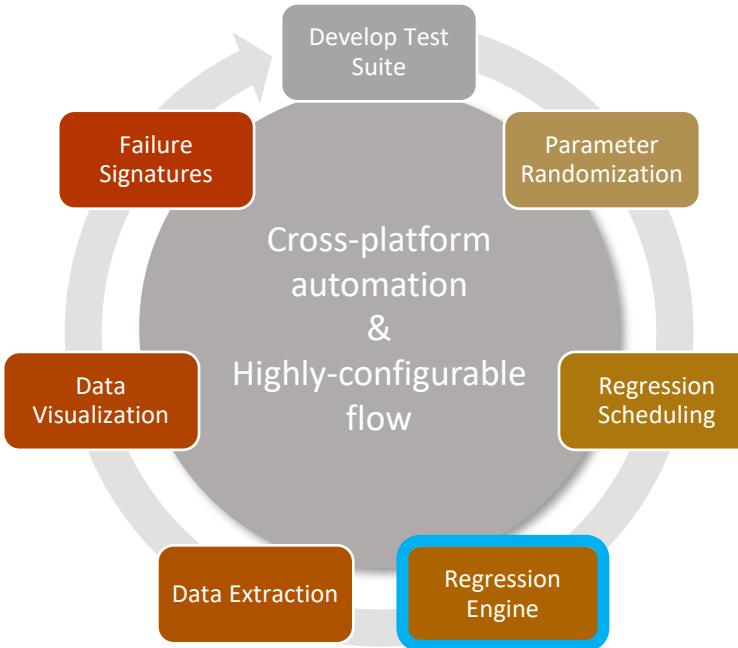

# Regression Engine

- Many stages of tests & scripts

- Executes config-randomization, PSS, simulation, coverage, data extraction

Action script execution status:

```

Total 138 scripts prepared: 138 OK, 0 failed

Total 138 scripts launched: 138 OK, 0 failed

Total 138 scripts finished: 138 OK, 0 failed

```

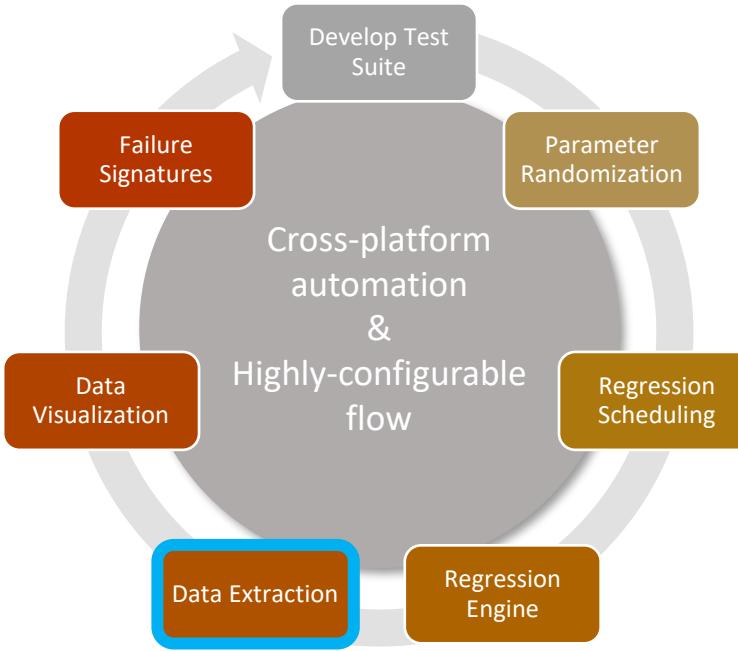

# Data Extraction

- Extractor to port all regression results and UCDBs to one location

- In-house flow (Yaml, Make, Python, Groovy)

- Automated test plan coverage annotation, coverage merging, unreachability-based waivers & repository data statistics

```

# -----

# s0 configs

# -----

- name: s0_DEFAULT

virtual: False

extends: ab

extraopts:

VARIANT: s0

viq_reg:

dataset: ab_s0_req

viq_cov:

- project: ust_msg_abridge

dataset_nightly: ab_s0_DEFAULT_cov_nightly

dataset_accum: ab_s0_DEFAULT_cov_accum

cov_merge:

- name: s0_ALL_CONFIGS

viq_cov:

- project: ust_msg_abridge

dataset_nightly: ab_s0_ALL_cov_nightly

dataset_accum: ab_s0_ALL_cov_accum

viq_testplan:

project: ust_msg_abridge

testplan: ab_s0_tp

```

# Data Visualization

- Separate datasets can be visualized

- Trigger for regression engine

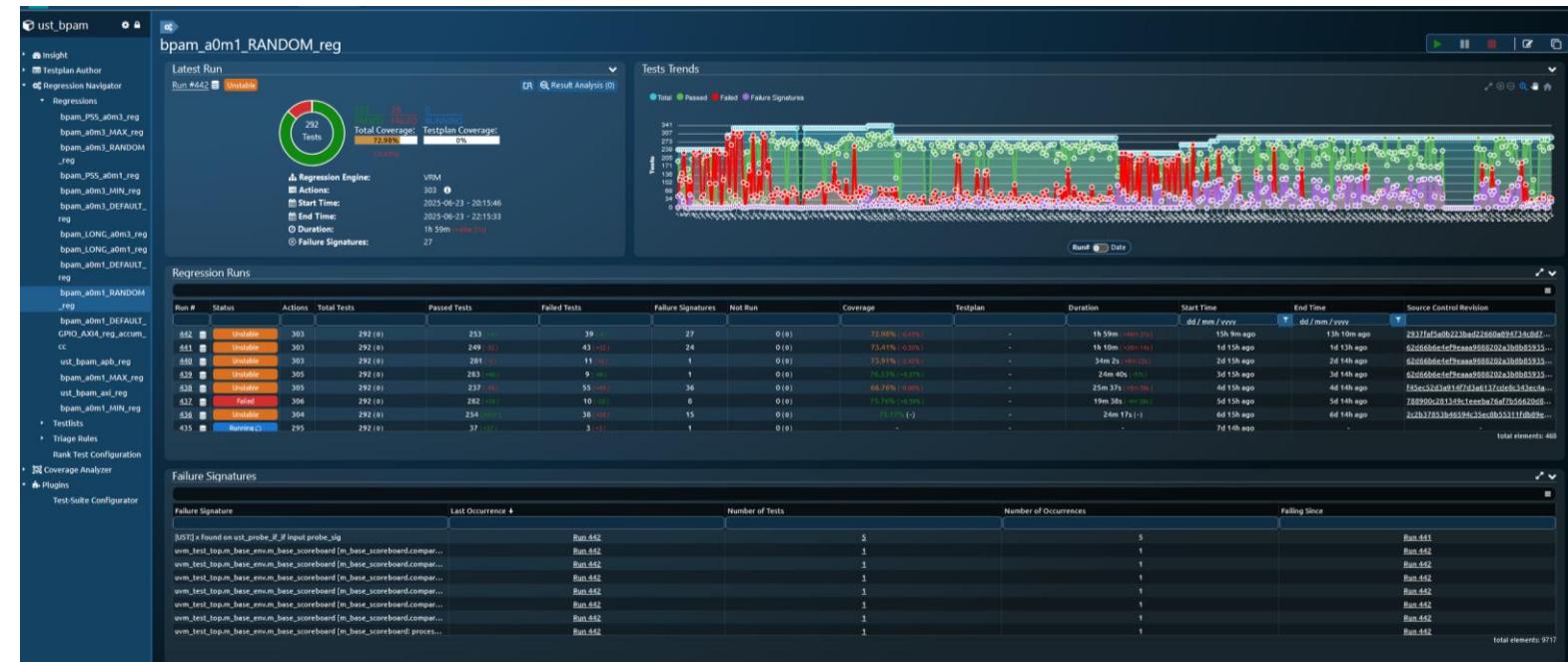

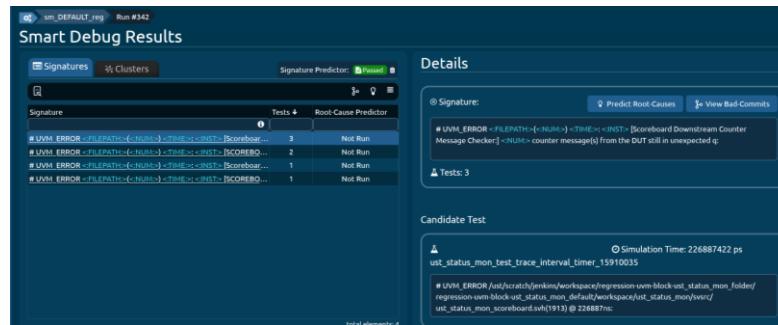

# Failure Signatures

- Automated data scraping

- View statistics on each failure message

| Failure Signatures                                                     |                         |

|------------------------------------------------------------------------|-------------------------|

| Failure Signature                                                      | Last Occurrence ↓       |

| [UST:] x Found on ust_probe_if_if input probe_sig                      | <a href="#">Run 442</a> |

| uvm_test_top.m_base_env.m_base_scoreboard [m_base_scoreboard.compar... | <a href="#">Run 442</a> |

- View failure log and run command with rand-seeds to rerun the same param config and test stimulus

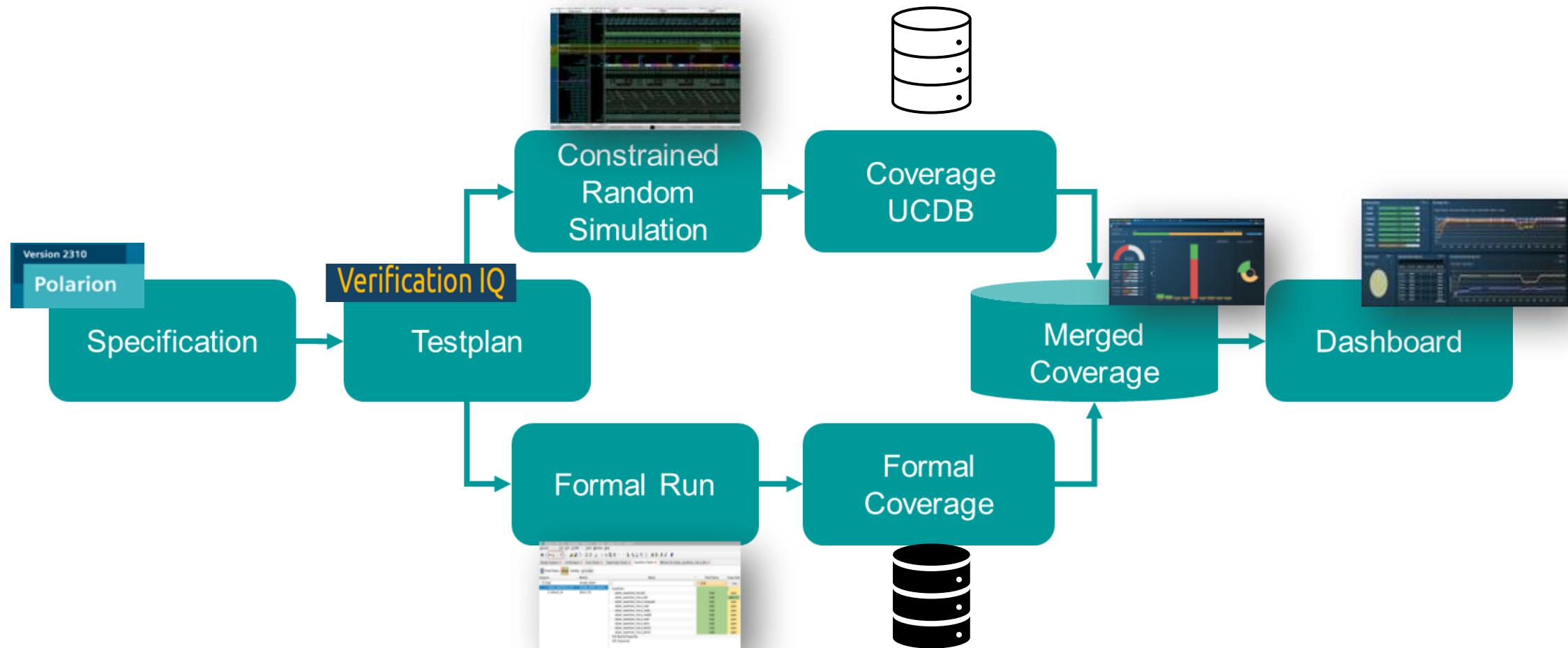

# Accumulated Coverage Structure

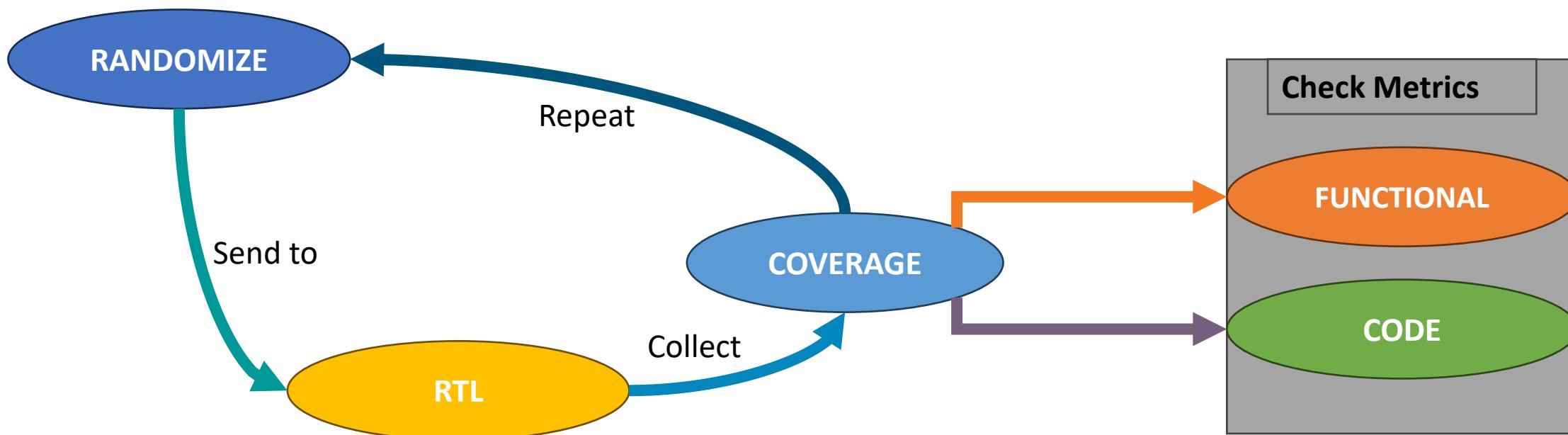

# Metric-Driven Verification (MDV)

- When should we use it?

- Sometimes, a system has too many possible inputs.

- Brute-force is not, therefore, an option.

- Metric-Driven Verification is based on RANDOMIZATION.

# Metric-Driven Verification (MDV)

- Collecting coverage for highly-configurable IPs require **robust strategy**.

- Using **automation tools** (e.g., Jenkins) is critical to success.

- Two different accumulation approaches will be explored.

- Accumulation is based on merging UCDB files.

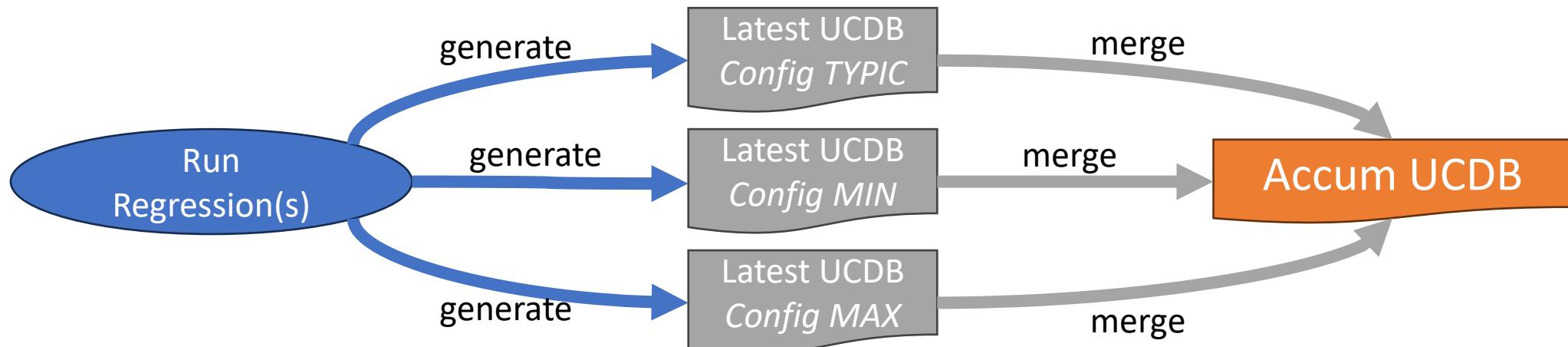

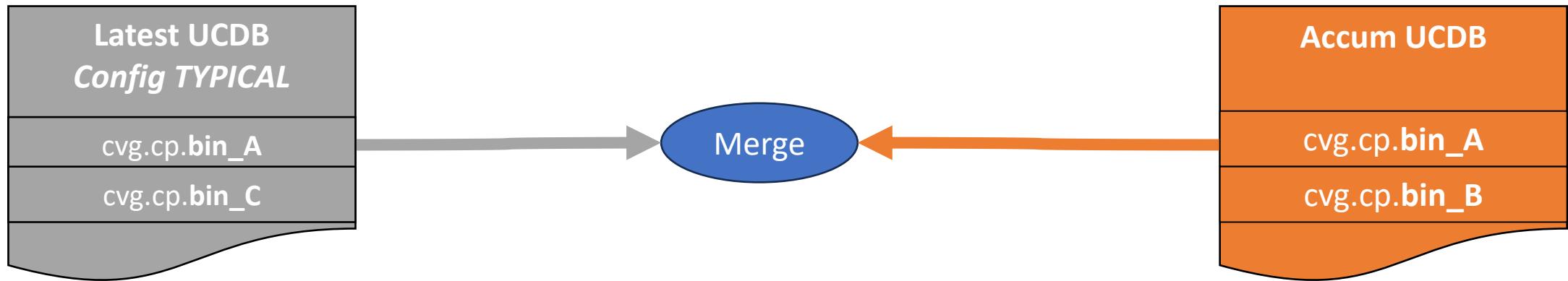

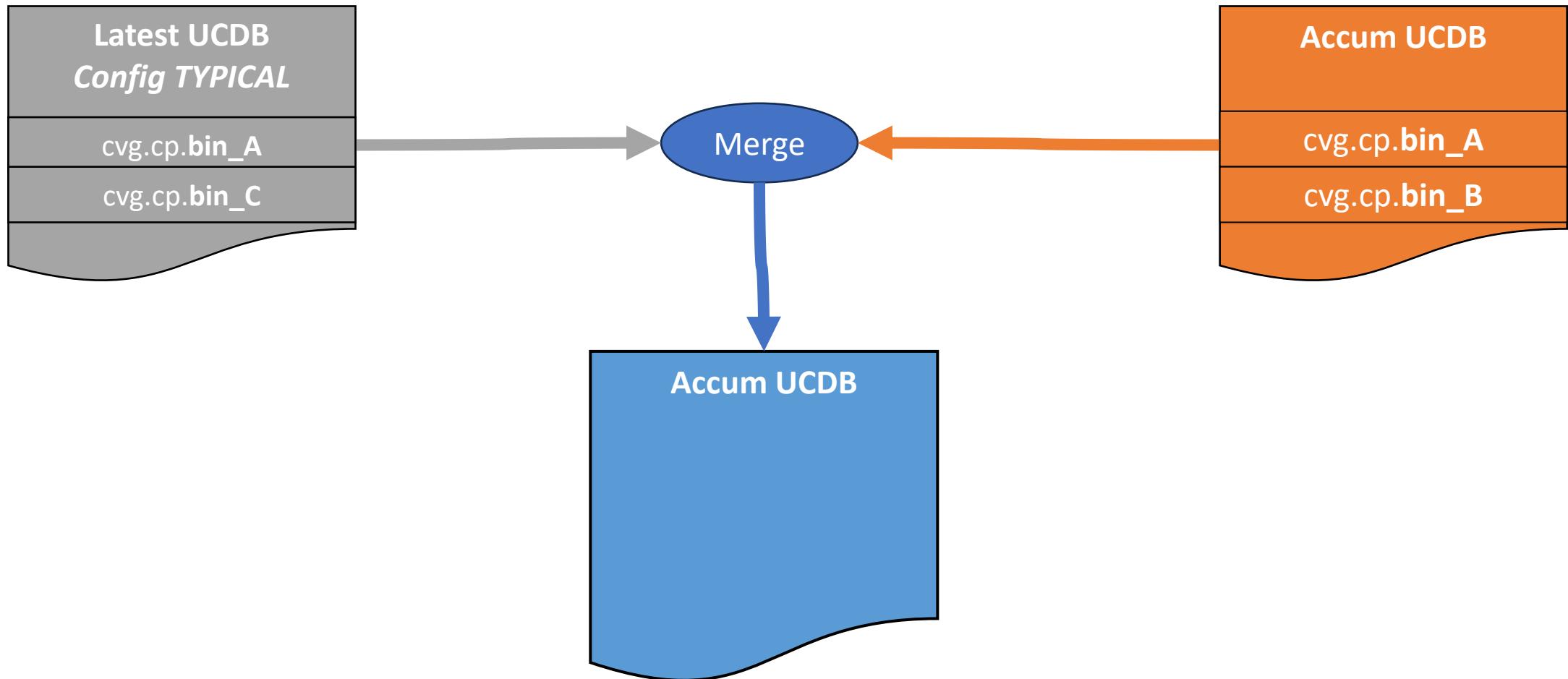

# Merging Strategy

# Merging Strategy

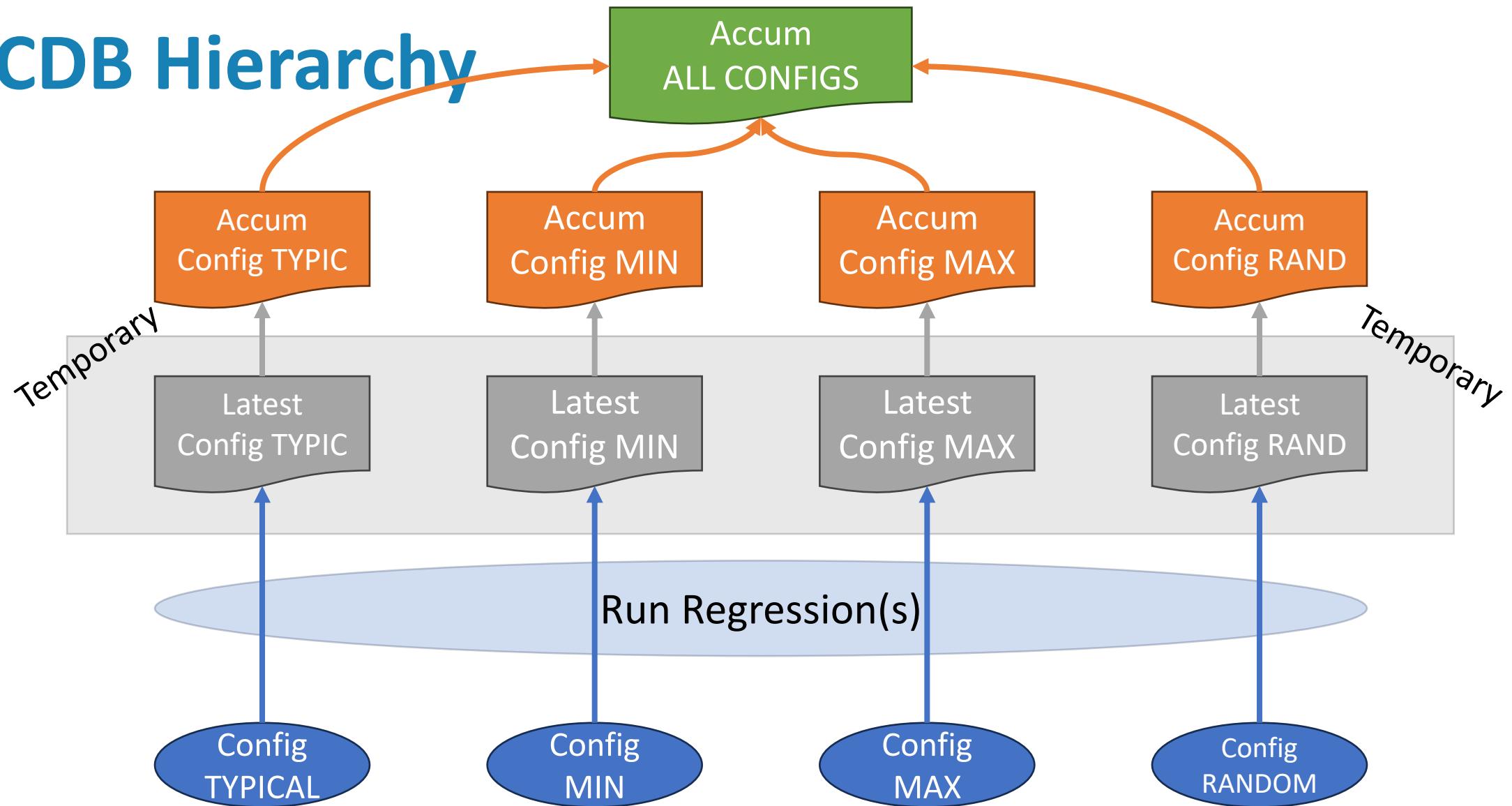

# UCDB Hierarchy

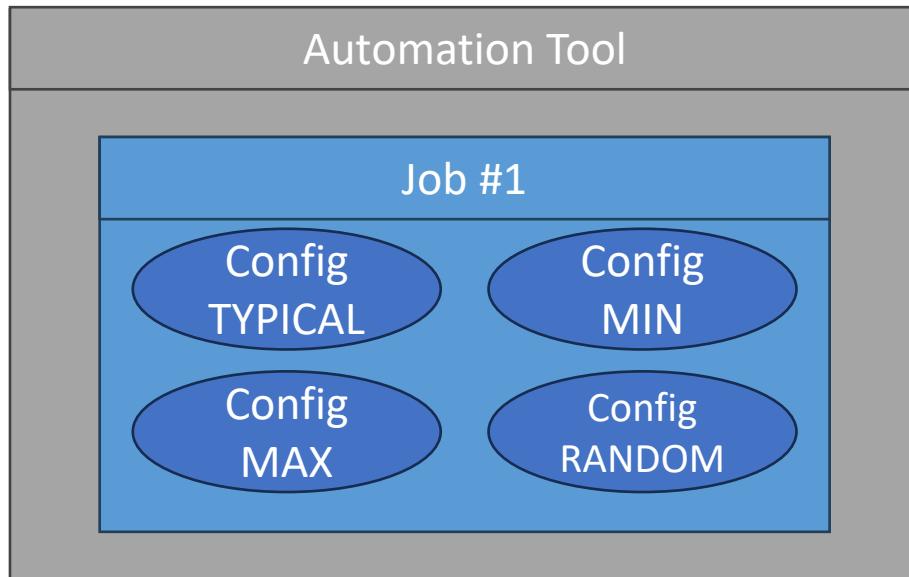

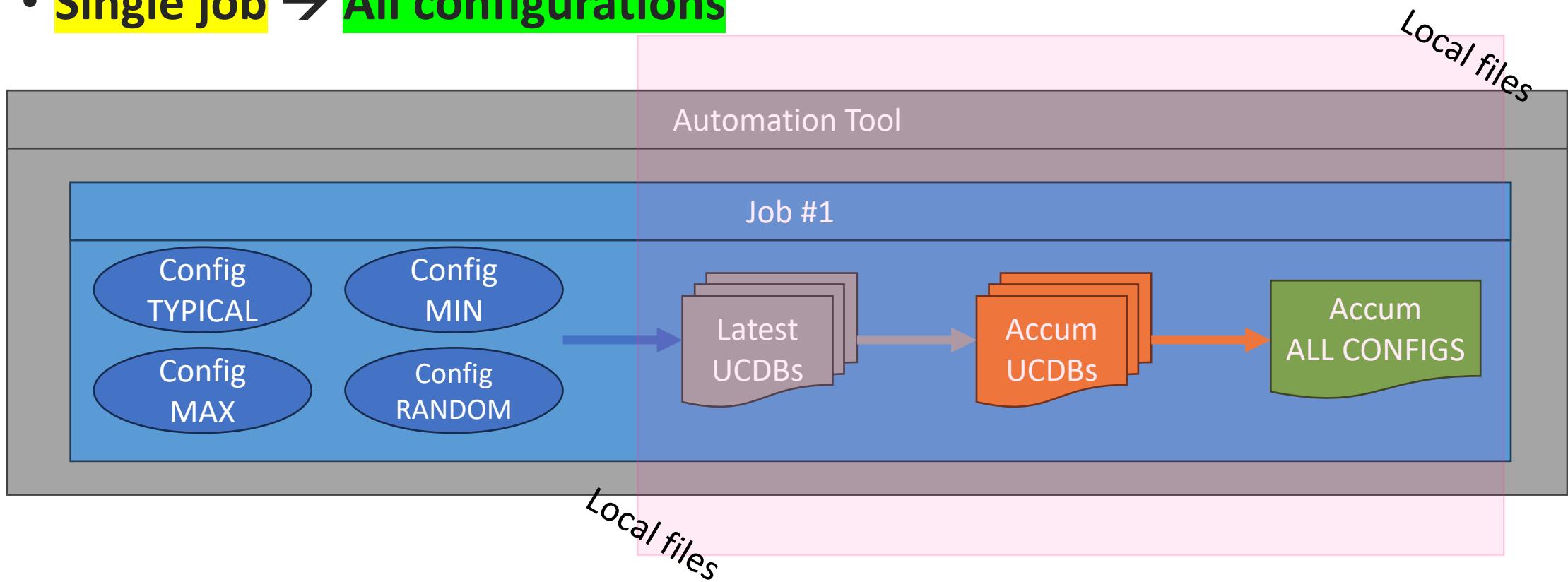

# Automation: Scenario 1

- Single job → All configurations

# Automation: Scenario 1

- Single job → All configurations

*Local files* → within a given job's workspace

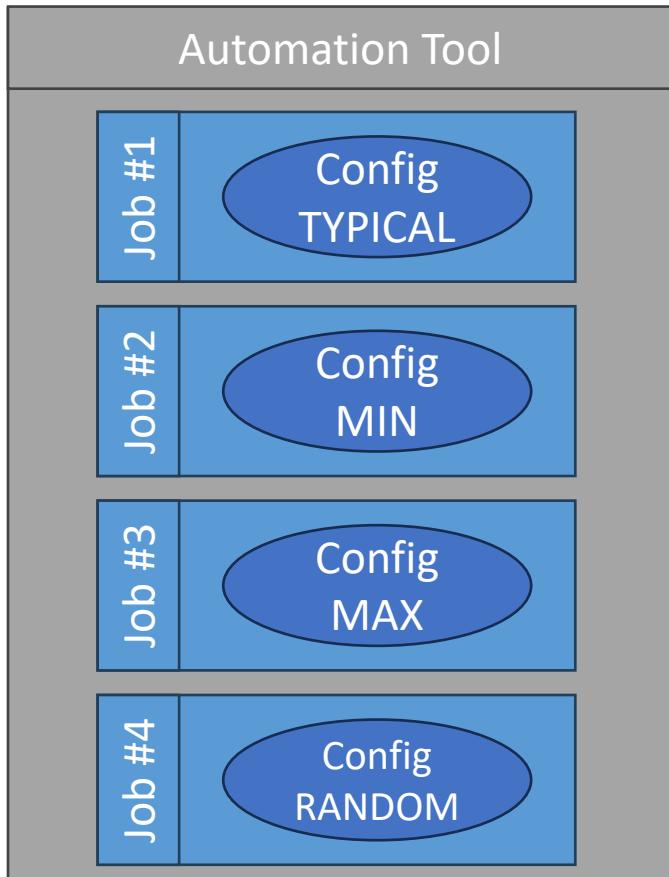

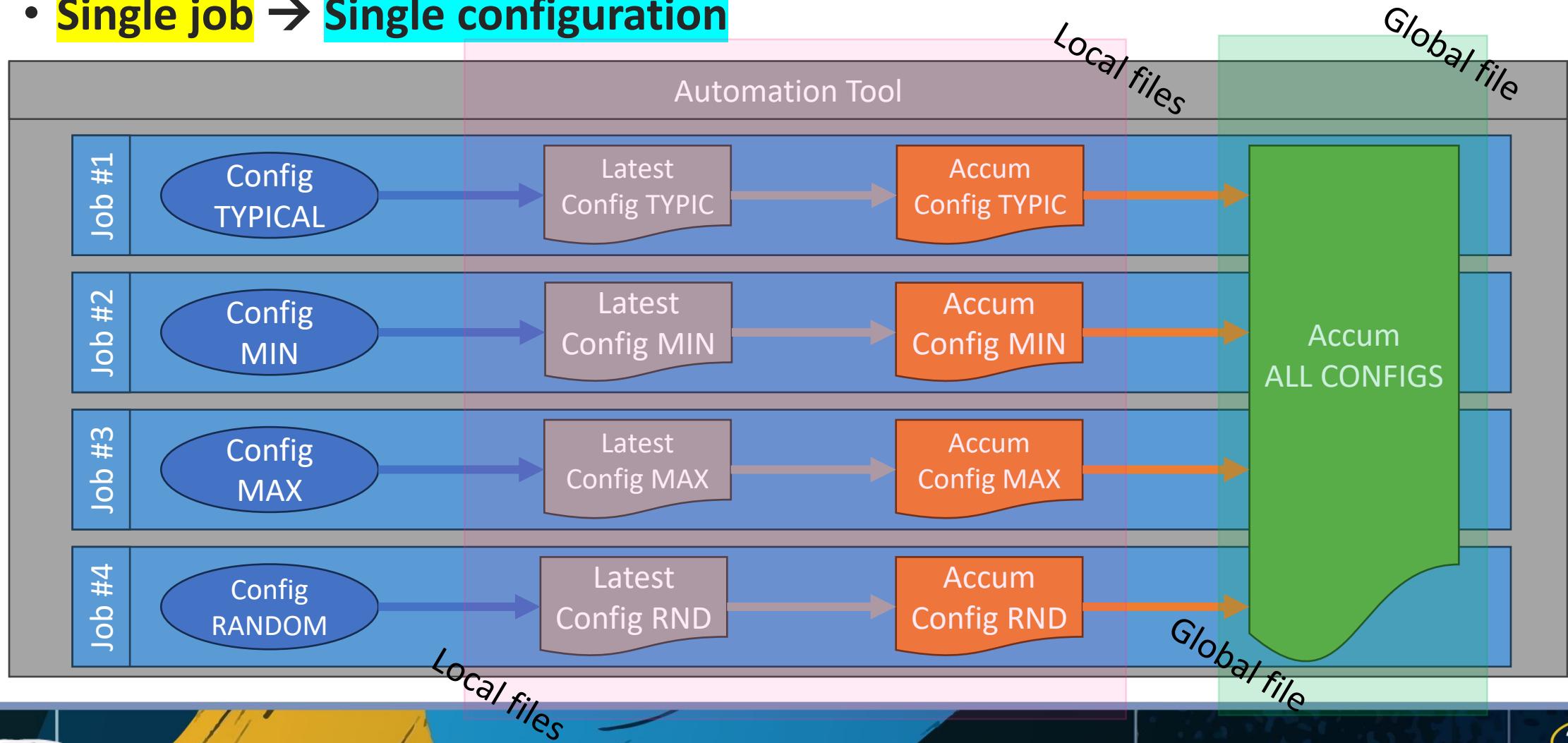

# Automation: Scenario 2

- Single job → Single configuration

# Automation: Scenario 2

*Local files* → within a given job's workspace

*Global files* → shared by multiple jobs

- Single job → Single configuration

# Considerations

- Choose the right accumulation path based on the structure.

- Analyze intermediary UCDBs as needed.

- Easily check how thoroughly the IP was verified using the ALL\_CONFIGS.

# Traffic Light System & Unreachability

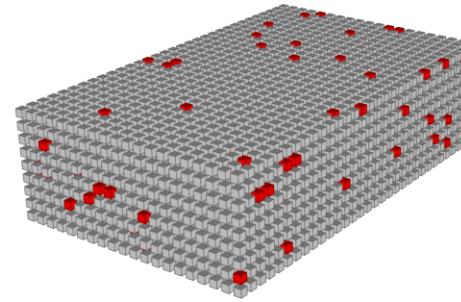

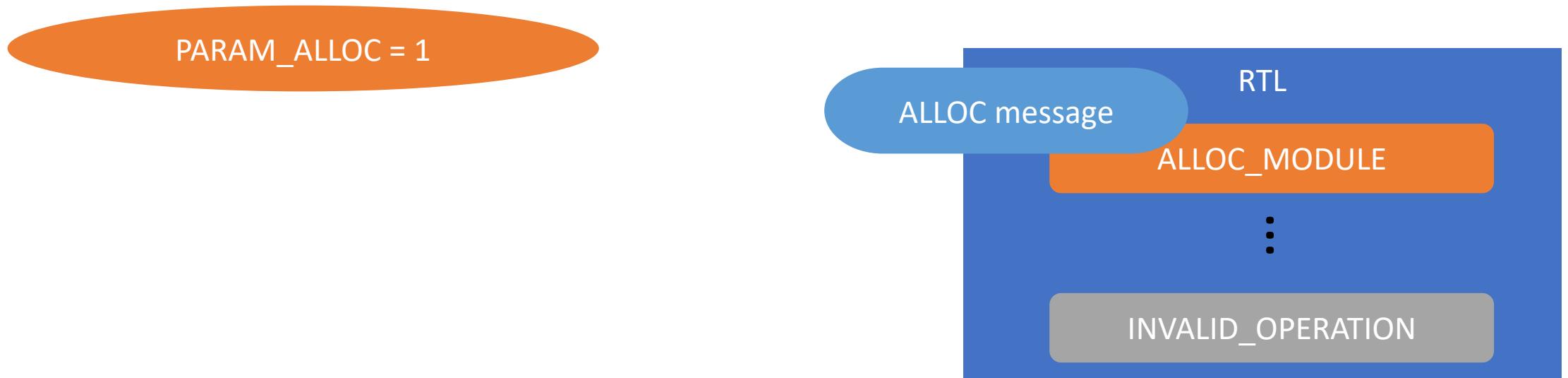

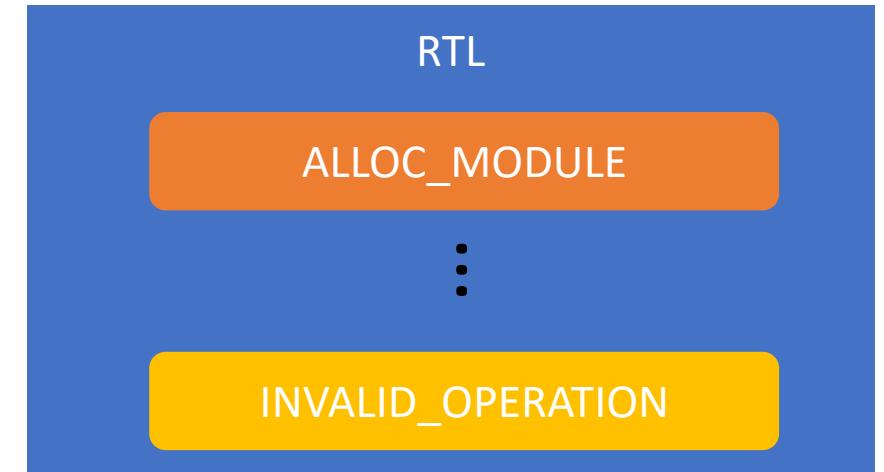

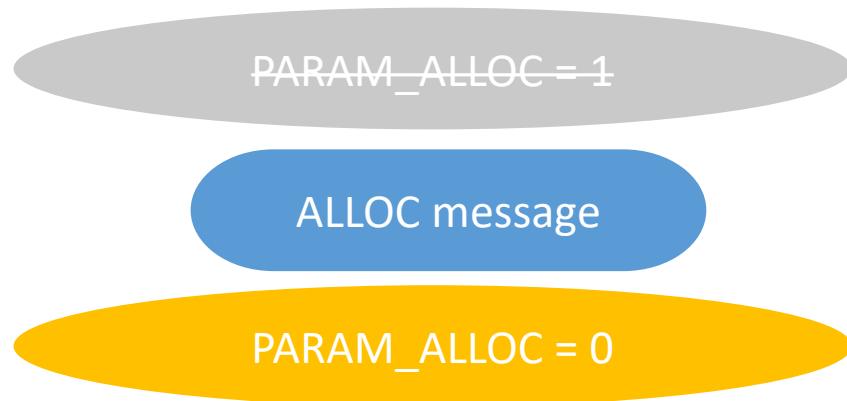

# Introduction

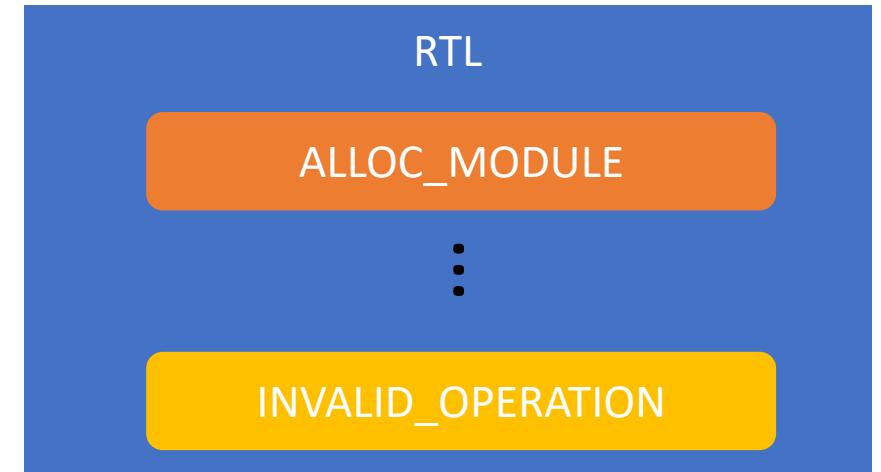

- In a world with **highly configurable IPs**, different parts of the RTL might be unreachable depending on the configuration.

# Introduction

- In a world with **highly configurable IPs**, different parts of the RTL might be unreachable depending on the configuration.

# Introduction

- In a world with **highly configurable IPs**, different parts of the RTL might be unreachable depending on the configuration.

# Introduction

- In a world with **highly configurable IPs**, different parts of the RTL might be unreachable depending on the configuration.

- With **PARAM\_ALLOC disabled**, `ALLOC_MODULE` can't be covered.

- **How to deal with that?**

# Traffic Light System: *Coverage Goals*

- Coverage collected both for function coverage and code coverage.

- Coverage target goals are:

- **100% Function Coverage**

- ❑ Upgraded methodology to be param aware.

- **100% “explained” Code coverage**

- ❑ Explained means there are waivers for unreachable code.

- **Why the Traffic Light System?**

- Allows for initial thorough analysis.

- Forces, on Red Waivers, to go back for more implementation/analysis.

# Traffic Light System

## Waiver classifications:

- **Red**

- Reachable, but untested

- Requires further attention.

- **Amber**

- Reachable, but only partly tested.

- High confidence it will be covered.

- **Might** require further attention.

- e.g., Cover Crosses (FC).

- **Green**

- Unreachable.

- Requires clear justification and reviews.

- Once accepted, no need for further attention.

- e.g., different configuration

# Traffic Light System: *Proposed methodology*

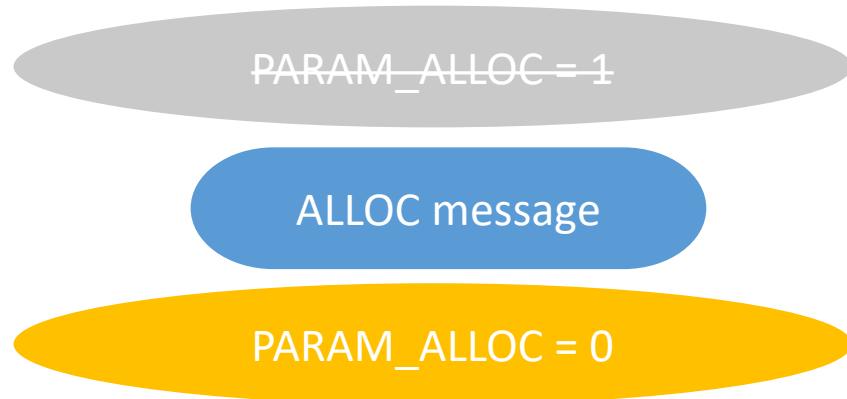

1. Look for coverage holes.

2. Analyze coverage holes.

3. Classify coverage holes.

4. Propose a classification (e.g., through JIRA).

5. Wait for the approval.

6. Exclude the items.

# Unreachability

- Formal Unreachability

- Mathematically unreachable.

- Formal Verification tools.

- Proposed Methodology:

1. Run unreachability analysis tool.

2. Analyze proposed exclusions.

3. Apply exclusions.

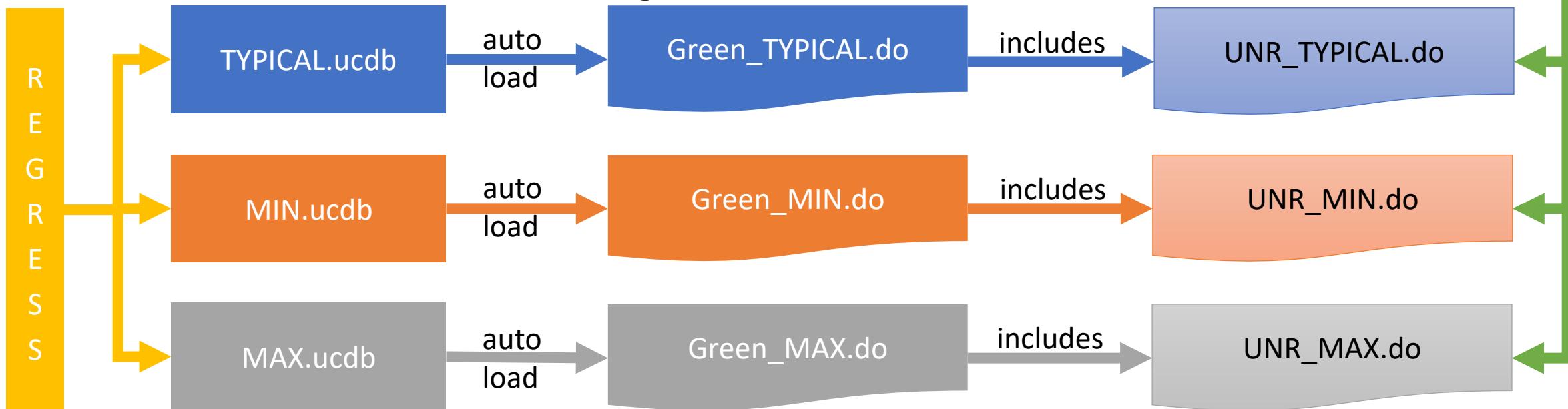

# Exclusions

Formal UNR Tool

(e.g. Questa CoverCheck)

- Traffic Light System + Unreachability → **Need for Exclusions!**

- How to manage exclusions?

- Assume 3 configurations: **CONFIG\_TYPICAL, CONFIG\_MIN, CONFIG\_MAX**

- Create exclusion files for each configuration.

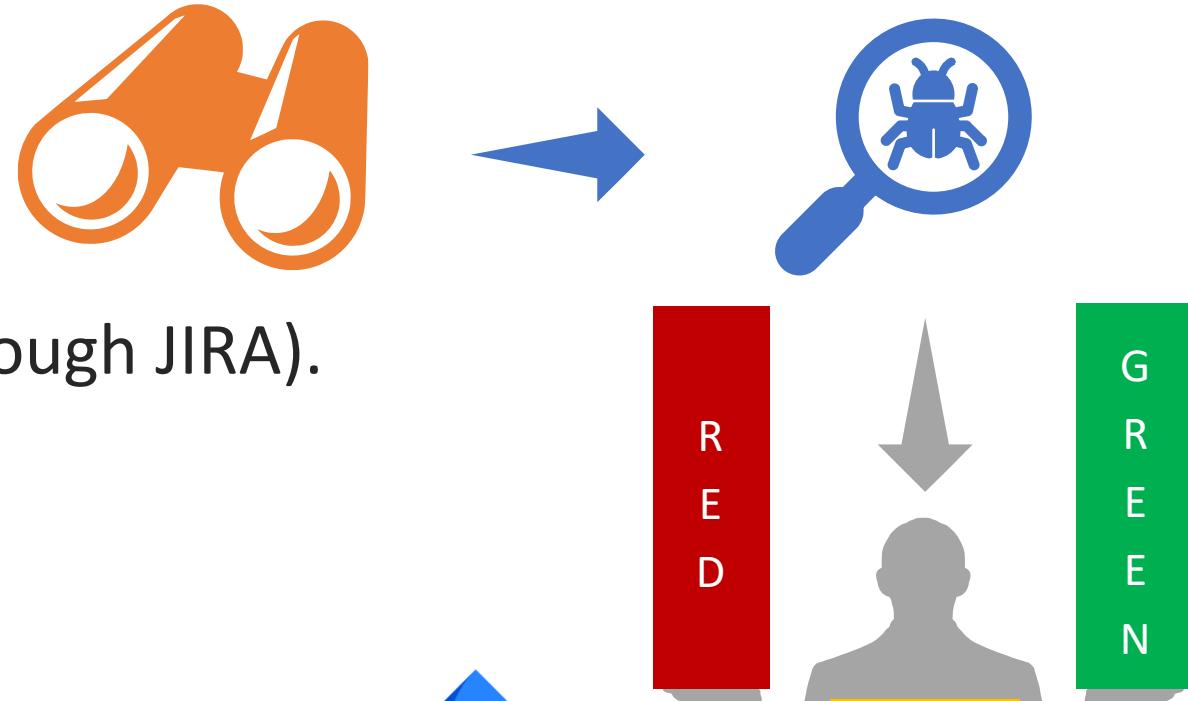

# Parameter-aware Functional Coverage

- Code Coverage can be excluded; **Functional Coverage shall not be for Green Waiver.**

- Introducing **Parameter-aware Functional Coverage**:

- Create auto-excluding Covergroups, Coverpoints and Bins based on parameters.

- Covergroups → `if (<COND>) cvg = new("name");`

- Coverpoints:

`option.weight = (<COND>);`

`option.at_least = (<COND>);`

`type_option.weight = (<COND>);`

- Bins → `bins b_A = {'h0} with (<COND>);`

What if

`option.per_instance = 1?`

# RANDOM Configuration

- Randomize all parameters → Allows for covering all possible configurations over time.

- Addition of **COV\_ALL** flag.

- No parameter-aware in RANDOM → We need to see coverage holes.

- Add **covergroup** for parameters.

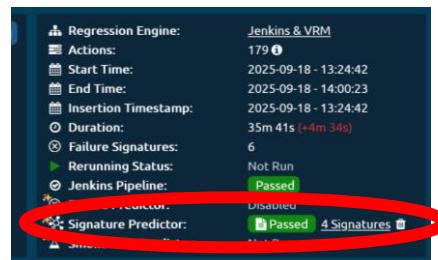

# Collaborative Work – Coverage Analyzer (VIQ)

- VIQ offers a collaborative work environment to analyze and manage coverage.

- It also keeps track of testplans merged into coverage files

# Considerations

- For **Code Coverage**, well-maintained Exclusions are the key to success.

- For **Functional Coverage**, well-designed parameter-aware covergroups shall expedite verification.

# Real-time and Interactive Dashboards

# Dashboards

## ASIC Verification Complexity

- Highly configurable IPs require verification across **multiple configurations**

- Leads to **exponential growth** in verification effort (almost infinite permutations)

- Managing diverse configurations and variants creates significant data challenges

- Need for **data-driven decision making** thus super important to present this data in a concise and meaningful way.

- Crucial that data is accurate and Real-Time

# Type of Metrics

Regression Pass /

Fail Status

Code and Function

Coverage

Bug tracking

system statistics

Specifications /

requirements

items

Verification plan

items

Repository

statistics

Compute

resources metrics

(CPU, Memory etc)

Test/regression

resource statistics

(e.g. run time)

# Challenges Without Real-Time Dashboards

- **Delayed insights** into verification progress and issues

- **Manual collection and correlation** of metrics across configurations can lead into misinterpretation

- **Reactive rather than proactive** issue detection

- **Siloed information** between teams and verification stages

- Can lead to **stale data** very quickly

- **Time-consuming** report generation and analysis

# Benefits of Real-Time & Interactive Dashboards

- Immediate visibility into verification progress

- Early bug detection and trend analysis

- Resource optimization and management

- Comprehensive coverage tracking across configurations

- Data-driven decision making

- Efficient generation of verification health reports.

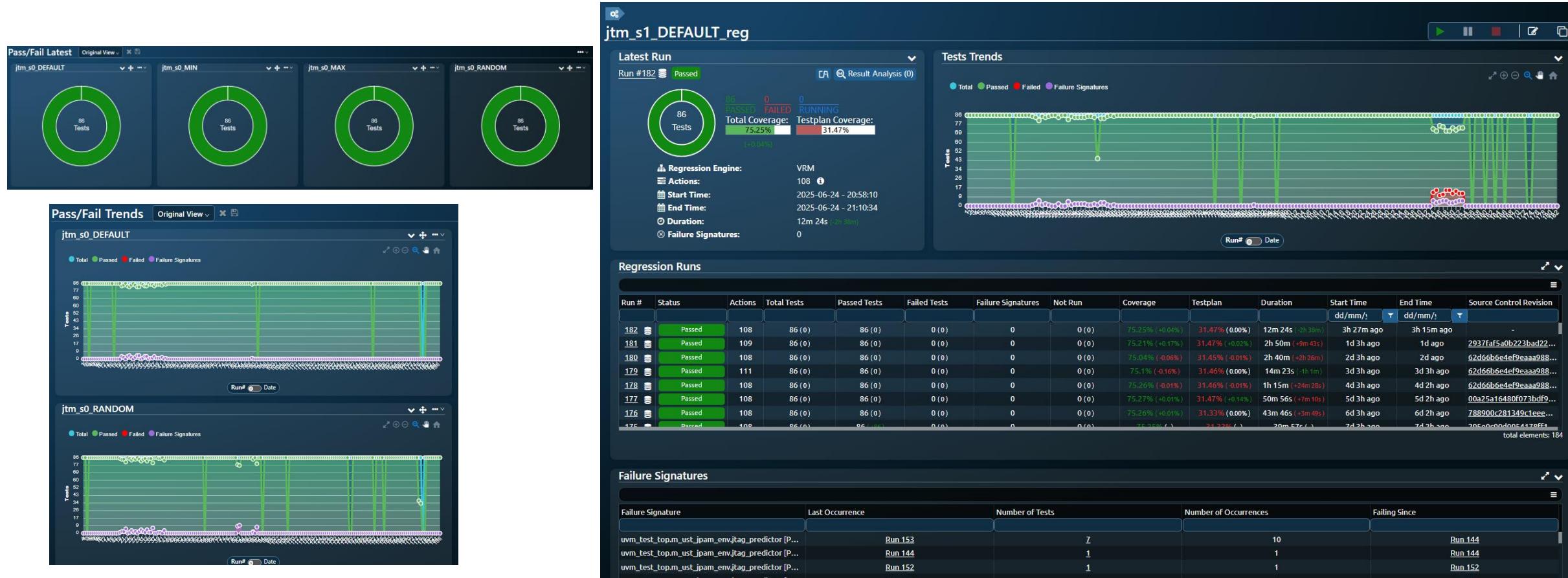

# Benefit 1: Immediate Visibility

- **At-a-glance** “health status” overview of design and verification

- **Real-time status** across all regression runs and configurations

- **Aggregated view** of pass/fail metrics across variants and also coverage

- **Immediate feedback** on new test additions or code changes

- Better understanding of **verification bottlenecks**

# Benefit 1: Immediate Visibility

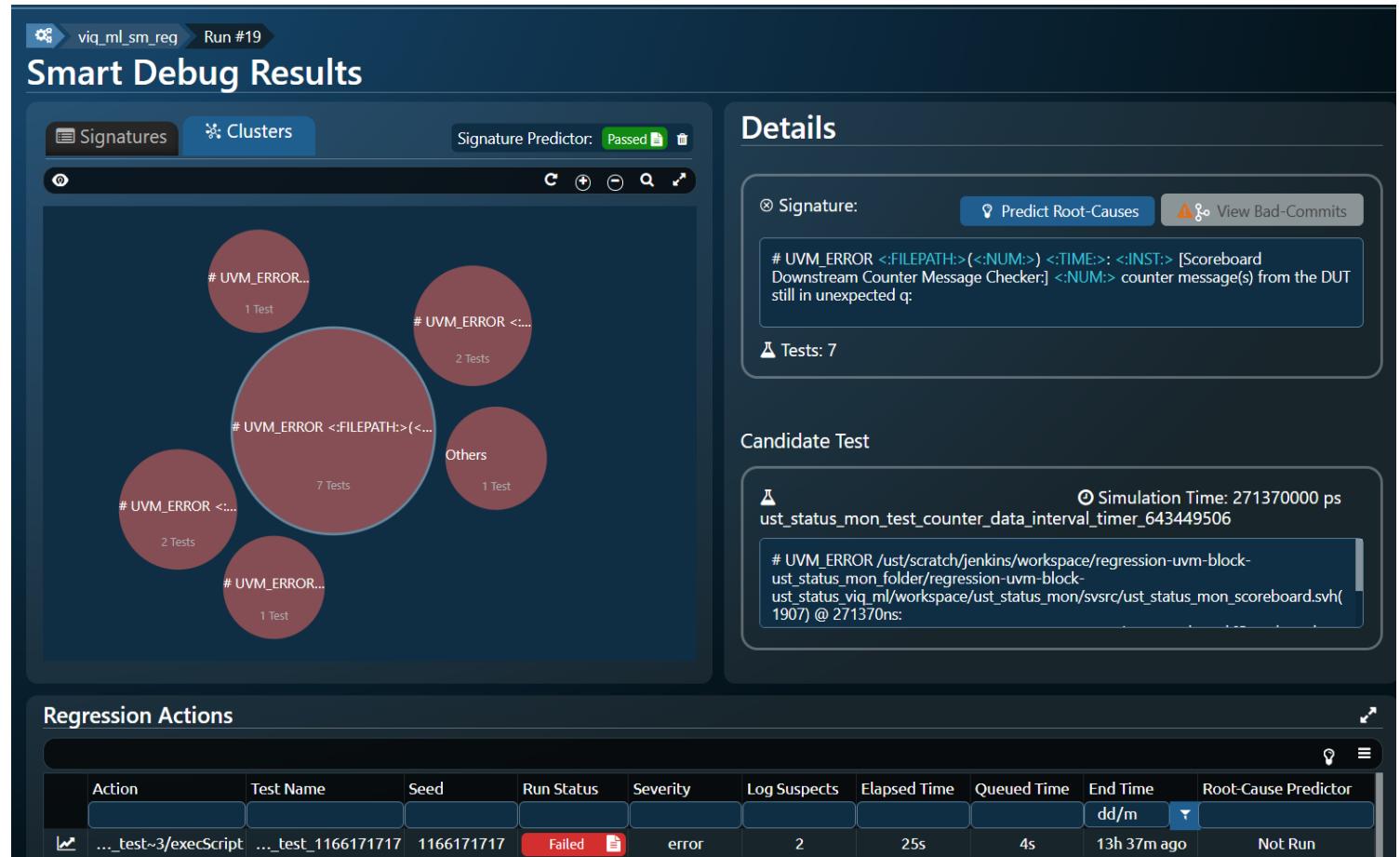

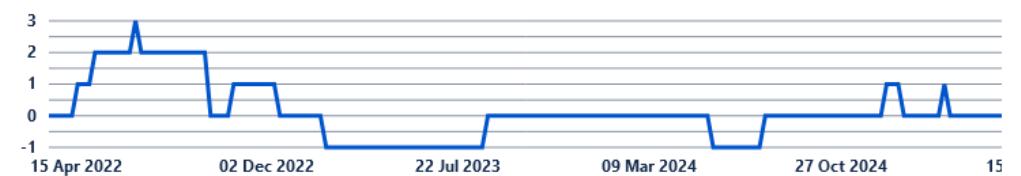

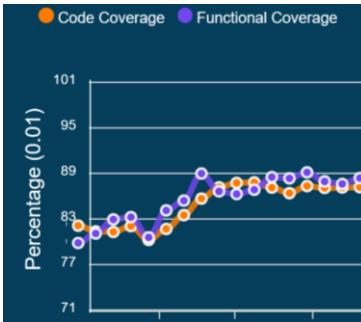

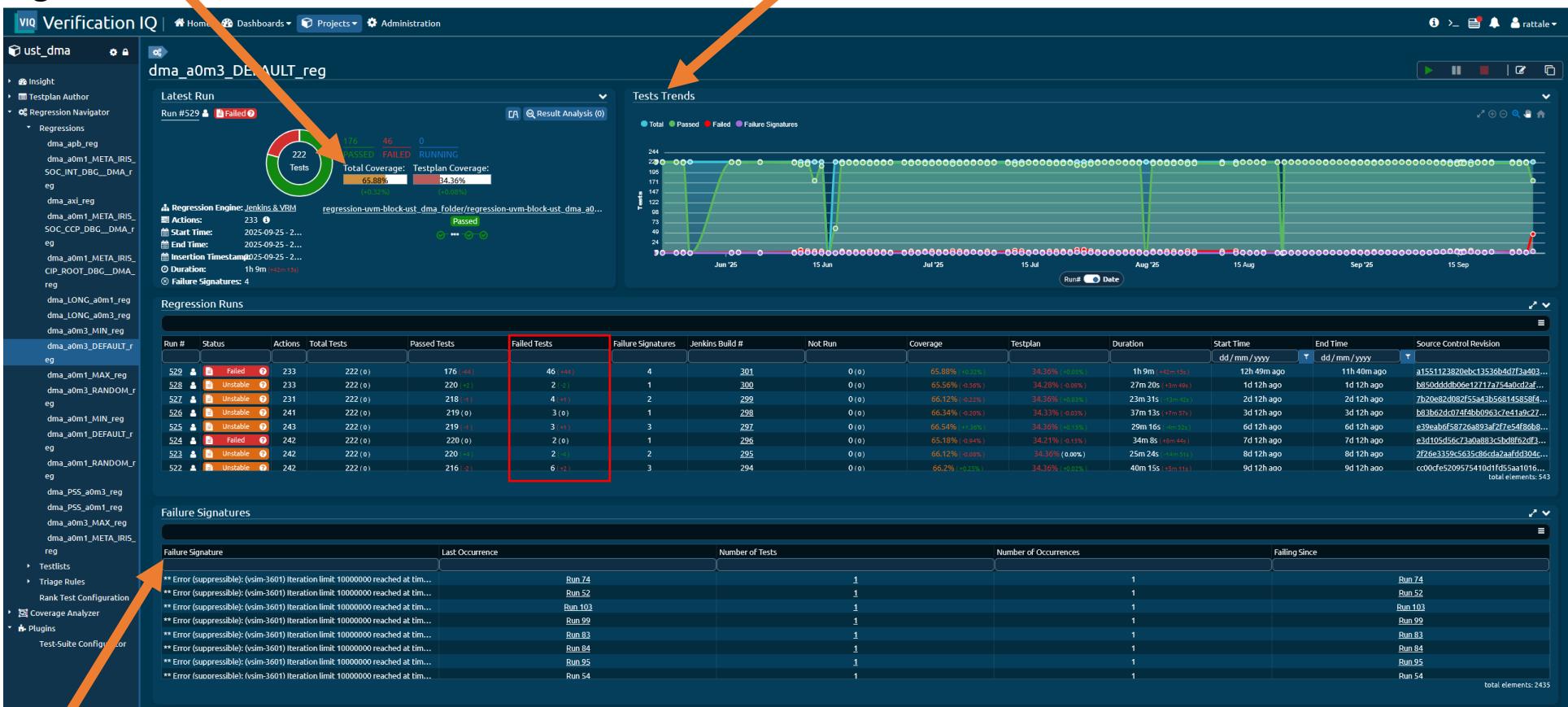

# Benefit 2: Early Bug Detection

- Live bug convergence trends highlight potential issues early

- Interactive bug curves allow drill-down into problematic areas

- Cross-configuration bug correlation identifies systemic issues

- Predictive analytics for forecasting time to verification closure

# Benefit 2: Early Bug Detection

# Benefit 2: Early Bug Detection (2)

- Smart debug - > Using ML to triage and identify candidate tests to debug.

- Speeds up debug cycles helping in earlier bug detection.

# Benefit 3: Comprehensive Coverage Tracking

- **Real-time coverage metrics** across all configurations and all coverage types

- **Interactive coverage** linked and annotated directly to testplan items

- **Gap analysis** between configurations highlights untested scenarios

- **Coverage progression tracking** shows verification maturity over time

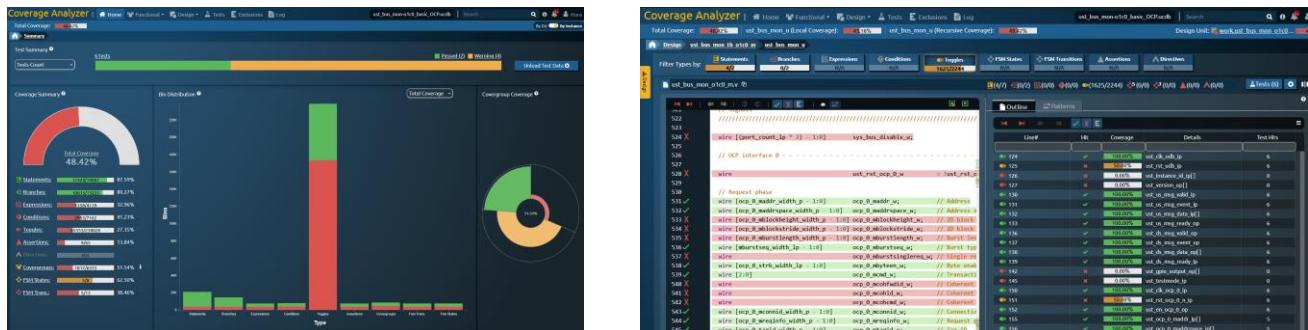

# Benefit 4: Resource Optimization

- **CPU / Memory utilization tracking** across all tests to identify performance anomalies

- **Test runtime analysis** to identify inefficient simulations

- **Regression execution patterns** reveal infrastructure bottlenecks

# Benefit 5: Data-Driven Decision Making

- **Actionable insights** rather than raw data

- **Interactive filtering** to isolate specific issues or configurations

- **Custom views** for different stakeholders (managers, engineers, leads)

- **Historical trend analysis** for continuous process improvement

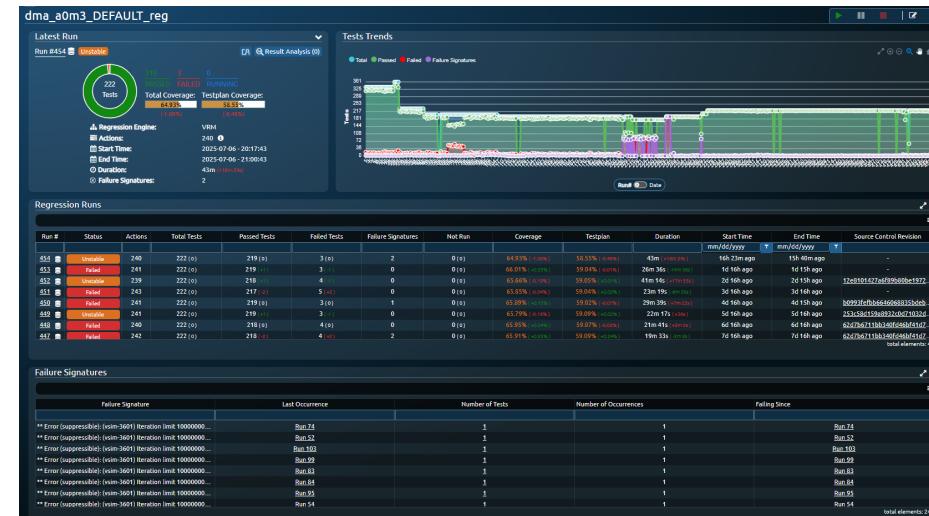

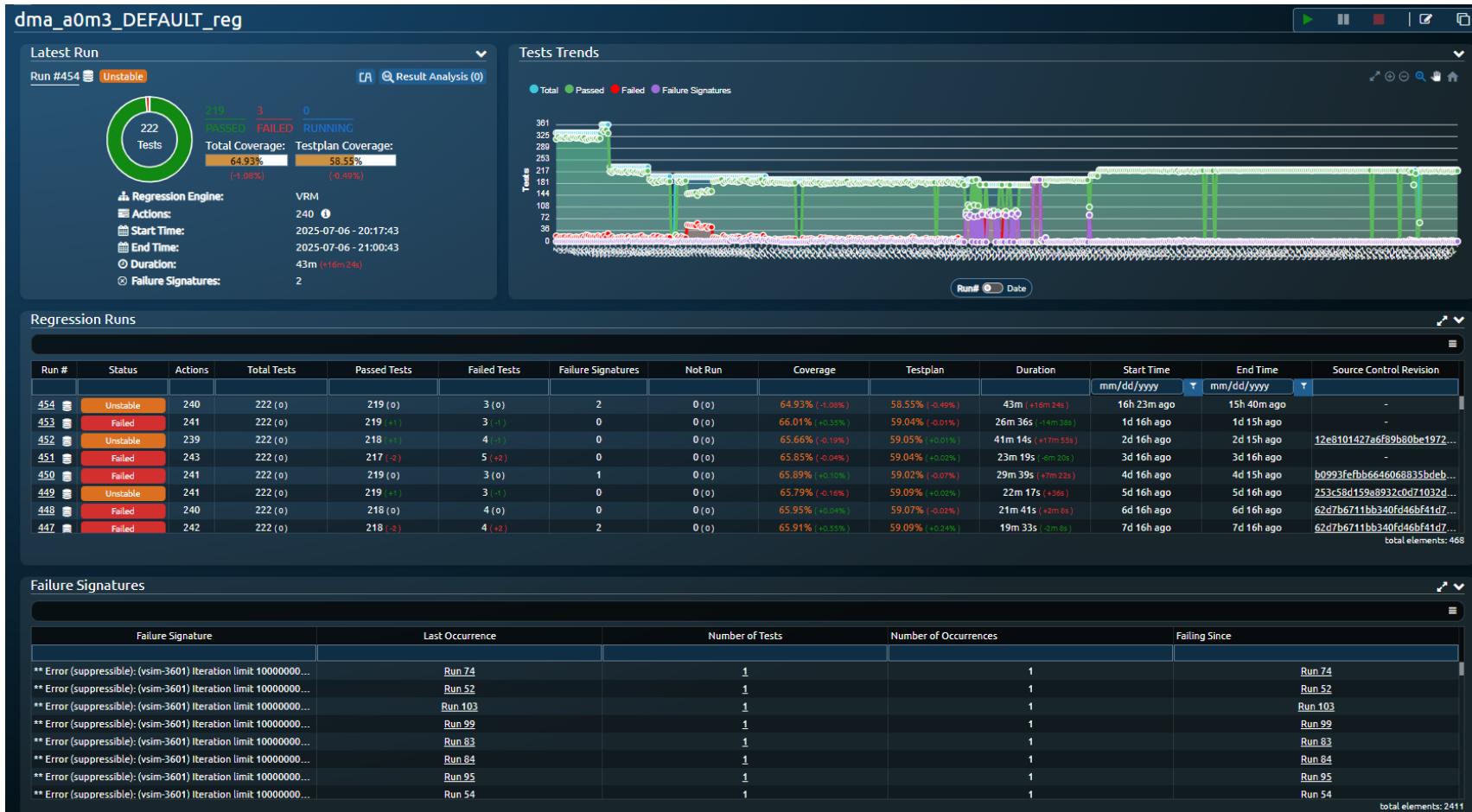

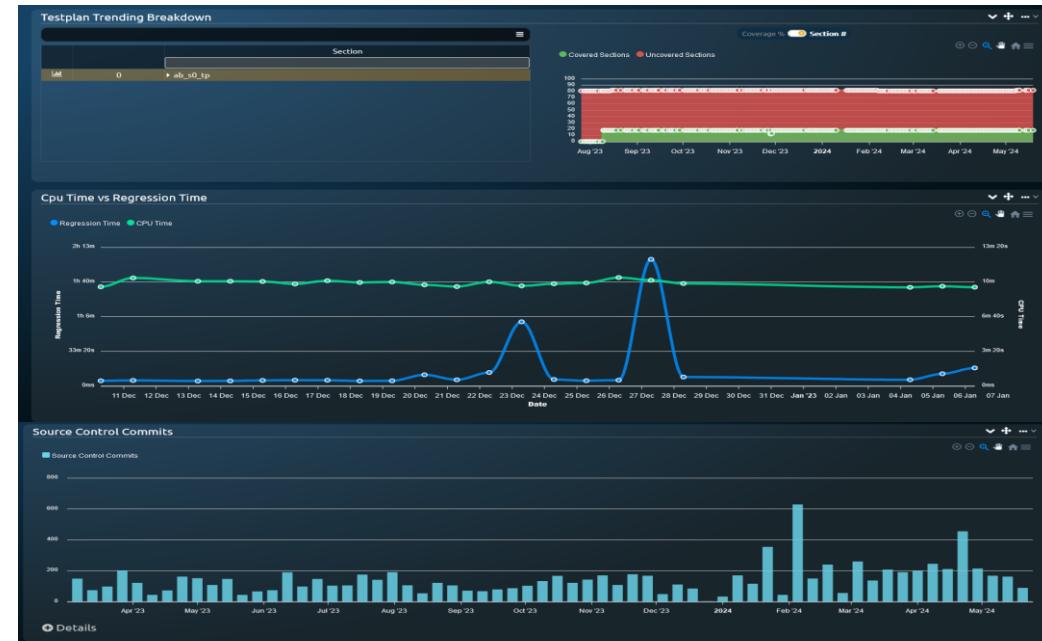

# Tessent Embedded Analytics Dashboard (1)

- Use Questa Verification IQ (VIQ) extensively for verification management and dashboarding

- Various metrics: regression status, coverage scores, database stability, CPU runtimes, etc.

- Each IP has separate Hierarchical dashboard per variant and configuration.

# Tessent Embedded Analytics Dashboard (2)

# Requirement Traceability Dashboards

- 01** **RTL Implementation**

Requirements linked to the actual RTL implementation e.g. VHDL, Verilog using pragmas.

- 02** **Test Plan**

Requirements linked to the Test Plan.

- 03** **Coverage Results**

Shows coverage number for each test plan items that the requirements are linked to.

# Bug / Issue Tracking

- Using JIRA for issue/bug tracking

- Will integrate with Verification Management tool

Issues in the last 1,200 days (grouped weekly) [View in Issue Navigator](#)

● Created issues (9)

● Resolved issues (9)

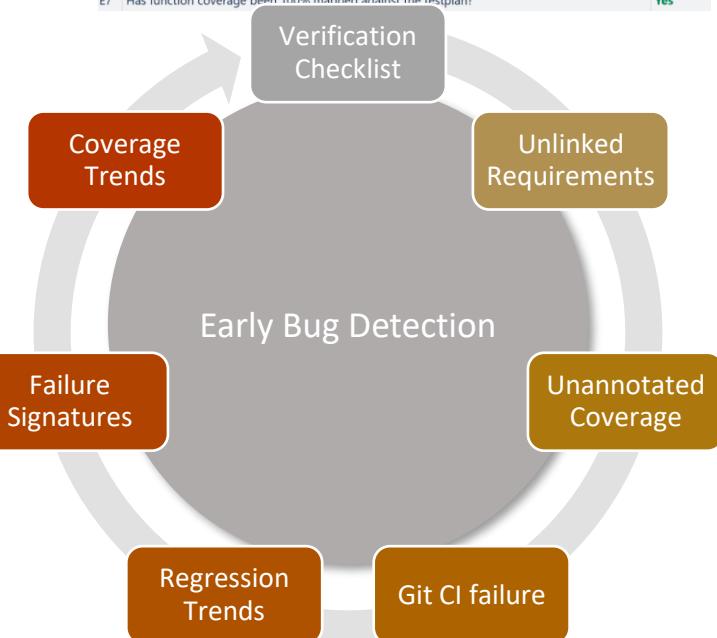

# Early Bug Detection

# How our coverage and dashboards help

TO FIND BUGS EARLY –

SPECIALY DURING THE

PRE-SILICON STAGE

CREATE ROBUST DESIGNS

– HIGH QUALITY DESIGN

DEVELOPMENT TIME IS

FASTER

BETTER RELATIONSHIP

WITH CUSTOMERS

# Early Indicators of Bugs

|    |                                                                                                                      |     |

|----|----------------------------------------------------------------------------------------------------------------------|-----|

| E1 | Has the spec been reviewed and approved and a baseline created?                                                      | Yes |

| E2 | Has the testplan been reviewed against spec and 100% of requirements mapped?                                         | Yes |

| E3 | Have all known tests (as per testplan) been implemented?                                                             | Yes |

| E4 | Have all known tests (as per testplan) been passing?                                                                 | No  |

| E5 | Have all bugs been documented in JIRA and closed?<br><i>[If there are any deferred bugs, please provide details]</i> | Yes |

| E6 | Has function coverage been implemented?                                                                              | Yes |

| E7 | Has function coverage been 100% mapped against the testplan?                                                         | Yes |

| Failure Signature                                                               | Last Occurrence |

|---------------------------------------------------------------------------------|-----------------|

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 74          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 52          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 103         |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 99          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 83          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 84          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 95          |

| ** Error (suppressible): (vsim-3601) iteration limit 10000000 reached at tim... | Run 54          |

|           |                                            |         |

|-----------|--------------------------------------------|---------|

| ▶ 1.1.1.3 | Clock Domain Crossing                      | 100.00% |

| ▶ 1.1.2   | AXI Interface                              | 100.00% |

| ▶ 1.2     | Features                                   | 93.71%  |

| ▶ 1.3     | Testcases                                  | E       |

| ▶ 2       | Downstream EBC (ebc_tp_downstream_virtual) | 100.00% |

| ▶ 3       | Upstream EBC (ebc_tp_upstream_virtual)     | 100.00% |

Pipeline #21069 failed

Pipeline failed for 4f0b47ec on clockgen\_checker 1 week ago

# Verification checklists

- Final link in the methodology

- Created early in the development process of the release

- Completed prior to code freeze

- Reviewed and approved prior to release

- Captures all aspects of the methodology

- Progress bar in Jira is used to track checklist

| #   | Question                                                                                                                     | Response | Comment |

|-----|------------------------------------------------------------------------------------------------------------------------------|----------|---------|

| E1  | Has the spec in Reviewed and Approved and a baseline created?                                                                |          |         |

| E2  | Has the <u>testplan</u> been reviewed against spec and 100% of requirements mapped?                                          |          |         |

| E3  | Have all known tests (as per <u>testplan</u> ) been implemented?                                                             |          |         |

| E4  | Have all known tests (as per <u>testplan</u> ) been passing?                                                                 |          |         |

| E5  | Have all bugs been documented in <u>JIRA</u> and closed?<br><i>[If there are any deferred bugs, please provide details ]</i> |          |         |

| E6  | Has function coverage been implemented?                                                                                      |          |         |

| E7  | Has function coverage been 100% mapped against the <u>testplan</u> ?                                                         |          |         |

| E8  | Has the <u>testplan</u> been annotated against coverage?                                                                     |          |         |

| E9  | Has the <u>testplan</u> been achieved 100% coverage?                                                                         |          |         |

| E10 | Is code coverage (block, toggle, expression, <u>FSM</u> ) 100% "explained". (i.e with all waivers applied)?                  |          |         |

| Version      | Status   | Progress                                                         | Start date <small> ⓘ</small> | Release date <small> ⓘ</small> |

|--------------|----------|------------------------------------------------------------------|------------------------------|--------------------------------|

| SM 10.2      | RELEASED | <div style="width: 100%;"><div style="width: 100%;"></div></div> | 03/Apr/25                    |                                |

| SIP 2025.1.1 | RELEASED | <div style="width: 100%;"><div style="width: 100%;"></div></div> | 07/Apr/25                    |                                |

| ETE 15.1.2   | RELEASED | <div style="width: 100%;"><div style="width: 100%;"></div></div> | 28/Jan/25                    |                                |

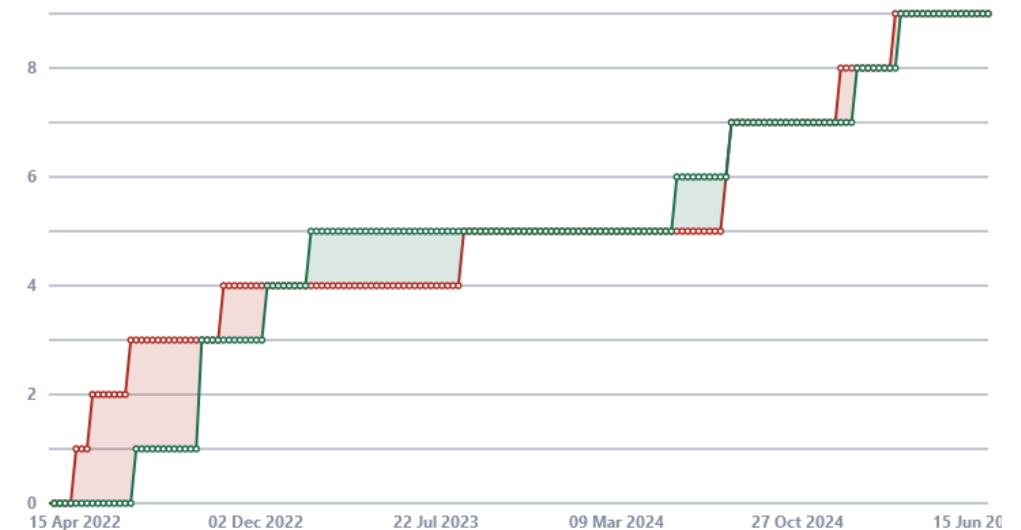

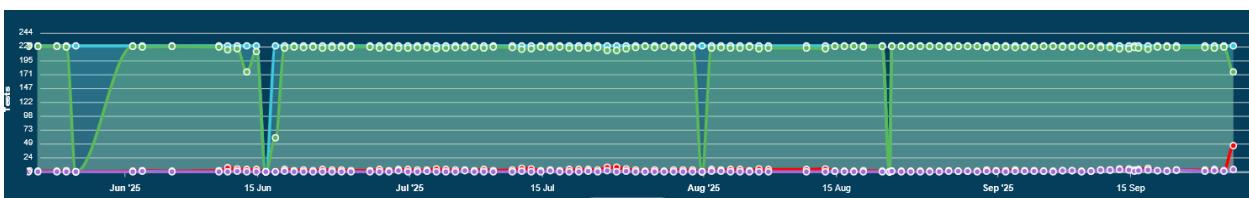

# Regression Trends & Failing Signatures

Coverage rate for the regression

Pass/fail trends of the regressions

Error messages seen in the regression

# Coverage Trends

Helpful to identify which areas of the code is untested

Fluctuations in coverage can help identify bugs

# Summary

**Automated & Configurable Flow:** Manages complex IP verification with cross-platform automation.

**Real-time Visibility:** Interactive dashboards enable early bug detection and data-driven decisions.

**Enhanced Coverage:** "Traffic Light System" for parameter-aware functional coverage.

**Integrated Traceability:** Seamless collaboration via JIRA and requirement management integration.

**Optimized Resources:** Monitors usage (CPU/memory, runtime) for efficiency.

**Efficient Techniques:** Leverages randomization, coverage merging, and automated data extraction.

# Questions?