#### **FIRST DVCON IN TAIWAN!**

# WELCOME TO DVCON TAIWAN

#### 2023-09-07 – <u>NYCU, HSINCHU</u>

#### 新竹陽明交通大學電資大樓

Congratulations & Thank You to the Organizers & Participants

**Synopsys**°

## **SYNOPSYS**<sup>®</sup>

## Autonomous Verification: Are We There Yet?

Ajay Singh SVP of Engineering, Design Creation & Verification

#### **Question for ChatGPT**

#### What is Autonomous Verification?

CODIN

"Autonomous Verification refers to the process of automatically verifying and validating systems, software or components *without significant human intervention*. It involves utilizing automated tools, algorithms, or systems to assess the correctness, performance, safety, or compliance of a particular entity or process..."

3

#### Robotaxi expansion gets green light in San Francisco

() 11 August

**AUTONOMOUS TAXI**

Road 1

85

SPEED LIMIT 90 ON CONTROL 2 St

#### Autonomous Taxis Are Here Today

#### LEVELS OF DRIVING AUTOMATION

| driving tasks task (e.g cruise tasks, but Human tasks, but Human tasks, but Human tasks under specific tasks without any               | 0                | 1                                       | 2                                                                            | 3                                                             | 4                                                                                   | 5                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| performs all the<br>driving tasks<br>control)<br>multiple automated<br>tasks, but Human<br>involvement is<br>needed for other<br>tasks |                  |                                         |                                                                              |                                                               | •                                                                                   |                                                                 |

|                                                                                                                                        | performs all the | a single automated<br>task ( e.g cruise | multiple automated<br>tasks, but Human<br>involvement is<br>needed for other | perform most driving<br>tasks, but Human<br>override is still | performs all driving<br>tasks under specific<br>circumstances.<br>Human override is | performs all driving<br>tasks without any<br>Human intervention |

The Human monitors the driving environment

The Vehicle monitors the driving environment

### LEVELS OF VERIFICATION AUTOMATION

| 0                                                   | 1                                                                                           | 2                                                                                                          | 3                                                                                              | 4                                                                                                                | 5                                                                                                |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| No                                                  | Engineer                                                                                    | Partial                                                                                                    | Conditional                                                                                    | High                                                                                                             | Full                                                                                             |

| Automation                                          | Assistance                                                                                  | Automation                                                                                                 | Automation                                                                                     | Automation                                                                                                       | Automation                                                                                       |

| The Human<br>performs all the<br>Verification tasks | The tool features a<br>single automated<br>task ( e.g Constraint<br>Random<br>Verification) | The tool features<br>multiple automated<br>tasks, but Human<br>involvement is<br>needed for other<br>tasks | The tool can perform<br>most verification<br>tasks, but Human<br>overview is still<br>required | The tool performs all<br>verification tasks for<br>certain kind of<br>designs.<br>Human override is<br>an option | The tool performs all<br>verification tasks<br>without any Human<br>intervention or<br>attention |

The Human controls the scope of Verification

The Tool controls the scope of Verification

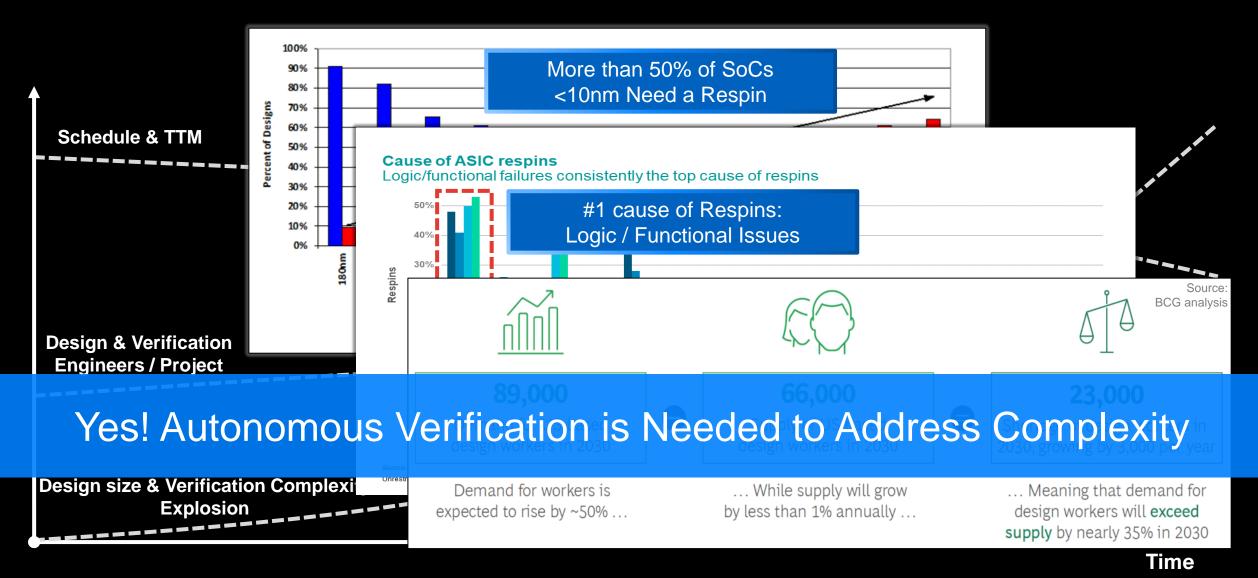

#### Do We Need Autonomous Verification?

#### Where can we do automation in Verification?

© 2023 Synopsys, Inc. 8

Synopsys

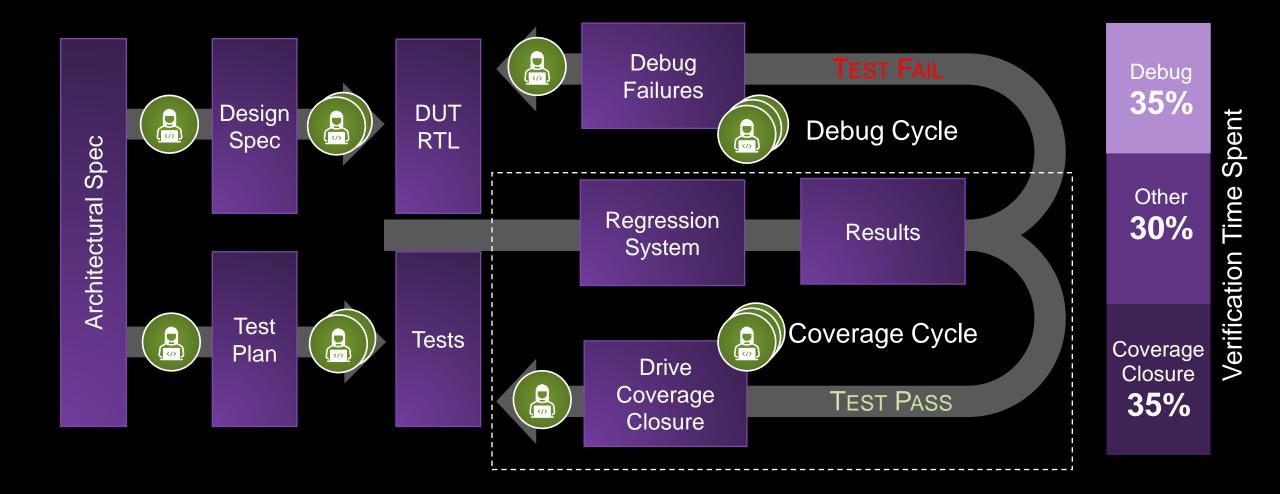

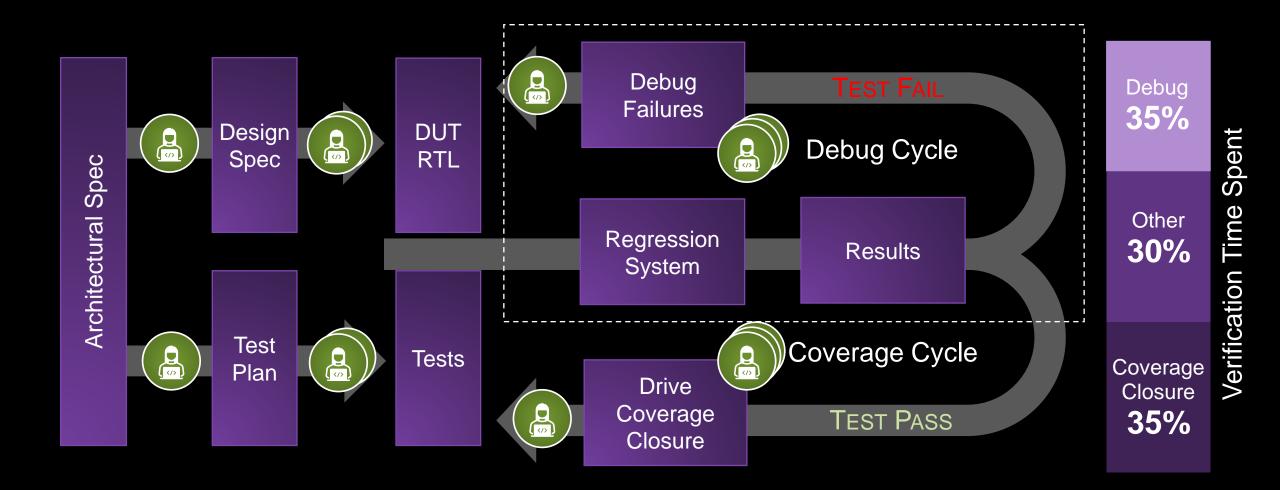

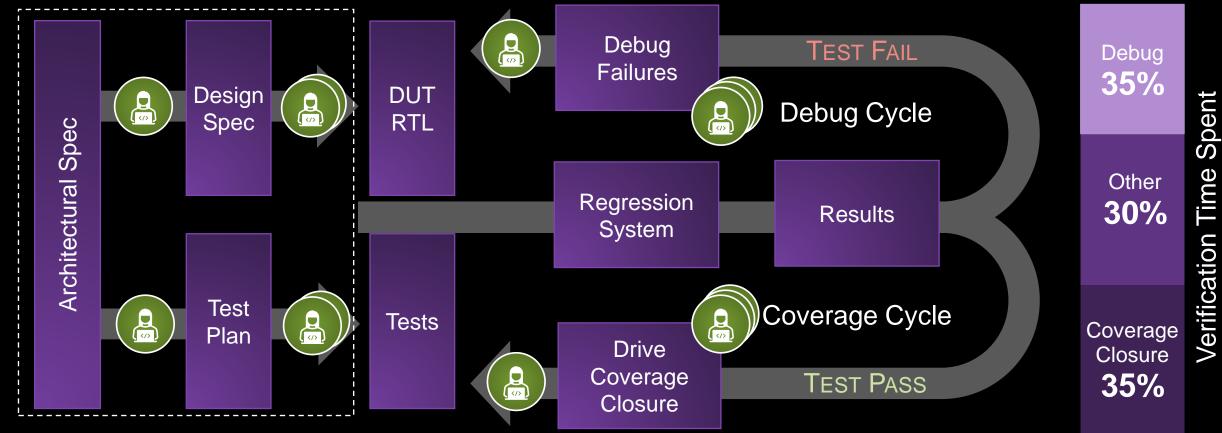

## Typical Coverage Flow

synopsys<sup>®</sup>

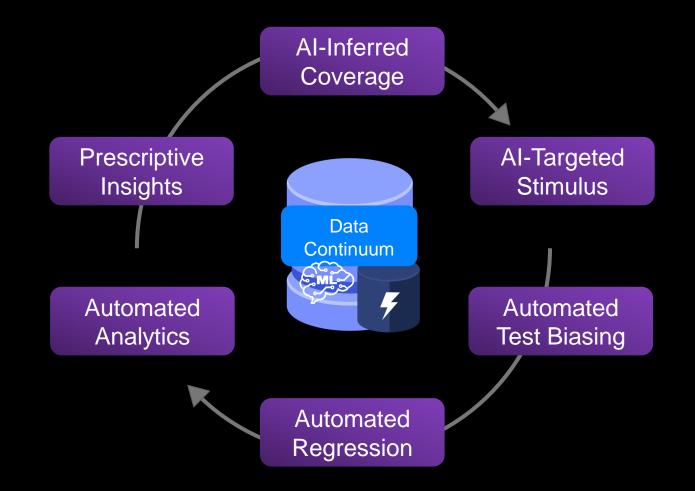

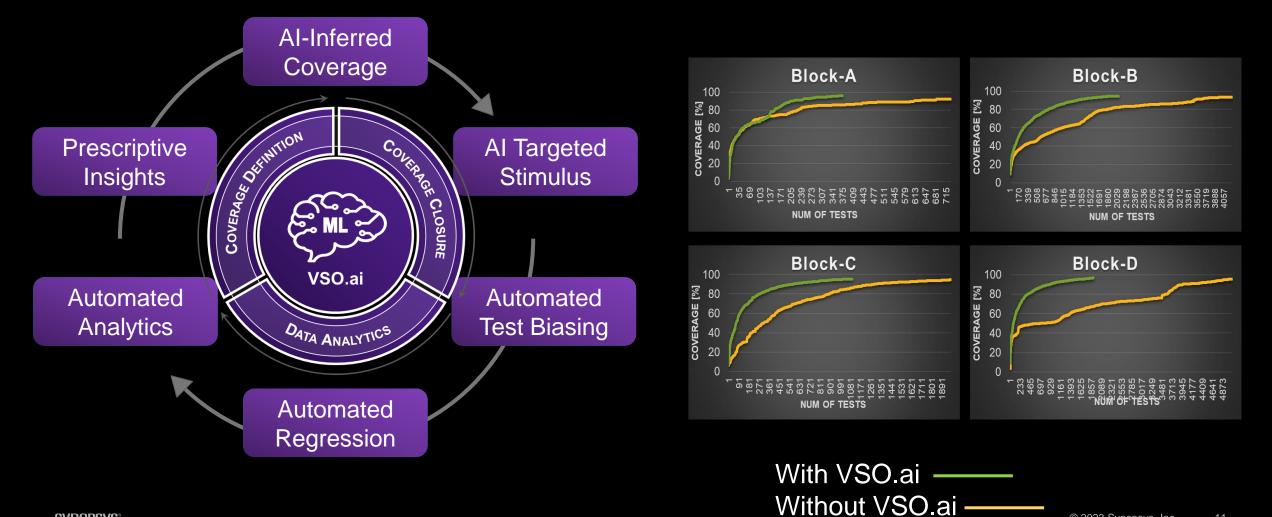

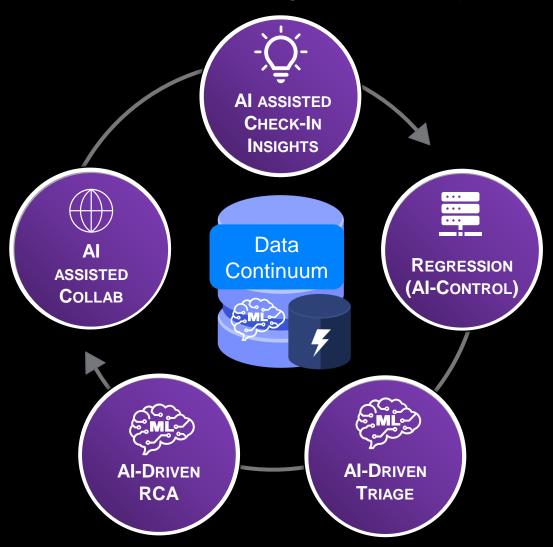

#### Al Assisted Coverage Flow

## VSO.ai: Autonomous Coverage Closure

Accelerating coverage closure upto 3x-5x

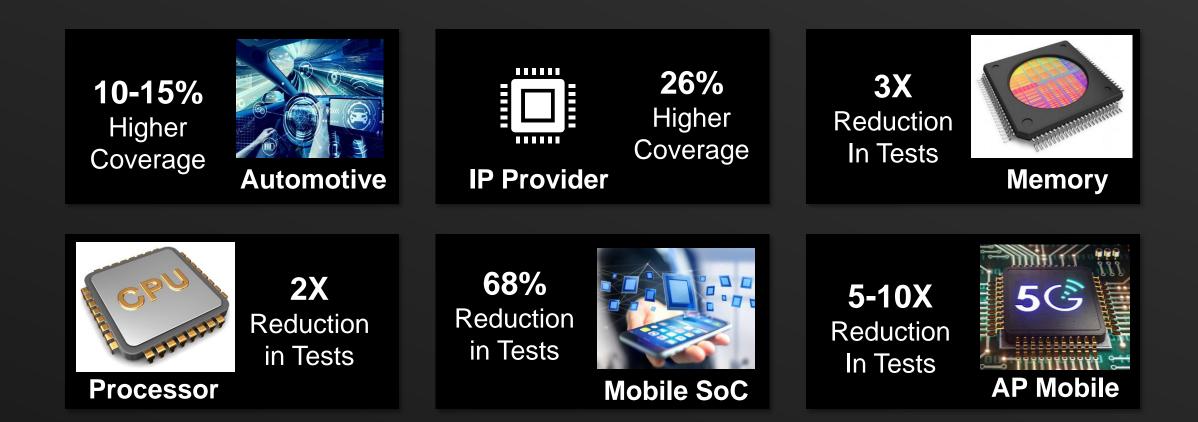

## VSO.ai: Customer Results

Faster Closure and Higher Coverage

**SYNOPSYS**<sup>®</sup>

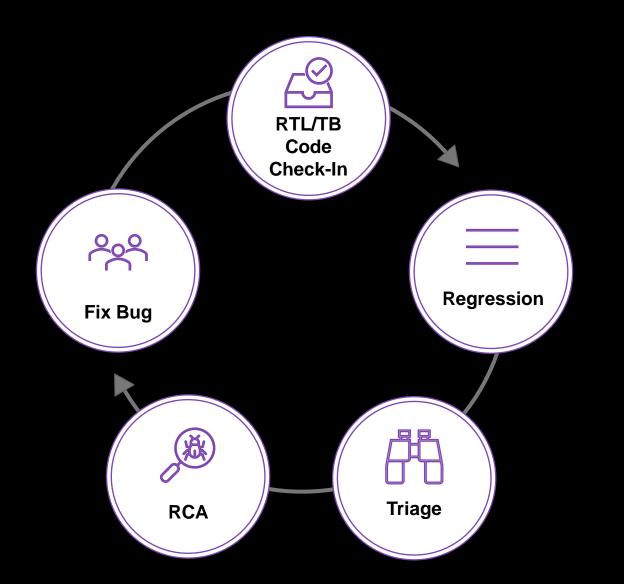

#### How is Debug Automated Today?

**SYNOPSYS**<sup>®</sup>

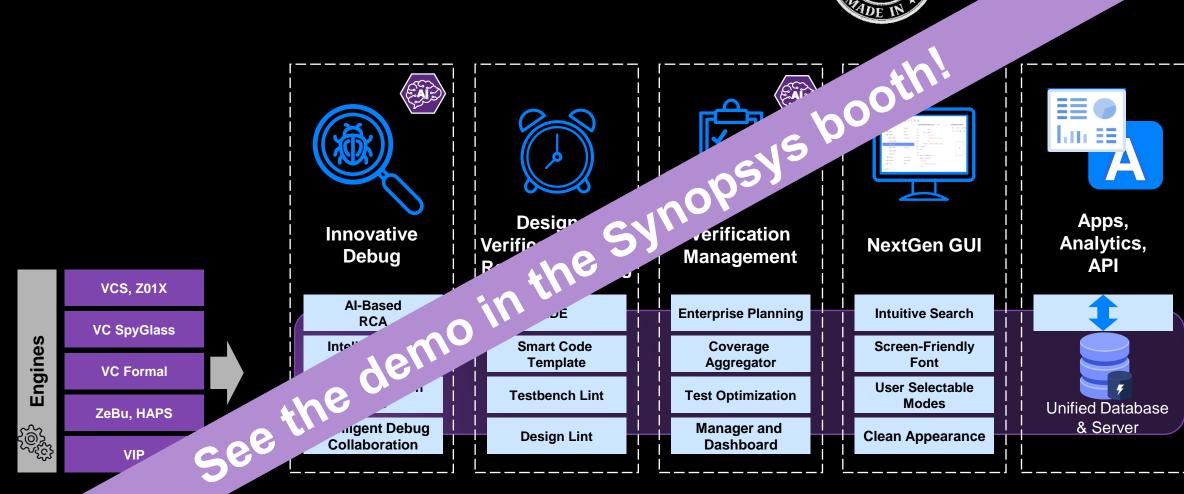

## **Typical Debug Flow**

#### Al Assisted Debug Flow

Next-Generation Verdi: Improves debug productivity up to 10X

## Next-Gen Verdi: Accelerate Debug Automation

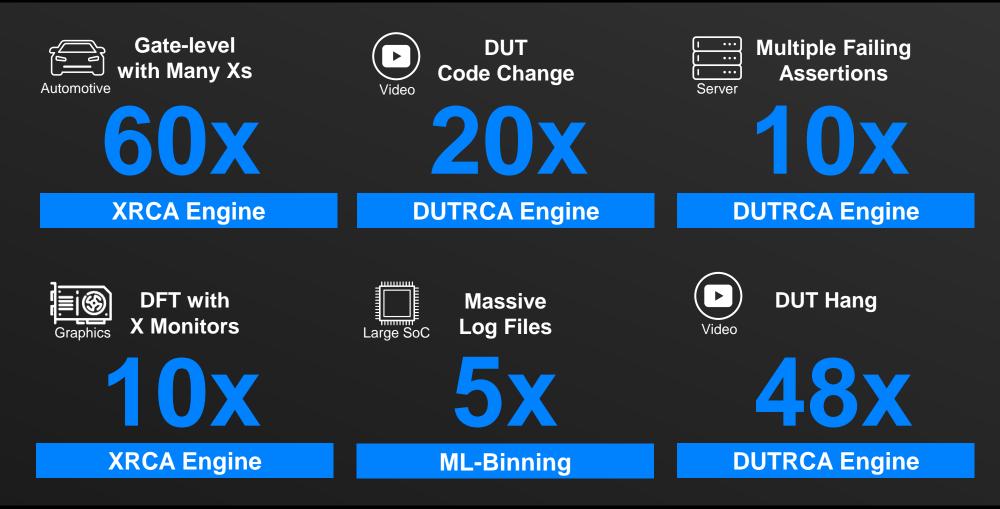

#### **Customer Examples**

#### Introducing Next-Generation Verdi Platform

#### What About Specification Automation?

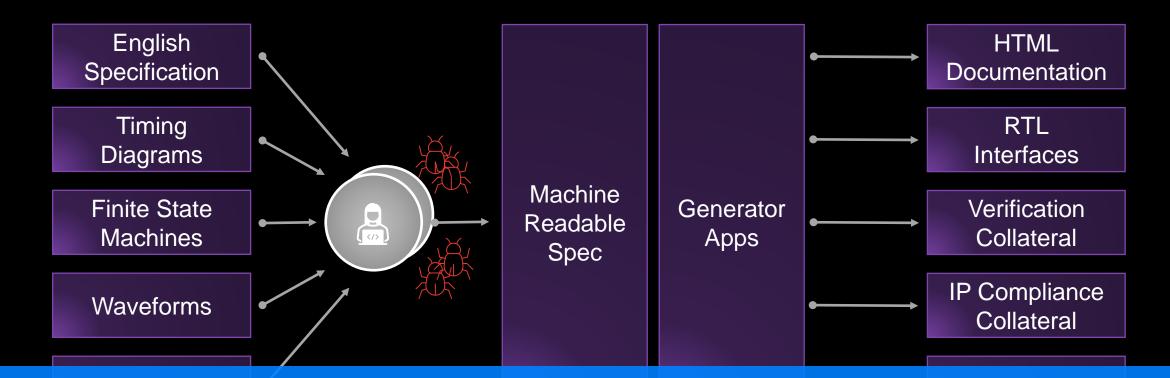

## Typical Specs $\rightarrow$ Collateral Flow

Generative AI Can Help to Remove Ambiguity & Provide Automation.

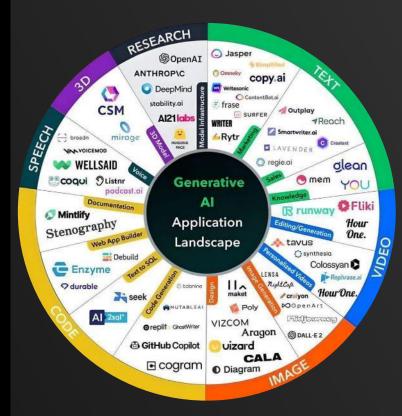

#### Introduction to Generative AI

- Generative AI: a branch of AI used to create new content, including audio, code, images, text, simulations, and videos.

- Recent advances in GPT (Generative Pre-trained Transformer) technology have enabled applications like ChatGPT

- ChatGPT is an LLM interface that can converse with a human, write essays, create websites automatically etc.

If Generative AI can create "intelligent" responses, can it write Verilog, automate chip design flow, and create layouts?

#### LLM Application Landscape

#### How about EDA?

## RTL Copilot

#### Natural Language Text $\rightarrow$ SystemVerilog Code

#### DV Assistants with Engineer in the Loop

| 100)<br>11<br>12<br>13<br>14 | <ul> <li>* if reset is high, reset the output q to 0.</li> <li>3 * Otherwise, only increment the output q if the <u>slowena</u> input is high and q is not 9.</li> </ul> |                                                          |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

|                              | <pre>L5@module count_slow(input clk, input slowena, input reset, output reg [3:0] q);</pre>                                                                              |                                                          |  |  |  |  |

| 16                           |                                                                                                                                                                          |                                                          |  |  |  |  |

| 17<br>18                     | Al proposal 0:                                                                                                                                                           |                                                          |  |  |  |  |

| 19                           | AI proposal 1:                                                                                                                                                           |                                                          |  |  |  |  |

| 20                           | Al proposal 2:                                                                                                                                                           | module count_slow(input clk, input slowena, input reset, |  |  |  |  |

| 21                           |                                                                                                                                                                          | output reg [3:0] q);                                     |  |  |  |  |

| 229                          |                                                                                                                                                                          | always @(posedge clk) begin<br>if (reset == 1'b1)        |  |  |  |  |

| 23                           |                                                                                                                                                                          | q <= 4'd0;                                               |  |  |  |  |

| 24                           |                                                                                                                                                                          | else                                                     |  |  |  |  |

| 25                           |                                                                                                                                                                          | begin                                                    |  |  |  |  |

| 26                           |                                                                                                                                                                          | if (slowena == 1'b1 && q!= 4'd9)                         |  |  |  |  |

| 27                           |                                                                                                                                                                          | q = q + 4'd1;<br>end                                     |  |  |  |  |

| 28                           |                                                                                                                                                                          | end                                                      |  |  |  |  |

| 29                           |                                                                                                                                                                          | endmodule                                                |  |  |  |  |

| 30                           |                                                                                                                                                                          |                                                          |  |  |  |  |

|                              | Press Ctrl+Space to show Template proposals                                                                                                                              | Press 'Tab' from proposal table or click for focus       |  |  |  |  |

#### Provide Spec in Natural Language

## Use LLM interface to Generate RTL code

#### **Review Code**

#### Accept / Reject

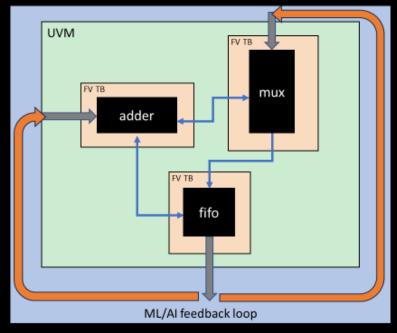

#### Generative AI Vision TechTalk

Presented by Microsoft (Eric Berg) at DAC 2023

#### **HW Vision**

- Generate RTL modules (adder, mux, fifo)

- Generate Formal Verification Testbench (FV TB) for design exercise

- Generate connection logic

- Generate UVM TB for connected block

- Optimize random test stimulus using ML/AI tools

© Copyright Microsoft Corporation

#### **Generative AI Promises**

Transform English Specification to Machine Readable Specification

#### Generative AI: Key Challenges

# Reinforcement Learning with Human Feedback & EDA Tools as Agents in the Loop can help

#### LEVELS OF VERIFICATION AUTOMATION

| 0                                                   | 1                                                                                           | 2                                                                                                          | 3                                                                                              | 4                                                                                                                | 5                                                                                                |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| No<br>Automation                                    | Engineer<br>Assistance                                                                      | Partial<br>Automation                                                                                      | Conditional<br>Automation                                                                      | High<br>Automation                                                                                               | Full<br>Automation                                                                               |

| The Human<br>performs all the<br>Verification tasks | The tool features a<br>single automated<br>task ( e.g Constraint<br>Random<br>Verification) | The tool features<br>multiple automated<br>tasks, but Human<br>involvement is<br>needed for other<br>tasks | The tool can perform<br>most verification<br>tasks, but human<br>override is still<br>required | The tool performs all<br>verification tasks for<br>certain kind of<br>designs.<br>Human override is<br>an option | The tool performs all<br>verification tasks<br>without any Human<br>intervention or<br>attention |

The Human controls the scope of Verification

The Tool controls the scope of Verification

## Question to DALL-E

#### Show the Level 5 vision of Autonomous Verification

**Robots Doing Verification**

We Focusing on What's Important

# Thank You