MUNICH, GERMANY OCTOBER 15-16, 2024

# Calling All Engines - Faster Coverage Closure with Simulation, Formal, and Emulation

Yassine Eben Aimine, Product Architect Dirk Hansen, Application Engineer

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

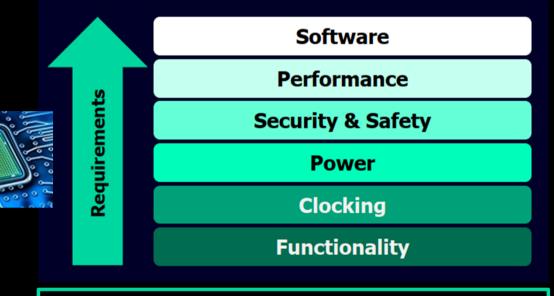

#### Market dynamics drive new use-cases and requirements

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

Complexity in terms of functional verification and HW-SW integration is predominantly due to these increasing levels of requirements

#### **Project impact**

Decline in first silicon success and cost increase significantly affect TTM and business success

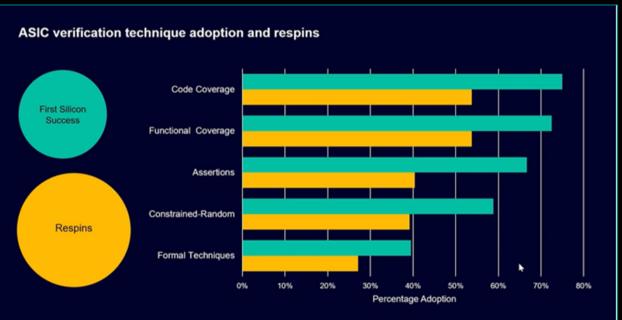

66 % Projects behind schedule 50-60 % Median project time spent in verification 76 % ASICs require 2 or 13 % more respins First silicon success on 10M-1B gates 62 % designs Logical/Functional flaws caused respins in design greater then 1B gates

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

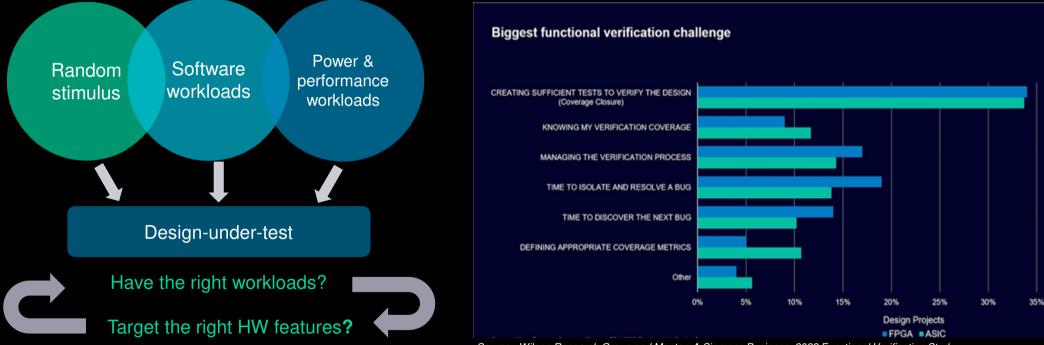

#### Understand the challenge to create the opportunity

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

#### Every project benefits from a robust coverage and assertion methodology

#### Why the need for coverage and assertion ? Metrics to measure verification progress and quality and productivity

#### Code coverage

• Design structure or implementation is covered

#### **Functional coverage**

Intent of the design or specification is covered

#### Assertion

- A given temporal condition holds or is covered

- Improve debug productivity

#### Leverage coverage & assertions to avoid bug escapes from block to system level

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

**ASIC/FPGA** verification effort

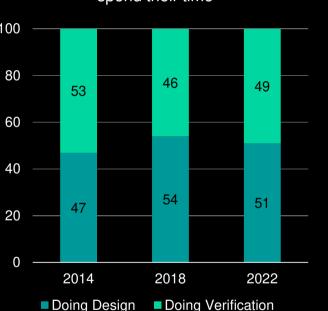

spend their time techniques 100 Code coverage 80 46 49 53 Functional 47% 60 coverage 40 Assertions 54 51 47 20 2007 Constrained-Random 2014 0 2022 2014 2018 2022 20% 40% 0% 60% 80% **Design Projects**

Test Planning Testbench Development

Creating Test and Running Simulation

Other

Debug

21%

15%

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

ASIC adoption of dynamic

Where IC/ASIC design engineers

Coverage & assertion-based verification are growing requirements in emulation

Where IC/ASIC verification engineers spend their time

5%

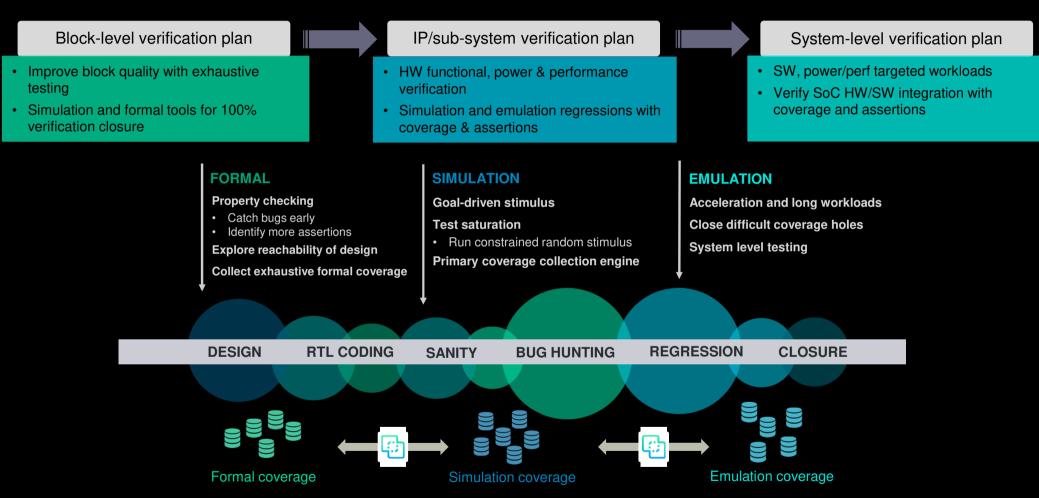

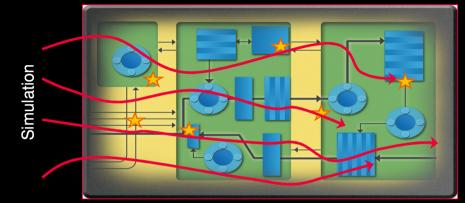

#### An SoC level multi-verification phase and tool challenge Adopt the right verification engine for effective verification sign-off

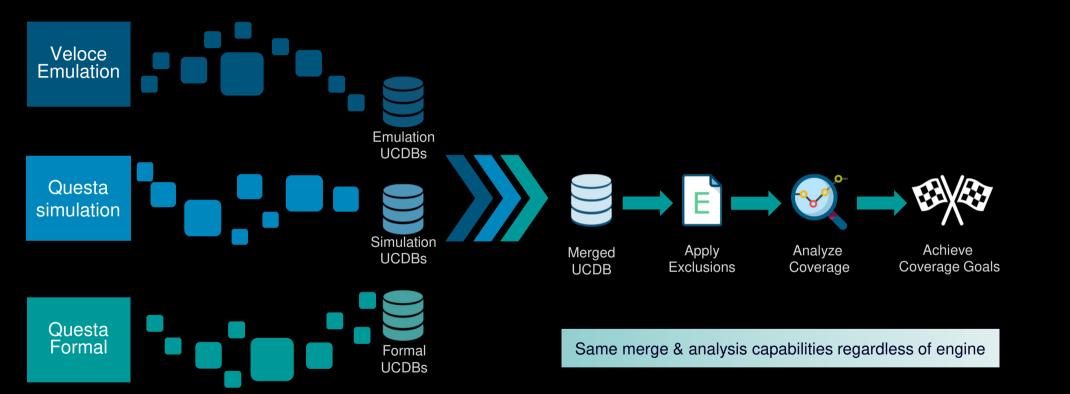

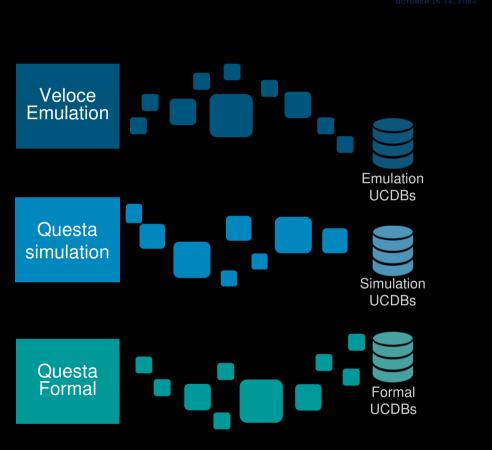

### **Combining Questa Simulation, Questa Formal and Veloce emulation coverage**

#### Agenda

- The Case for Unified Coverage

- Simulation and Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

#### Purpose of Code Coverage

#### Determine the effectiveness of your testbench

- Does it exercise the HDL model (source code)

- Helps automate design process.

#### Use to improvement / gain confidence in the test suite

• Use in a manufacturing functional test

Shorten Lab Debug Time Expose corner case bugs

#### **Purpose of Functional Coverage / Assertion covers**

- The role of the functional coverage model is to ensure that the tests that the DUT passes have checked the design features for all of the relevant conditions.

- The testbench will exercise the features of the design. The role of the functional coverage model is to check that the different variants of those features have been observed to work correctly.

- Features may also be referred to as requirements or in some situations as stories.

#### Purpose of using both types of coverage

• All nodes inside the design have been stimulated

#### 100% functional coverage means

• All possible combinations of input stimuli have been applied to the design, and the output is proven correct

100% code coverage and 100% functional coverage → DONE TESTING

# Major Types of Coverage

| Code Coverage                                                                                                                                                                                                                                                         | FSM Coverage                                                                                                                                                                                                                             | Functional<br>Coverage                                                                                                                                                                                                                                                                            | Assertion<br>Coverage                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Did all statements,<br/>branches of code get<br/>exercised?</li> <li>Did all signals toggle<br/>at least once?</li> <li>Automated in the<br/>simulation<br/>environment</li> <li>A basic measure with<br/>little correlation to<br/>functionality</li> </ul> | <ul> <li>Did all the states and transitions get exercised?</li> <li>Automated in the simulation environment</li> <li>Typically included with code coverage</li> <li>Indicates transitions exercised, not functionally correct</li> </ul> | <ul> <li>Have all the important values/ranges of a signal been covered?</li> <li>Have sequences / transitions between signals been covered?</li> <li>Verification engineer must write covergroups, bind into RTL</li> <li>Are the covergroups written correctly? Do they cover enough?</li> </ul> | <ul> <li>How many times did<br/>the assertion get<br/>evaluated and pass,<br/>and fail?</li> <li>Designer must write<br/>assertions and cover<br/>properties</li> <li>Is the assertion<br/>implemented<br/>correctly? Check<br/>anything of value?<br/>Are there enough<br/>assertions?</li> </ul> |

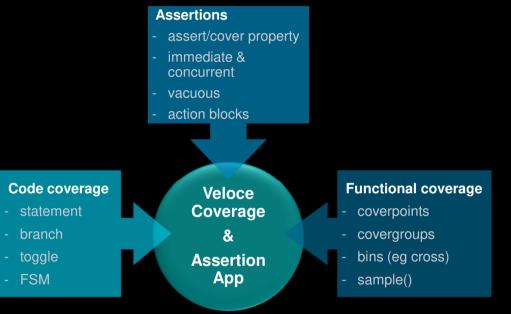

#### **Veloce Coverage & Assertion App – Addressing Coverage Closure Needs**

**Functional Coverage** Have signals taken specific set of values? Have signals taken specific sequence of values?

Did interesting value combinations occur?

#### Code Coverage All statements/branches exercised? All signals toggled? All FSM states reached? All state transitions taken?

#### **Coverage Metric Holes**

#### Code / FSM / Assertion Coverage

- Functional dead code and unreachable FSM states/transitions

- Modes of the design that create dead code

- Time can be wasted trying to hit these holes!

#### **Transaction/Structural Coverage**

- Testbench doesn't stress the design enough

- Incomplete models don't exercise all transactions

#### **Functional Coverage**

Incomplete spec or planning, lack of knowledge/time

#### Proper test planning can mitigate some of these challenges

Static techniques such as Questa CoverCheck can minimize time to closure

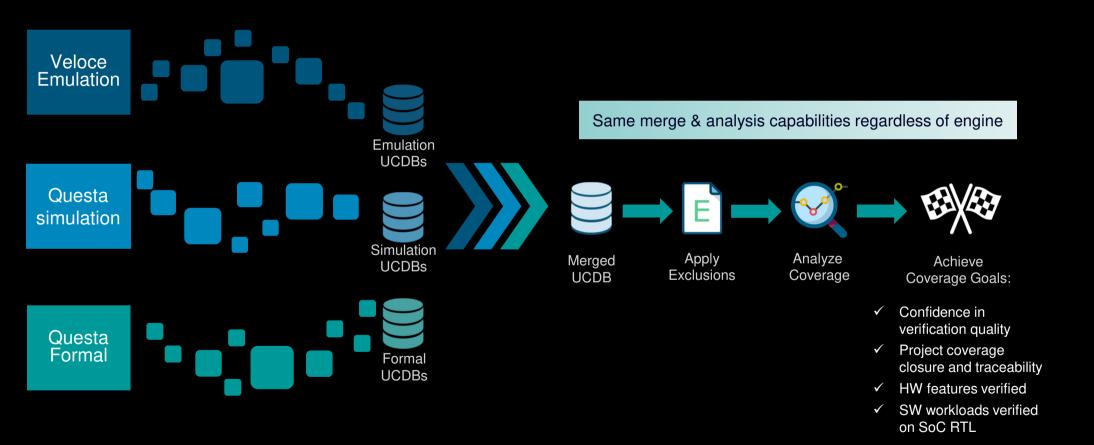

#### Accelerate coverage closure and assertion-based debug

Re-use simulation coverage and assertions to achieve metric-driven verification goals in emulation

Run real workloads that effectively cover the system features and stress scenarios

Fast coverage closure & efficient assertionbased debug for complex system level bugs

Effectively merge coverage with simulation and emulation results for project level view

## Code Coverage Metrics Supported by Veloce Coverage App

#### Statement Coverage

Check if all procedural statements in always blocks (clocked/combinational) are exercised

#### **Toggle Coverage**

Check if all signals have toggled from 0->1 and 1->0

#### **Branch Coverage**

Check if all branches in always blocks (clocked/combinational) are exercised

• if/case/conditional operator

Also check if none of the branches are taken (missing else)

# FSM Coverage

transitions

State Coverage – Check if all states of the FSM have been covered

Transition Coverage – Check if all **possible** transitions between states have been covered.

Can also be determined by branch coverage, but a more intuitive representation

#### **Methodology Considerations**

- Once enabled, code coverage is automatic. No changes / additions to RTL required.

- While easy to "turn on everything," doing so can significantly impact capacity.

- Counter width settings and thresholds are global.

- Be mindful of capacity increases and adjust counter widths accordingly.

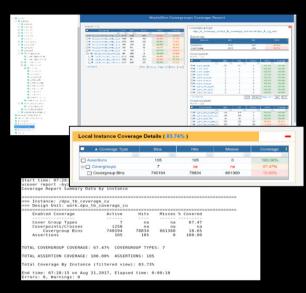

#### **Coverage Database: UCDB**

- The Unified Coverage Interoperability Standard (UCIS) from Accelera defines the schema/format for storing Coverage information, known as UCISDB (or UCDB)

- Manipulation via standard APIs, implementation is tool-specific

- Questa fully supports this standard

- Integration in Veloce to generate Questa-compatible UCDB

- All actions/manipulations possible with Questa-generated UCDB also possible with Veloce-generated UCDB

- Reporting

- Merging (Veloce-Veloce or Questa-Veloce)

- Ranking

- Questa Coverage ecosystem available to Veloce as well

- vcover utility

- Visualizer

- Coverage Analyzer

# Unified coverage and assertion metrics

|        | Statement | Branch                      | Block | Expr/Cond<br>(FEC) | FSM<br>(State/Trans) | Toggle | Covergroup | Assert / Cover |

|--------|-----------|-----------------------------|-------|--------------------|----------------------|--------|------------|----------------|

| Questa |           |                             |       |                    |                      |        |            |                |

| Veloce |           |                             | C     | C                  |                      |        |            |                |

| Formal |           |                             |       |                    |                      |        |            |                |

|        |           | Supported<br>Future Support |       |                    |                      |        |            |                |

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

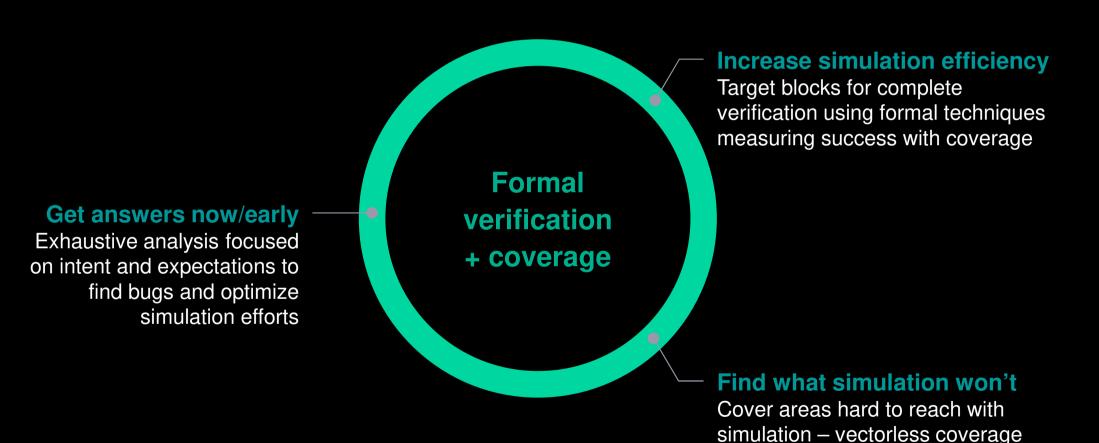

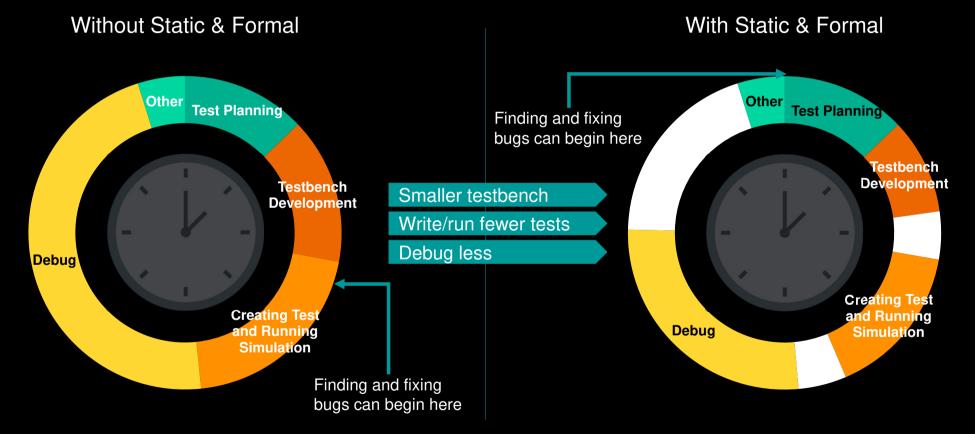

#### Adding formal coverage is critical to success

Complementary with simulation, deliver unique abilities and acceleration

#### Formal adoption does more than increase simulation efficiency Finding and fixing bugs before testbench increases team agility

Source: Wilson Research Group and Mentor, A Siemens Business, 2022 Functional Verification Study

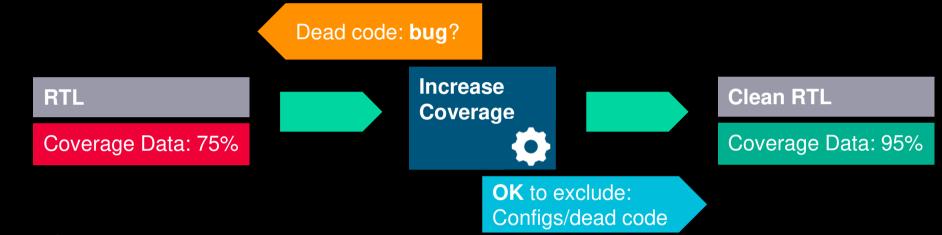

#### **Reachability – simulation coverage closure**

#### **Questa Increase Coverage** performs a reachability analysis for all code coverage items

#### Reachability provides design insights in form of:

- Dead code analysis

- FSM state and arc analysis

- Signal stuck at value analysis

- Witness trace

- Supports same 7 coverage types Questa Sim

- bcefst and bin

Used to accelerate simulation coverage closure

- Tight integration with Questa Sim and UCDB

- Integrated with Coverage Analyzer

| always @*<br>if (a)<br>else if (b)<br>else | R = 2'b00;<br>R = 2'b01;<br>R = 2'b11; |

|--------------------------------------------|----------------------------------------|

| •••                                        |                                        |

| always @*                                  |                                        |

| case (R)                                   |                                        |

| 2'b00:                                     | T = 1'b0;                              |

| 2'b01:                                     | T = 1'b1;                              |

| 2'b10:                                     | T = 1'b1;                              |

| 2'b11:                                     | T = 1'b0;                              |

| endcase                                    |                                        |

#### Questa Increase Coverage Statically identifies unreachable code

#### Increase Coverage advantages

- Save man-months of effort closing coverage

- Tight integration with UCDB

- Automation of exclusions

- Identifies unreachable coverage targets

- Multi-vendor solution

#### Reachability and observability – formal code coverage

#### Questa Verify Property performs a reachability and observability analysis for all code coverage items

#### Reachability provides design insights in form of:

- Dead code analysis

- FSM state and arc analysis

- Signal stuck at value analysis

- Over-constraint analysis

- States and signals contributing to property proof

| always @*<br>case (sel) |            |

|-------------------------|------------|

| 2'b00:                  | en = 1'b0; |

| 2'b01:                  | en = 1'b1; |

| 2'b10:                  | en = 1'b1; |

| 2'b11:                  | en = 1'b0; |

| default:                | en = 1'b0; |

| endcase                 |            |

Observability provides design insight in form of structural coverage contributing to property proof

#### Formal signoff code coverage

#### Based on property proof coverage Familiar code coverage types with simulation

- Branch

- Condition

- Expression

- FSM

- Statement

- Toggle

- Covergroup bin

#### Based on two concepts:

- Reachability

- For a given property and its cone of influence, what logic is reachable from the inputs?

- Observability

- For a given property, what logic was used to prove the property (is observable by a property)?

- 100% code coverage doesn't equal bug free RTL

- Focus on what isn't covered, improve TB there

| Reachable    | Observable | Coverage Result |

|--------------|------------|-----------------|

| Yes          | Yes        | Covered         |

| Yes          | No         | Uncovered       |

| No           | -          | Excluded        |

| Inconclusive | -          | Uncovered       |

#### Verify Property formal coverage methodology

The 4 types of formal coverage: reachability, observability, bounded reachability, and signoff

#### **Analysis: Reachability**

#### Reachability analysis shows if a cover item (sbceft bin) is reachable from the design inputs

- Can be used for insight into the complexity of the design

- Can be used with or without properties

- Unreachable logic is a bug or can be excluded

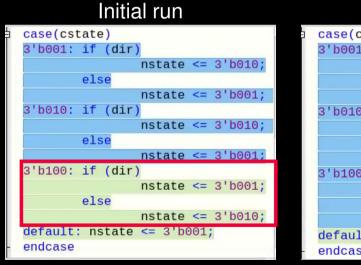

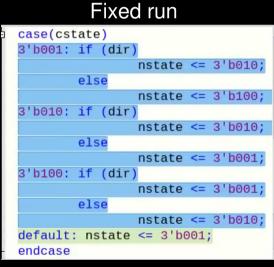

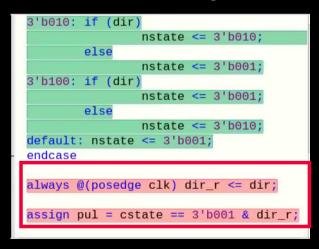

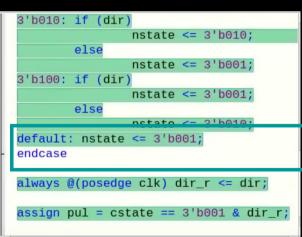

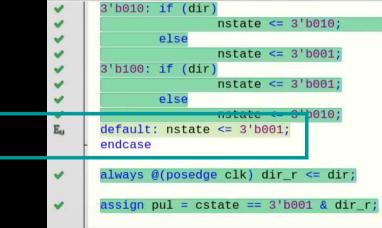

#### Example FSM design:

Initial run has unreachable FSM state and transitions, bug?

| Reachability   |         |             |              |             |

|----------------|---------|-------------|--------------|-------------|

| Summary (Recu  | ursive) |             |              |             |

| Coverage       | Total   | Unreachable | Inconclusive | Reachable   |

| Branch         | 13      | 1           | Θ            | 12 ( 92.3%) |

| Condition      | 0FF     | OFF         | 0FF          | OFF ( N/A ) |

| Expression     | 0FF     | OFF         | OFF          | OFF ( N/A ) |

| FSM State      | 3       | 0           | Θ            | 3 (100.0%)  |

| FSM Transition | 5       | Θ           | Θ            | 5 (100.0%)  |

| Statement      | 12      | 1           | Θ            | 11 ( 91.7%) |

| Toggle         | OFF     | OFF         | OFF          | OFF ( N/A ) |

| Covergroup Bin | Θ       | Θ           | Θ            | 0 ( N/A )   |

| Total          | 33      | 2           | 0            | 31 ( 93.9%) |

#### Analysis: Observability

#### Observability analysis shows if a cover item (sbceft bin) is observable by a property

- Is used to determine where in the design to add more properties

- Is calculated from proofs or bounded proofs during the formal run

#### Example FSM design:

Add properties that exercise the uncovered logic, repeat till covered

Uncovered logic

#### Property added to cover it

#### bservability Summary For 1 Property (Recursive) Observable Total Unobservable Coverage (Proofs) 13 Θ 13 (100.0%) Branch OFF Conditio OFF OFF ( N/A ) OFF OFF OFF ( N/A Expression FSM State 3 Θ 3 (100.0%) 5 (100.0%) ESM Transition 5 Θ Statement 12 10 (83.3%) OFF OFF OFF ( N/A ) Toggle 0 0 ( N/A ) Covergroup Bin Tota 33 31 ( 93.9%)

#### Signoff coverage: Obs + Rea

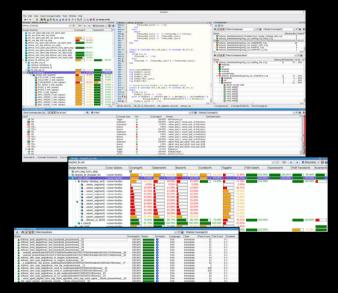

## Verify Property debug: formal signoff coverage

#### 19% signoff coverage with proofs, still a lot uncovered, need to add properties to uncovered areas

• Add properties that verify to the spec the logic that is uncovered (highlighted in red)

| File Edit View Des           | sign Tools Window Help                |                              |           |                                                                | Use                 | to goto li     | ne      |             |                       |             |                  |

|------------------------------|---------------------------------------|------------------------------|-----------|----------------------------------------------------------------|---------------------|----------------|---------|-------------|-----------------------|-------------|------------------|

| <b>←</b> · →                 | Look for                              | Dod                          |           | AnyEdge ▼ → 0 	 + 1ns ▼                                        |                     |                |         |             | Coverage Sum          | mary - top  | + ×              |

| Design -                     |                                       | Reu                          | + 4 2     |                                                                |                     | uncovere       | a       |             |                       |             | K X              |

| Search: Type Search          | iexi (Fiess Eiller)                   |                              |           | <ul> <li>■ X ▼ ▲ E<sub>U</sub> ▼ ▲ ✓ ▼ =</li> <li>32</li></ul> | ▲   ♥ ♥ ▲           | Signoff        |         |             |                       |             |                  |

| Instance                     | Module                                | % Coverage                   | Coverage  | 32 € Case(sel)<br>33 ✔ 2'b00: rin <= 4'h                       | 1;                  |                |         |             |                       |             |                  |

| top                          | top<br>ftb top                        |                              | 404 / 592 | 34 ✓ 2'b01: rin <= 4'h                                         |                     | Summary For 2  | Propert | ies (Recur  | sive)                 |             |                  |

| u ff                         | ff                                    |                              | 4/12      | 35 ✔ 2'b10: rin <= 4'h<br>36 Eu 2'b11: rin <= 4'h              |                     |                | -       | la companya | and the second second | Covered     | Covered          |

| - 📃 u_ff4                    | ff4                                   |                              | 16 / 24   | 37 Eu default: rin <= 4                                        | 'h1;                | Coverage       | Total   | Uncovered   | Excluded              | (Proofs)    | (+Inconclusives) |

|                              | fifo<br>fsm                           |                              | 207 / 241 | 38 - endcase<br>39<br>40 always @(posedge                      | clk or negedge rstn | Branch         | 66      | 6           | 17                    | 7 ( 14.3%)  | 43 ( 87.8%)      |

|                              |                                       |                              |           | 40 always g(poseuge<br>41 x if (!rstn)                         | 1                   | Condition      | 22      | 2           | 7                     | 3 ( 20.0%)  | 13 ( 86.7%)      |

|                              |                                       |                              |           | 42 rino <= 4                                                   | 'h1:                | Expression     | 29      | 14          | 1                     | 0 ( 0.0%)   | 14 ( 50.0%)      |

|                              | What n                                | ronertie                     | es can I  | X else<br>44 X rino <= r                                       |                     | FSM State      | 3       | 0           | 0                     | 0 ( 0.0%)   | 3 (100.0%)       |

| <u>n</u>                     | · · · · · · · · · · · · · · · · · · · |                              |           |                                                                |                     | FSM Transition | 6       | Θ           | 3                     | 0 ( 0.0%)   | 3 (100.0%)       |

| Coverage (Signoff<br>Show: S | add to v                              |                              |           | ] <b>]</b> ] <b>T X</b> E <sub>0</sub> ✔ ✔ E   ⊕               |                     | Statement      | 75      | 15          | 16                    | 7 ( 11.9%)  | 44 ( 74.6%)      |

| ∆ Line#                      | Add prop                              | erties a                     | nd rerun  |                                                                |                     | Toggle         | 378     | 60          | 37                    | 80 ( 23.5%) | 281 ( 82.4%)     |

|                              |                                       |                              |           |                                                                |                     | Covergroup Bin | 13      | 10          | Θ                     | 0 ( 0.0%)   | 3 ( 23.1%)       |

|                              | Toggle                                | ✓ (0->1)<br>✓ (1->0)         |           |                                                                |                     | Total          | 592     | 107         | 81                    | 97 ( 19.0%) | 404 ( 79.1%)     |

| - 🕥 3                        | Toggle<br>Toggle                      | <b>E</b> <sub>U</sub> (0->1) |           |                                                                |                     |                |         |             |                       |             |                  |

|                              | Toggle                                | Eu (1->0)                    |           |                                                                |                     | <b>I</b> ,     |         |             |                       |             | 1                |

| Transcript 🛛 Cover           | rage (Signoff) 🛛 Design Ch            |                              |           |                                                                | Ite                 | rate until     | 0       |             |                       |             |                  |

|                              |                                       |                              |           |                                                                |                     |                |         |             |                       |             |                  |

|                              |                                       |                              |           |                                                                |                     |                |         |             |                       |             |                  |

#### **Coverage tracking and analysis** Questa Verify Property

#### **Coverage Analyzer and Visualizer supporting views**

Will include higher-level tracking management systems (Polario

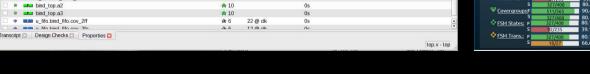

#### Formal coverage workflow

Tools Window Helr 🚯 🎧 🎟 🕏 🗟 👔 👔 🗟 す 🧎 Mnem 🔹 🗢 AnyEdge 🔹 🌩 0

Hier Instance -

Compile @ 🥵 📝 New Property 🏘 Filter: Type here <Ctrl+E

Exact

+ # # X P top.y - top

31

34

35

36 37

38

40

41 E

42 E

44

ile Edit View Coverage Summary

ftb top

ff4

fifo

Name

bind\_top.a1

□ \_\_\_\_ u\_fifo.bind\_fifo.a\_data\_chk

u\_fifo.bind\_fifo.a\_overflow ◎ ■ u\_fifo.bind\_fifo.a\_underflow

earch: Type Sea

bind\_top

u ff

\_ \_ u\_ff4

🖬 u\_fifo

🗉 🗾 u\_fsm

- Debug done in Verify Property

- Tracking/Management same as simulation/emulation using the

Total Uncovered Excluded Covered (Proofs)

20

11 19

124 50 Covered

45 (80.4%

43 ( 93.5%

3 (100.0%

3 (100.0%)

13 (86.7%

13 ( 65.0%)

0 ( 0.0%)

\*\*\*

204 ( 62.2%)

16 (28.6%)

15 (32.6%)

3 (100.0%)

3 (100.0%)

3 (20.0%)

3 ( 15.0%)

94 (28,7%)

0(0.0%

137 ( 28 59

Restricted | © Siemens | Coverage Closure | DVCon Europe 2024

Questa PropCheck 2020.4-DAILY\_BETA\_200716 (...ropCheck/formal\_cov\_all/log/propcheck.db)

2'b00: rin

'b01: rin <= 4'h2

2'h10' rin <= 4'h4

default: rin <= 4'h1;

always @(posedge clk or

0. 0 0 1 2

rino <= 4'h1:

rino <= rin;</pre>

Health Radius

**±** 10 3 @ clk

0 10

\*0

always @ case(sel)

endcase

if (!rstn)

else

1ns -

+ 7 X

• •

10 @ cl

Formal Coverage

Coverage

Statement

FSM State

Condition

Togale

Expression

ESM Transition

Branch

Summary For 5 Properties

378

11

12

| on, etc.)                                                                 | Coverage Summery                                                            | 0.00%<br>52.77%<br>0.00%      | 0.0096 0.009<br>31.33% 0.009<br>0.0096 0.009<br>28.57% 58.33<br>(4.1)                                              | 26 ✓<br>27 ✓<br>28 ✓<br>30 Xs<br>31 E<br>33 ✓<br>33 ✓ | sel << :<br>else if (bin ==<br>sel <= :<br>always @*<br>case(sel)<br>2'b00: rin <= 4<br>2'b10: rin <= 4<br>2'b10: rin <= 4 | 2'b01;<br>2'b10;<br>2'b10;<br>2'b00;<br>'h1;<br>'h2; | * *<br>* *         |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|

|                                                                           | Total Coverage                                                              | 13% covered                   | Branches. 14/4<br>Conditions: 2/4<br>Expressions: 3/17<br>Fam States: 0<br>Fam Transitions: 0<br>Statements: 14/64 | (14.28%)<br>(17.64%)<br>(3 (0.00%)<br>(6 (0.00%)      |                                                                                                                            |                                                      |                    |

| UCDB                                                                      | 1713% covered      22/87% m     Transcript     Coverage Summary     Code Co | nssed<br>overage Analysis 💿 📄 | Toggles 48/140                                                                                                     | 0.0                                                   | 25 0 50.0                                                                                                                  | 75.0<br>top                                          | 100.0<br>a.v - top |

| c_merged.ucdb                                                             | Coverage By Instance                                                        |                               | Home Covergroups                                                                                                   | Design -                                              |                                                                                                                            |                                                      | Dout C             |

| •<br>→ Bin Distribution <b>Đ</b><br>→ → → → → → → → → → → → → → → → → → → |                                                                             |                               | Total Coverage                                                                                                     |                                                       | wergroup Coverage                                                                                                          |                                                      |                    |

ାନ୍ମ - formal.ucdb 🧧 🛱 💮 ହୁ କୁ ଭୁ ହୁ ଭୁ ଭୁ ଭୁ ଭୁ ଭୁ କୁ 🖗 😣 📕

DU 🔹 🔹 🕲 Recursive 🔹 🎹 🚱

-----

wire fdeg, fen

always @\* if (bin == 2'b01)

20 21 22 Xs 23 ✓

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

#### **Combining Questa Simulation, Questa Formal and Veloce emulation coverage**

#### Comparing formal coverage to simulation/emulation coverage

- Is based on vectors run through the design

- Whatever a vector hits is covered

- Can be logic related to / unrelated to what is being tested

- Property coverage = pass/fail

- For all vectors looking for what isn't covered

- Action: Run more vectors to hit what isn't covered

#### Formal Code Coverage = Property Coverage

- Is based on proven properties in the design

- What logic is used to prove a property is covered

- Only related to a given property

- Property coverage = proven/fired/inconclusive

- For all properties looking for what isn't covered

- Action: Add more properties to hit what isn't covered

- Is a combination of reachability and observability Restricted | © Siemens | Coverage Closure | DVCon Europe 2024

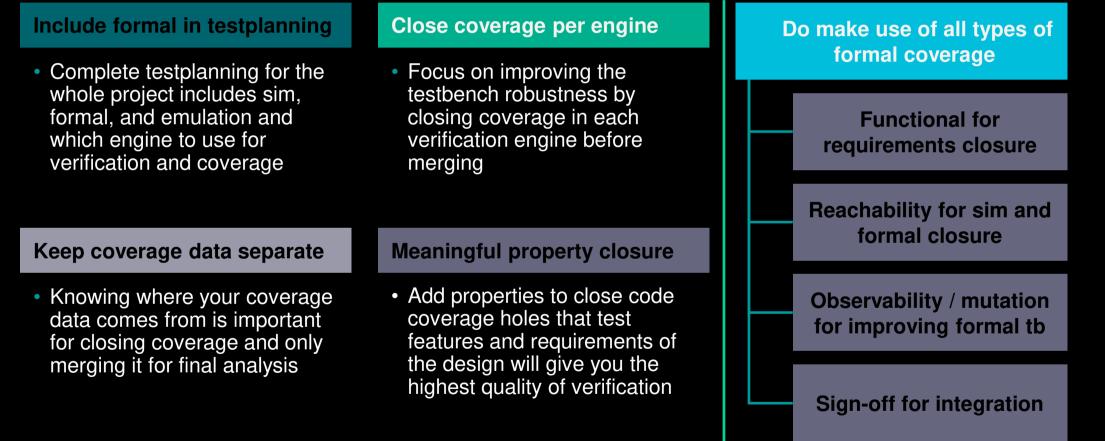

#### **Don't cross the streams** Example comparing simulation and formal coverage

Each tool's coverage is there to point to holes in each tool's respective flows

- Mixing coverage masks this data (customers will still want to do it)

- The semantics of each is different, how it is calculated is different

- Sim coverage is more optimistic when compared to formal coverage

- Example: Design has A,B,C outputs, 1 hot 0. Formal proves 1 hot property, sim does vectors for all 3

outputs

Formal coverage from UCDB (s,b)

- Statement 5.45%

- Branch 0%

#### Sim coverage from UCDB (s,b)

- Statement 92.94%

- Branch 88.23%

| L Coverage Summary                                        |                             |       |           |             | + 🛛 🗷   |

|-----------------------------------------------------------|-----------------------------|-------|-----------|-------------|---------|

| Design/Testbench Testplan                                 |                             |       |           |             |         |

| Total Coverage<br>21.09% covered                          | Assertions: 1/1 (100.00%)   |       |           |             |         |

|                                                           | Branches: 0/34 ( 0.00%)     |       |           |             |         |

| 21.09% covered                                            | Conditions: 0/12 ( 0.00%)   |       |           |             |         |

| 78.91% missed                                             | Statements: 3/55 ( 5.45%)   |       |           |             |         |

| 21.09% covered 78.91% missed                              | Toggles: 0/50 ( 0.00%)      |       |           |             |         |

|                                                           | 0.0                         | 25.0  | 50.0      | 75.0        | 100.0   |

| Transc 🖾 Coverage Summ 🔯 DUs 🖾 Code Coverage Outl 🖾 Cover | rgro 🛛 🛛 Toggle Cover 🖾     | Fsm 🖾 | Directi 🖾 | Assertion ( | Cover 🛙 |

| ≜ Coverage Summary                                        |                             |       |           |             | + 🔹 🕫   |

| Design/Testbench Testplan                                 |                             |       |           |             |         |

| Total Coverage                                            |                             |       |           |             |         |

|                                                           | Assertions: 1/1 (100.00%)   |       |           |             |         |

|                                                           |                             |       |           | 1           |         |

|                                                           | Branches: 30/34 ( 88.23%)   |       |           |             |         |

| 193.72% covered                                           | Statements: 79/85 ( 92.94%) |       |           |             |         |

| 93,72% covered 6.28% missed                               | 0.0                         | 25.0  | 50.0      | 75.0        | 100.0   |

| Transc 🛛 Coverage Summ 🛛 DUs 🖾 Code Coverage Outl 🖾 Cover | rgro 🖾 🛛 Toggle Cover 🖾     | Fsm 🖾 | Directi 🖾 | Assertion C | over 🖾  |

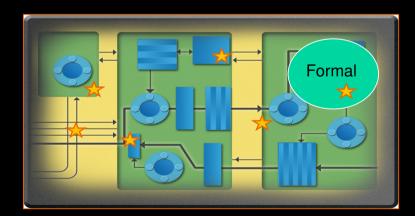

**Recommendations for merging formal with simulation coverage** Using both formal and simulation coverage to ensure robustness and correctness

| Functional                                                                                                                                                                       | Cone of Influence                                                                                                                                                        | Mutation                                                                                                                                                                                               |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>Assertions check design<br/>behavior</li> <li>Cover statements show parts<br/>of the design covered</li> <li>Both tied to test-planning and<br/>requirements</li> </ul> | <ul> <li>Structural COI based</li> <li>Very early code coverage<br/>Where to add properties</li> <li>Not generally used</li> </ul>                                       | <ul> <li>Design mutation based<br/>Is property impacted?</li> <li>Very accurate code coverage<br/>Where to add properties</li> <li>Computationally intensive</li> </ul>                                |  |  |  |  |

| Reachability                                                                                                                                                                     | Observability                                                                                                                                                            | Signoff                                                                                                                                                                                                |  |  |  |  |

| <ul> <li>Unreachable logic checking<br/>Bugs and configuration</li> <li>Used to increase sim code<br/>coverage</li> <li>Over-constraint checking</li> </ul>                      | <ul> <li>Property based code coverage</li> <li>Logic used to prove the property is observable by the property</li> <li>Early guide on where to add properties</li> </ul> | <ul> <li>Combination of observability<br/>and reachability</li> <li>Final coverage data to UCDB</li> <li>Integration with other<br/>verification engine data and<br/>coverage closure tools</li> </ul> |  |  |  |  |

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

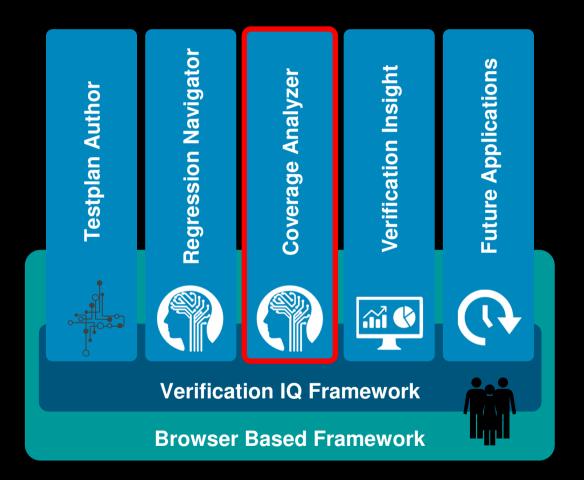

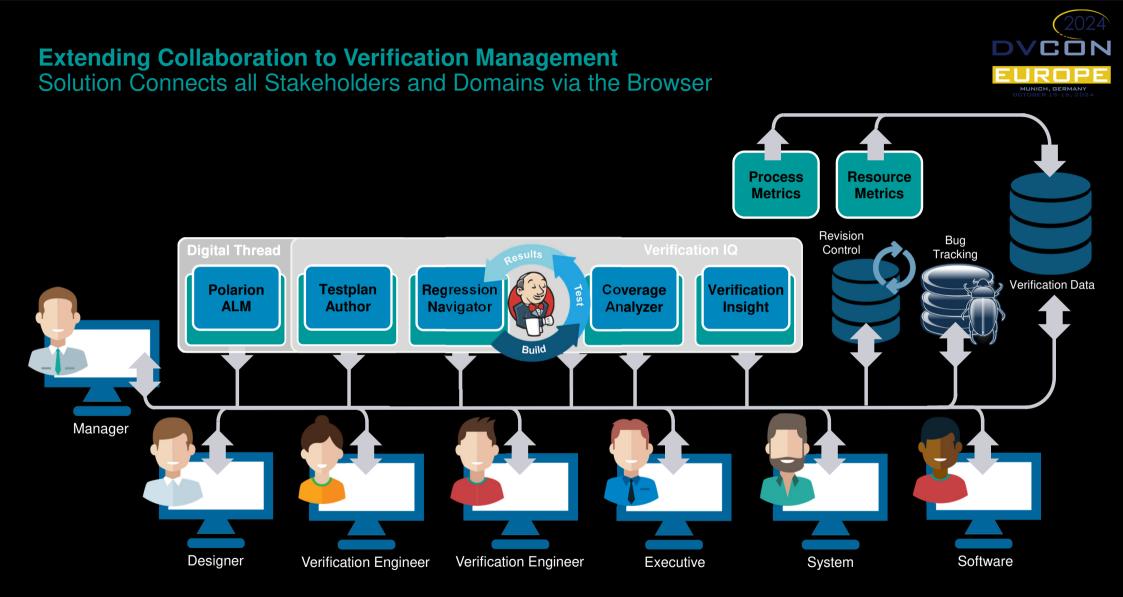

### Unified coverage and assertion analysis – Stand-alone to cloud-based collaborative workf

#### Text / HTML

- Generate coverage reports to track

verification closure

- Fast adoption but limited visualization and collaboration

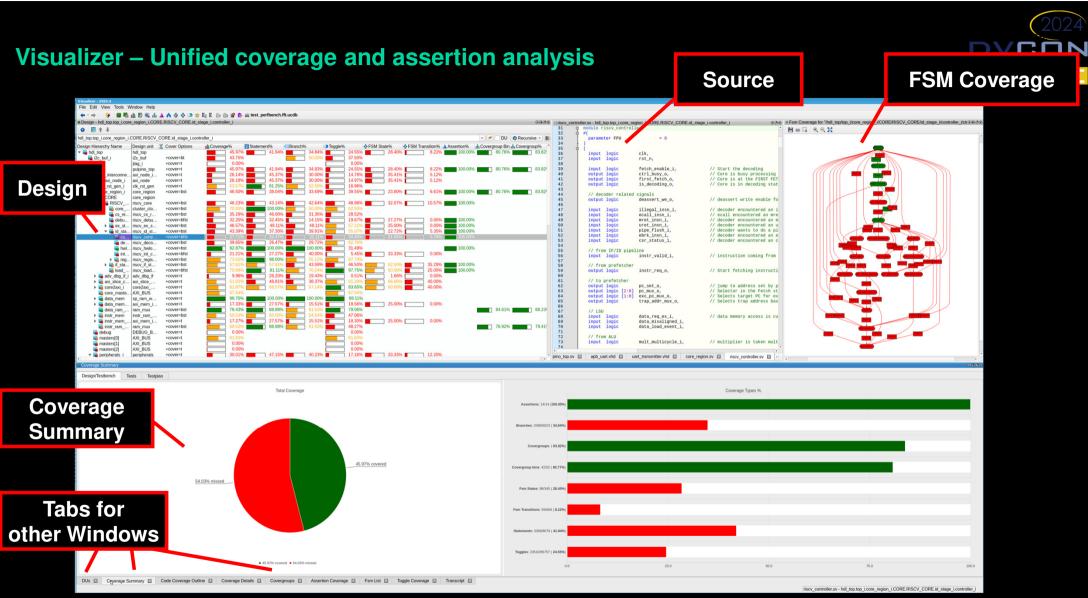

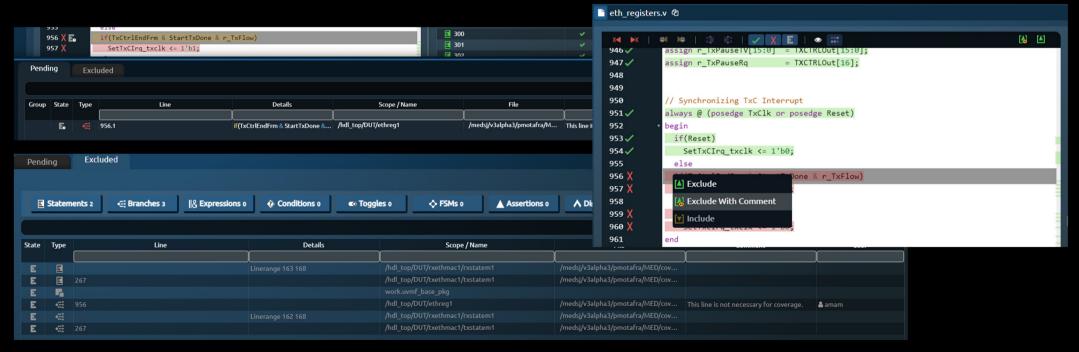

#### Visualizer

- Unified debug & coverage analysis tool

- View source code and apply exclusions

- A standalone product flow

#### **Coverage Analyzer**

- Collaborative, web-ready coverage analysis flow

- Provide critical insights with coverage heat-map and network graphs

© Siemens 2024 | HAVAC2024 | Coverage & Assertions Demo | April 2024 | Siemens Restricted

© Siemens 2024 | HAVAC2024 | Coverage & Assertions Demo | April 2024 | Siemens Restricted

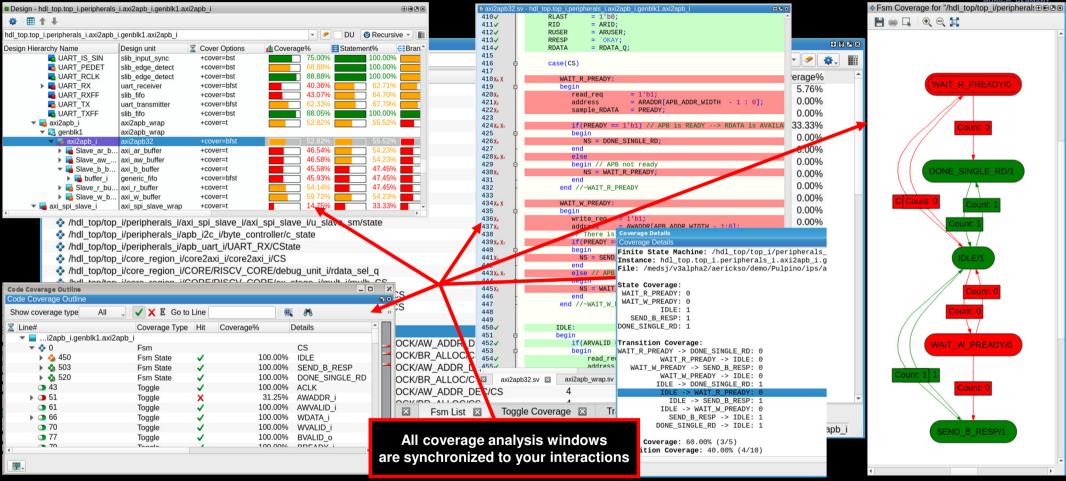

#### Visualizer – Linked windows update automatically with interactivity

#### Unified coverage is more than just a merge of databases ...

## Confidence in verification quality while meeting schedule targets

Project-level coverage analysis and traceability for robust verification closure and compliance

HW features verified from IP to system level to minimizing bug escapes into silicon

Real-world SW workloads for comprehensive validation against power/performance specs

#### Verification IQ – Collaborative Browser Based Solution Enabling Team-based Data Driven Verification

#### **Process Guide**

Plan & Requirements Driven Safety Critical Flows Lifecycle Management

#### **Regression Running**

Creation, Execution & Visibility Historical Analysis ML Acceleration and Efficiency

#### **Coverage Analysis**

Code/Functional/Testplan Hole, Test & Time Domains ML Powered Analytics

#### **Data Analytics**

Metric Platform Project Dashboards Cross Analytics

Restricted | © Siemens | Coverage Closure | DVCon Europe 2024

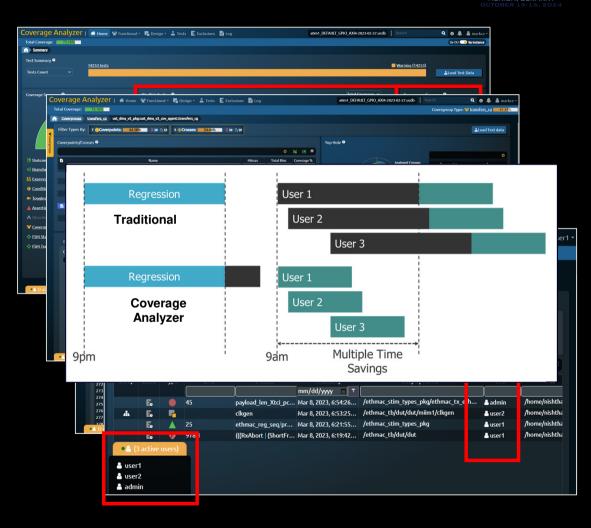

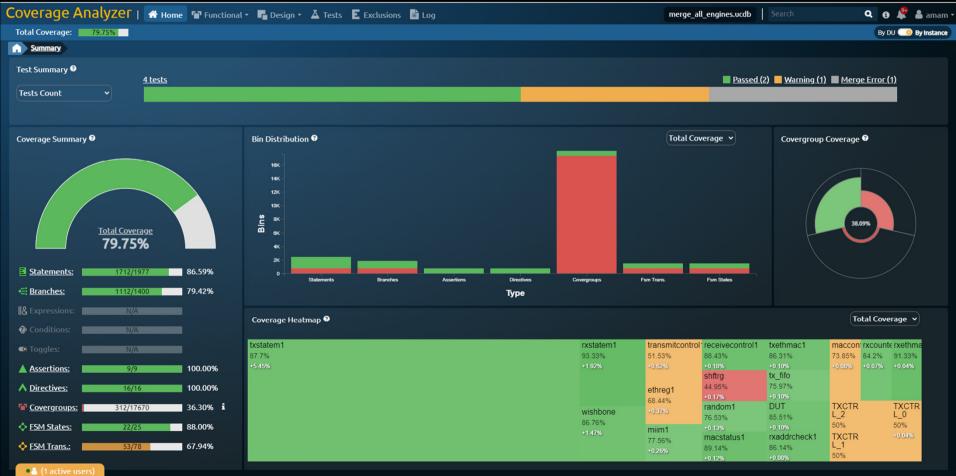

#### Verification IQ Coverage Analyzer Collaborative Data-Driven Verification Closure

#### **Coverage Closure Acceleration**

Browser-based Coverage Closure Analyze Code, Functional and Testplan Coverage Unified support of <u>Multiple Engines</u>

#### **Power of Collaborative Data Analytics**

Improved Coverage Model & Closure Understanding Analytical Navigation and Smart Visualization Adds User awareness with Questa Exclusion Flows

#### **Application Benefits**

Brings Team Based Analysis to the Questa UCDB Unique Analytics for Accelerated Understanding ML Accelerated Coverage Closure

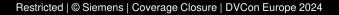

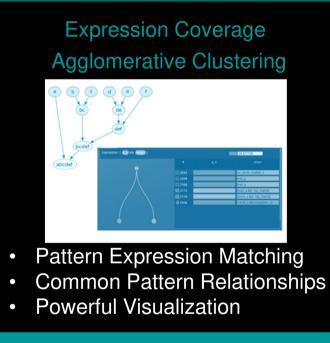

#### Pattern and Hole Analysis Guiding Closure with Analytical Visualizations Powered by ML

Benefit: Closure Acceleration

# Viewing UCDB's in Coverage Analyzer Perform analysis on individual UCDB's or a merged UCDB with unified coverage

| UCDB Browser             |                                        |                                        |                                                                                          |  |   |                                                             |   |   |  |  |

|--------------------------|----------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------|--|---|-------------------------------------------------------------|---|---|--|--|

| Include Full Path        |                                        |                                        |                                                                                          |  |   | Ad                                                          | d |   |  |  |

| File Name                | Owner                                  | Date Added                             | Users                                                                                    |  |   |                                                             |   |   |  |  |

|                          |                                        |                                        |                                                                                          |  |   |                                                             |   |   |  |  |

| 🛢 merge_all_engines.ucdb | amam                                   | Oct 24, 2023, 9:10:31 am               | • A (0 active users)                                                                     |  |   |                                                             | C |   |  |  |

| 🛢 formal_rx_fsm.ucdb     | amam                                   | Oct 24, 2023, 9:06:33 am               | Not Active                                                                               |  | ß | °°                                                          |   | Û |  |  |

| 🛢 formal_tx_fsm.ucdb     | amam                                   | Oct 24, 2023, 9:06:16 am               | Not Active                                                                               |  | ß | °°                                                          | Ø |   |  |  |

| 🛢 emu_traffic_test.ucdb  | amam                                   | Oct 24, 2023, 9:05:59 am               | Not Active                                                                               |  | ß | ø                                                           | C |   |  |  |

| sim_register_test.ucdb   | amam                                   | Oct 24, 2023, 9:05:34 am               | Not Active                                                                               |  | ß | °°                                                          | C | Û |  |  |

|                          |                                        |                                        |                                                                                          |  |   |                                                             |   |   |  |  |

|                          |                                        |                                        | CA Instance Ready                                                                        |  |   |                                                             |   | × |  |  |

| UCDB Diff                |                                        | Coverage Analyzer Instance has started |                                                                                          |  |   |                                                             |   |   |  |  |

|                          | Diffs are shown by comparing <b>UC</b> |                                        |                                                                                          |  |   | CA Instance Ready<br>Coverage Analyzer Instance has started |   |   |  |  |

| UCDB #1                  |                                        | UCDB #2                                | Coverage Analyzer is<br>Coverage summaries loaded for<br>/wv/amam/unifiedCovge_all_engin |  |   |                                                             |   | × |  |  |

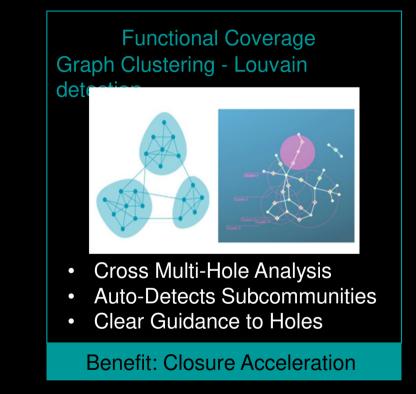

#### **Coverage Results from Unifying Coverage**

#### **Coverage Visualization and Navigation**

#### **Code Coverage**

Design

Filter Types by:

hdl top DUT

Stal

• View RTL and code coverage that was hit/missed on a line or bin basis

**||R** Expressions

Conditions

Toggles

• Filter out different code coverages

wishbone

en en

Branches

400/472

• View coverages for each instance/design unit

| Desi | gn                                                  |            |         |                     |          |          | List     | Hierarchy   | Local 💽  | Recurs |

|------|-----------------------------------------------------|------------|---------|---------------------|----------|----------|----------|-------------|----------|--------|

|      |                                                     |            |         |                     |          |          |          |             |          |        |

| Lail | Name                                                | Coverage % | Stateme | Branch %            | Fsm Stat | Fsm Tran | Assertio | Directive % | Covergro |        |

| 1.04 | eth_phy_pkg                                         | 0.09%      | _↓      | L                   | L        | l        | l        | l           | 0.09%    |        |

|      | ethmac_env_pkg                                      |            |         |                     |          |          |          |             | 1.60%    |        |

|      | <ul> <li>echnac_env_pkg</li> <li>hdl_top</li> </ul> |            |         |                     |          |          |          |             | 1.00 %   |        |

|      |                                                     | 90.71%     | 96.42%  | 85.00%              |          |          |          |             |          |        |

|      | • Fethreg1                                          |            | 92.13%  | 80.23%              |          |          |          |             |          |        |

|      | ▼ ■ maccontrol1                                     | 85.50%     | 96.00%  | 75.00%              |          |          |          |             |          |        |

|      | receivecontrol1                                     |            | 90.10%  | 86.76%              |          |          |          |             |          |        |

|      | transmitcontrol1                                    | 51.53%     | 56.52%  | 46.55%              |          |          |          |             |          |        |

|      | macstatus1                                          |            | 89.83%  | 88.46%              |          |          |          |             |          |        |

|      | ▶ 📕 miim1                                           | 78.08%     | 85.05%  | 71.11%              |          |          |          |             |          |        |

|      | 🕶 🌇 rxethmac1                                       |            | 96.07%  | 92.00%              |          |          |          |             |          |        |

|      | arcrx 📲                                             |            | 100.00% | 100.00%             |          |          |          |             |          |        |

|      | rxaddrcheck1                                        |            | 87.09%  | 85.18%              |          |          |          |             |          |        |

|      | 📑 rxcounters1                                       |            | 90.62%  | 77.77%              |          |          |          |             |          |        |

|      | 🕨 🌇 rxstatem1                                       |            | 100.00% | 100.00%             | 100.00%  | 70.00%   |          |             |          |        |

|      | 🕶 📊 txethmac1                                       |            | 93.24%  | 92.95%              |          |          |          |             |          |        |

|      | 📕 random1                                           |            | 94.73%  | 58.3 <sup>3</sup> % |          |          |          |             |          |        |

|      | txcounters1                                         |            | 95.65%  | 86.66%              |          |          |          |             |          |        |

|      | txcrc 📲                                             |            | 100.00% | 100.00%             |          |          |          |             |          |        |

|      | txstatem1                                           |            | 100.00% | 96.05%              | 81.25%   | 66.66%   |          |             |          |        |

| eth_wishbone   | e.v @                                                                                                                | <b>E</b> (589/                       | 662) (400/472) | <b>ۇ(0/0) ∞(</b> 0/0 | ) 💠 (0/0) 💠 | r (0/0) ▲(0/0) ▲(0/0)                                                                              |

|----------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------|----------------------|-------------|----------------------------------------------------------------------------------------------------|

| X4 • × + •     | et le   3 ki   <mark>∕ X</mark> E   ● III                                                                            | Outl                                 | ine 🔐 Patterns |                      |             | P Enable Related Coverage                                                                          |

| 744 √<br>745 √ | WbEn <= 1'b1;<br>RxEn <= 1'b0;                                                                                       | X                                    | 🗙 ei ie 🧕 🗸    | XE                   |             |                                                                                                    |

| 746 ✓<br>747 ✓ | TxEn <= 1'b0;<br>ram addr <= 8'h0;                                                                                   |                                      | Line#          | Hit                  | Coverage    | Details                                                                                            |

| 748 🗸          | ram_di <= 32'h0;                                                                                                     | <b>E</b> 688                         |                | ~                    |             | assign m_wb_bte_o = 2'b00; // Linear burst                                                         |

| 749 ✓<br>750 ✓ | BDRead <= 1'b0;<br>BDWrite <= 0;                                                                                     | <ul> <li>690</li> <li>692</li> </ul> |                | ~                    |             | assign m_wb_stb_o = m_wb_cyc_o;<br>always @ (posedge WB_CLK_I)                                     |

| 751<br>752 √   | end                                                                                                                  | <b>E</b> 694                         |                | ~                    |             | WB_ACK_O <= (IBDWrite) & WbEn & WbEn_q   BDRead                                                    |

| 753 -          | begin                                                                                                                | <ul> <li>697</li> <li>719</li> </ul> |                | ~<br>~               |             | assign WB_DAT_O = ram_do;<br>assign ram_ce = 1'b1;                                                 |

| 754<br>755 •   | <pre>// Switching between three stages depends on enable signals /* verilator lint_off CASEINCOMPLETE */ // JB</pre> | <b>2</b> 720                         |                | <b>v</b>             |             | assign ram_we = (BDWrite & {4{(WbEn & WbEn_q)}})                                                   |

| 756 X<br>757 ✓ | <pre>case ({WbEn_q, RxEn_q, TxEn_q, RxEn_needed, TxEn_needed}) // synopsys parallel<br/>5'b100 10, 5'b100 11 :</pre> | 2 727                                |                | *<br>*               |             | assign ram_oe = BDRead & WbEn & WbEn_q   TxEn & Tx<br>always @ (posedge WB_CLK_I or posedge Reset) |

| 758            | begin                                                                                                                | € 729.                               | 1              | ×                    |             | All False                                                                                          |

FSM States

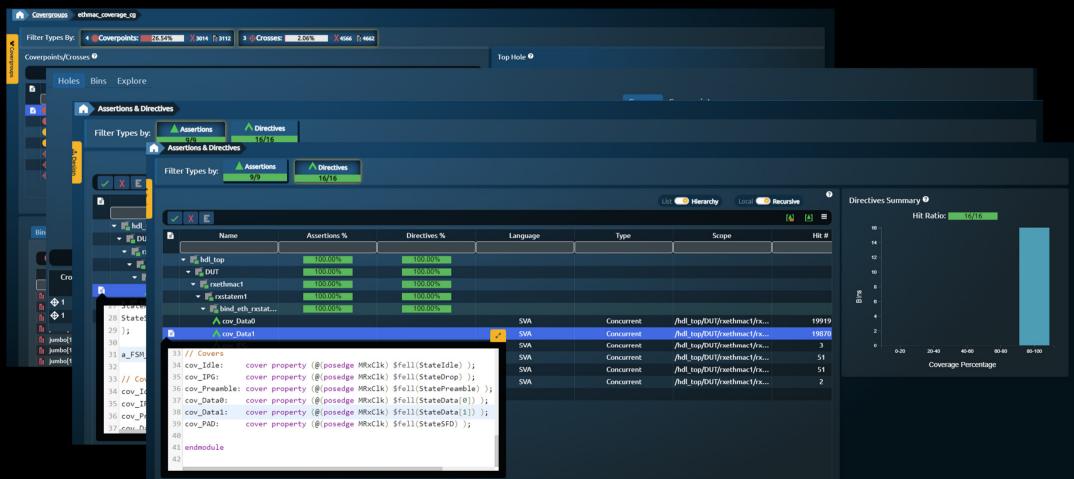

#### **Functional Coverage** Covergroups, Assertions, Directives (Covers)

#### **Coverage Exclusions**

- Add exclusions through GUI to any code, functional, or design units/instances

- 2 step exclusion flow provides a way to help prevent invalid exclusions from being applied

- Export and import existing exclusions for future use

#### Agenda

- The Case for Unified Coverage

- Simulation & Emulation Coverage

- Formal Coverage

- Coverage Merge

- Unified Coverage Analysis

- Conclusion and Q&A

#### **Coverage - Call On Your Engines**

- Coverage is not only simulation:

- Take coverage credit for your formal proofs

- Take coverage credit for emulation long / software payloads

- Generate the same database from any source of coverage

- Merge seamlessly within a unified environment

Questions

# Thank You