DVCon Japan 実行委員会 細川博司・三橋明城男

# アジェンダ

- PSSの概要と現在の状況

- ディスプレイコントローラの適用例

- メモリ&キャッシュの適用例

- SoCレベルの適用例

- ・まとめ

## 機能検証における最大の課題

デザインを検証する充分なテストの作成 機能検証のカバレッジの把握 ■ ASIC-2012 検証プロセスの管理 FPGA-2012 ■ ASIC-2014 FPGA-2014 バグ特定から改修までの時間 ■ ASIC-2016 ■ FPGA-2016 ■ ASIC-2018 次のバグ特定までの時間 ■ FPGA-2018 ■ ASIC-2020 適切なカバレッジ指標の定義 ■ FPGA-2020 その他 Source: Wilson Research Group and Mentor, A Siemens Business, 2020 Functional Verification Study 0% 5% 10% 15% 20% 30% 35% 40% 45% 25%

# メソドロジのシフトには新たな発想が必要

- SystemVerilogは検証に新たなアプローチをもたらした

- 他の独自言語からの機能を標準言語で実現

- ディレクテッドテスト → 制約付きランダムテスト

- 制約付きランダムには何が起きたかを知る機能カバレッジが必要

- エコシステムの醸成には詳細な仕様が必要

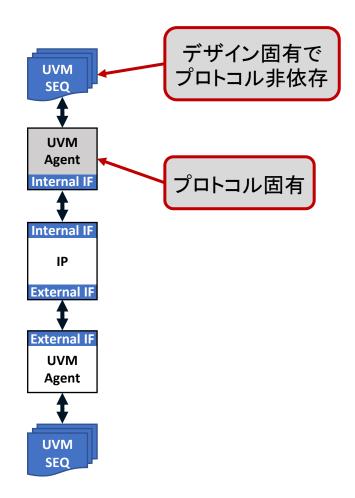

### UVMは "How" - どう検証するかが焦点

- ブロックレベル検証に最適

- モジュラー化され再利用可能な検証コンポーネント

- What と How の分離

- 構成可能なトランザクションレベルのシーケンス

- ドライバ/モニタがトランザクションと信号間を変換

- 抽象的なシーケンスを異なるエージェントに適用

- ・シーケンスは "What"

- エージェントはプロトコル固有の "How"

- IPのインタフェースは同じアプローチを用いる

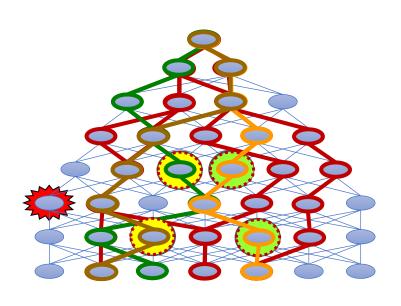

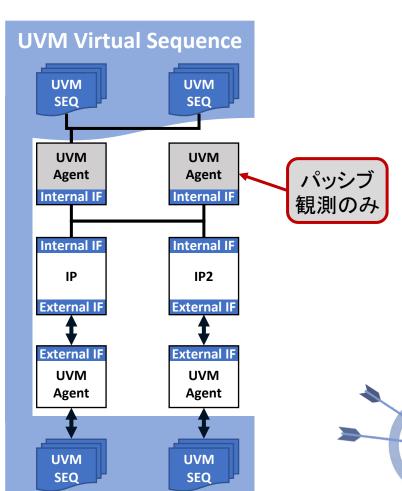

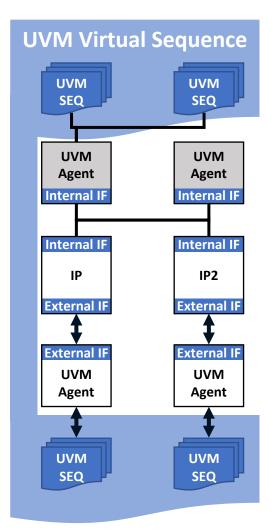

# UVMは "How" - どう検証するかが焦点

- すべてのテストやテストベンチは共通の基本構造を 持つ

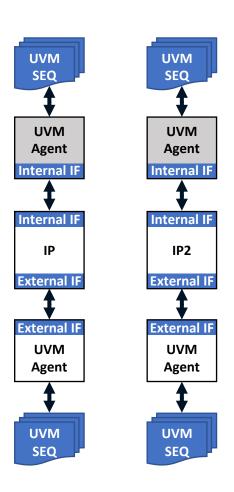

- ・水平方向の再利用

- 同じインタフェースを持つ異なるブロックで共通のエージェントが使用できる

# UVMは "How" - どう検証するかが焦点

- すべてのテストやテストベンチは共通の基本構造を 持つ

- 水平方向の再利用

- 同じインタフェースを持つ異なるブロックで共通のエージェントが使用できる

- ブロックレベルの環境をコンフィギュレーションし、コンポーネントを再利用する

- ブロック用のテストはVirtual Sequenceから呼出される

10年前はこれが正しいターゲットだった

**UVM Virtual Sequence**

# ターゲットが変わるのが検証

・ブロックレベルのテストはSoCにスケールしない

ASM:C == Gate:RTL == UVM:?

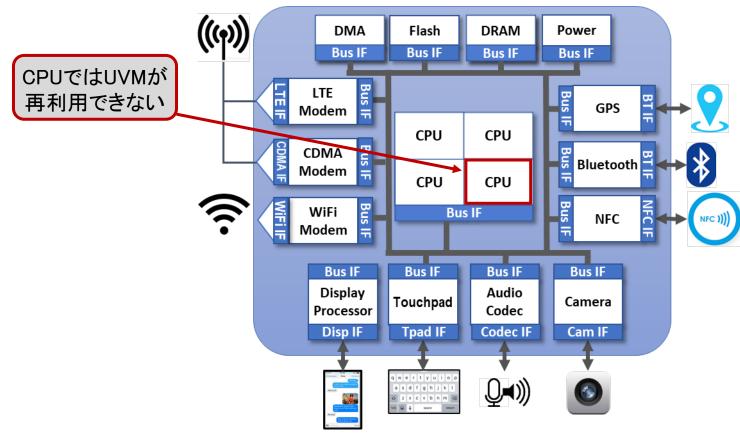

# 組込みプロセッサを含むSoCの検証

- 通常はマニュアルでCコードを記述

- ランダムによるカバレッジ改善は不可

- ・マニュアルコードのIPライブラリ

- IPの再利用は困難

- テスト空間を手続的にモデル化する 必要がある

- ビデオデータは複数ソースから来る

- DMAが Nチャネルある

- グラフィクスは使用前にパワーアップ

- ・パワーマネジメントのシーケンス

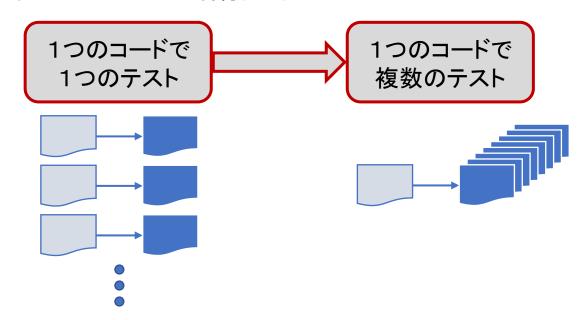

# SoC検証に対して自動化が適用できたら

1つの定義指定 – 複数のテスト

・テスト空間をフォーマル定義することで ツールがシステム制約を満たし

ながらテストを生成可能にする

・1つの定義指定からテスト分散

プロセッサでインテントを再利用

パーティショニングと調整を 自動化

・シナリオレベルでの制約付きランダムで バグを特定

# より高位におけるスティミュラス

- UVM Sequenceはトランザクションのセットを定義

- トランザクション内容をランダム化

- トランザクションのフローは明示的にランダム化できない

- ・シーケンス間におけるランダム 化が難しい

- ・シナリオは動作のセットを定義

- 重要な検証インテントを定義

- 重要なインテントをサポートする ルールを定義

• 単純なPSSの定義から複数の

シナリオが 生成できる

#### PSSは制約付きランダムをシナリオ生成に適用

- PSSの部分的な指定で重要な検証インテントを定義

- コーディングして期待する必要がない

- SVの機能カバレッジより直感的かつ直接的

- ルールによりツールが追加アクションを挿入可能

- ・シナリオをランダム生成を可能に

- 各シナリオはリーガルであることが保証される

- 特定のアクションを制約

- アクション間のスケジュール関係を制約

### Portable Stimulusのキーポイント

テストインテントを キャプチャ

部分シナリオを 定義

構成可能な シナリオ

テスト空間の フォーマルな表現

テストを 自動生成

複数の実装を ターゲットに

分離されたテストインテント

独立したテスト実装

検証プロセスにわたって 高いカバレッジを実現するテストを より少ない労力で生成

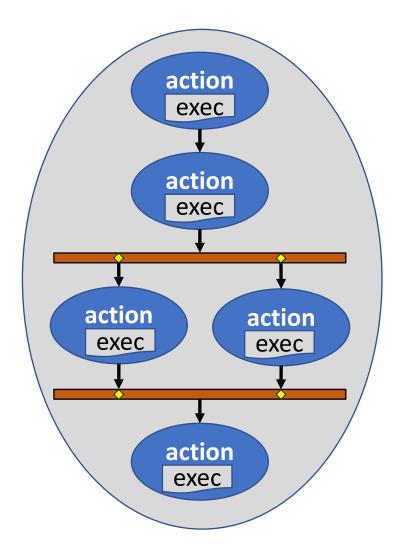

#### Portable Stimulus Model とは?

抽象化モデル

What = 何を行うか

リアライ ゼーション レイヤー

How = 行う内容を どう実現するか

#### 伝えたいこと

#### 重要な動作をアクティビティで定義する

- 仕様の一部のみを定義することが可能

- ツールはシナリオを完成させるために他の要素を追加

#### モデルのその他の部分では動作が どのように相互作用するかを定義する

- インスタンス化されたコンポーネントが利用可能なアクションを定義

- フロー・オブジェクトのバインディングにより推論の選択 肢が制約される

- 利用可能なリソースによりスケジューリングの選択肢が 制約を受ける

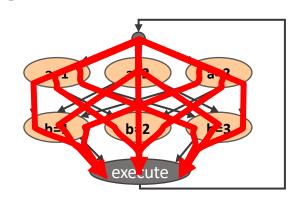

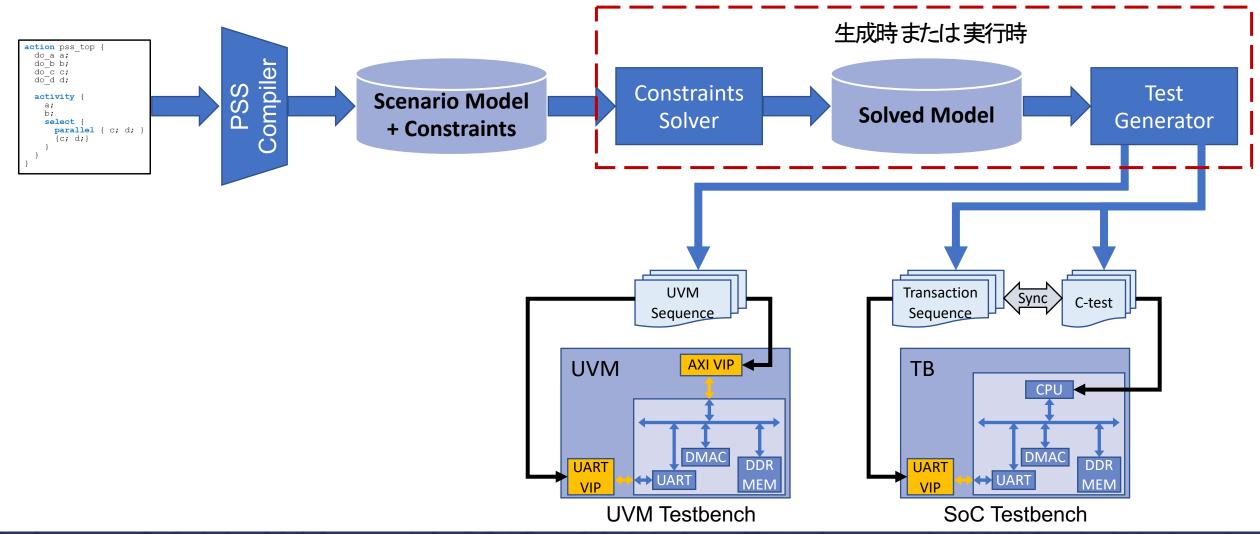

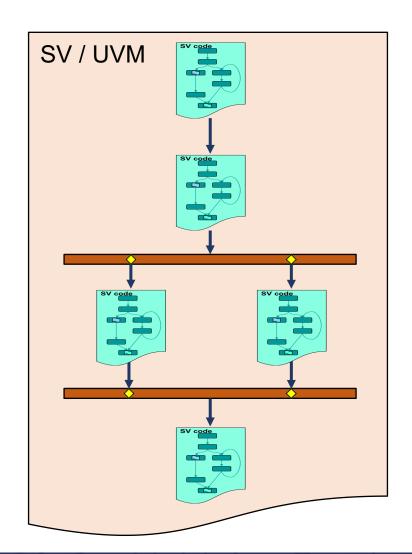

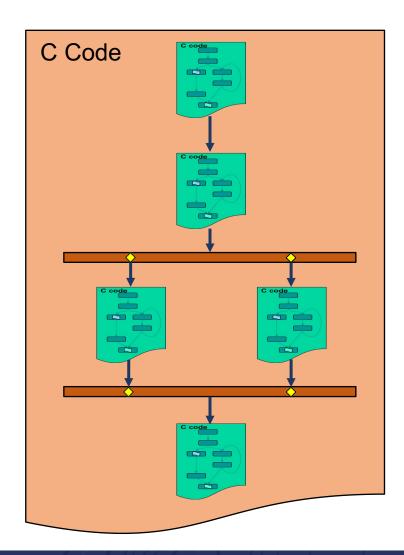

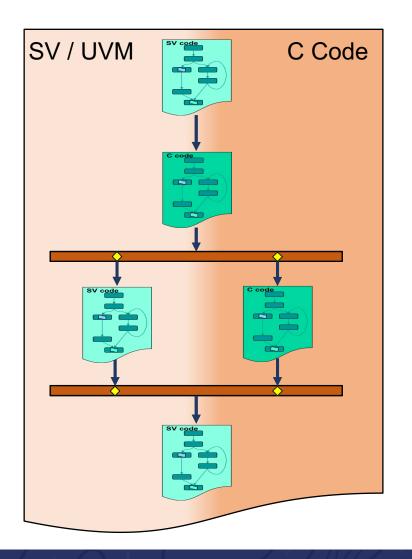

## タイヤが道路に出会うように・・・

抽象化モデルは異なるターゲット上で 実装できなくてはならない

不可分なアクションをターゲット上の コードとしてexecブロックにモデル化

ツールはアクティビティのスケジュー ルに従いターゲットコードを構築する

## 一般的なPSSフロー

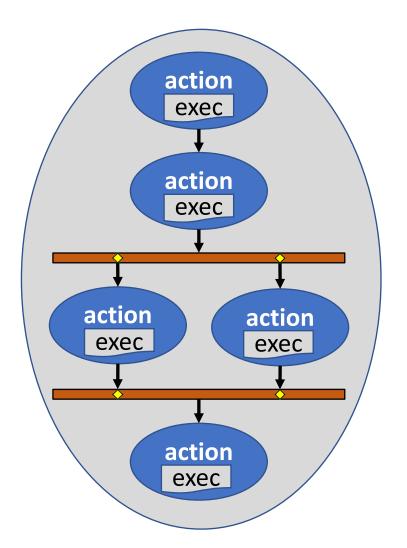

# コード生成はアクティビティのスケジュールに従う

#### 生成コードはアクティビティのスケジュールに従う

# アジェンダ

- PSSの概要と現在の状況

- ディスプレイコントローラの適用例

- メモリ&キャッシュの適用例

- SoCレベルの適用例

- ・まとめ

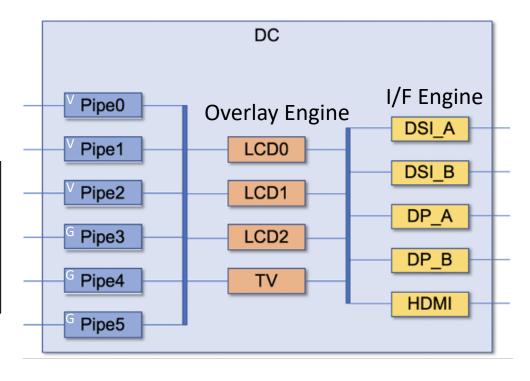

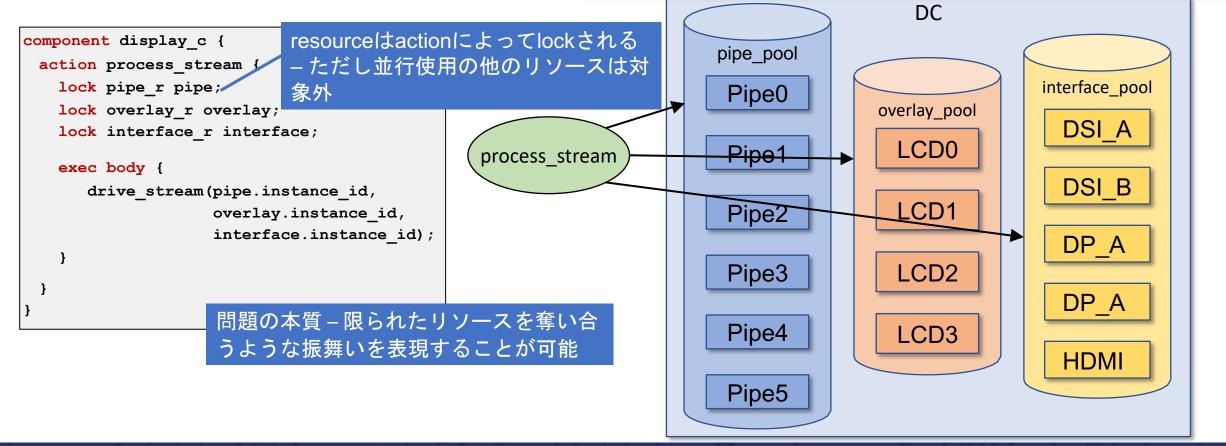

### 概要

- •このセクションの目的

- ・ 典型的なIP検証問題に対するPSSの適用を紹介

- PSSのリソースプールとクレームの意味、使い方を解説

- PSSによるシナリオのモデリングの主なメリットをSystemVerilogとの対比において解説

- ・このセッションの構成

- ・検証の課題 ディスプレイコントローラにおけるデータパスの活性化

- SystemVerilogによるシナリオ空間のモデリングとその限界

- ・ PSSによるシナリオ空間のモデリング 一般的な解決策

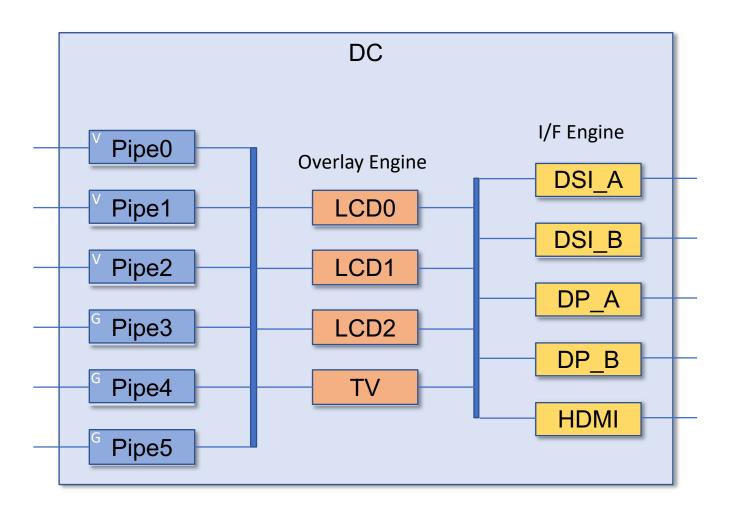

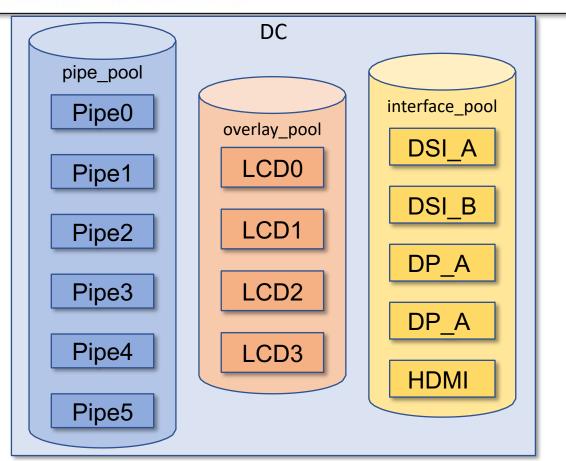

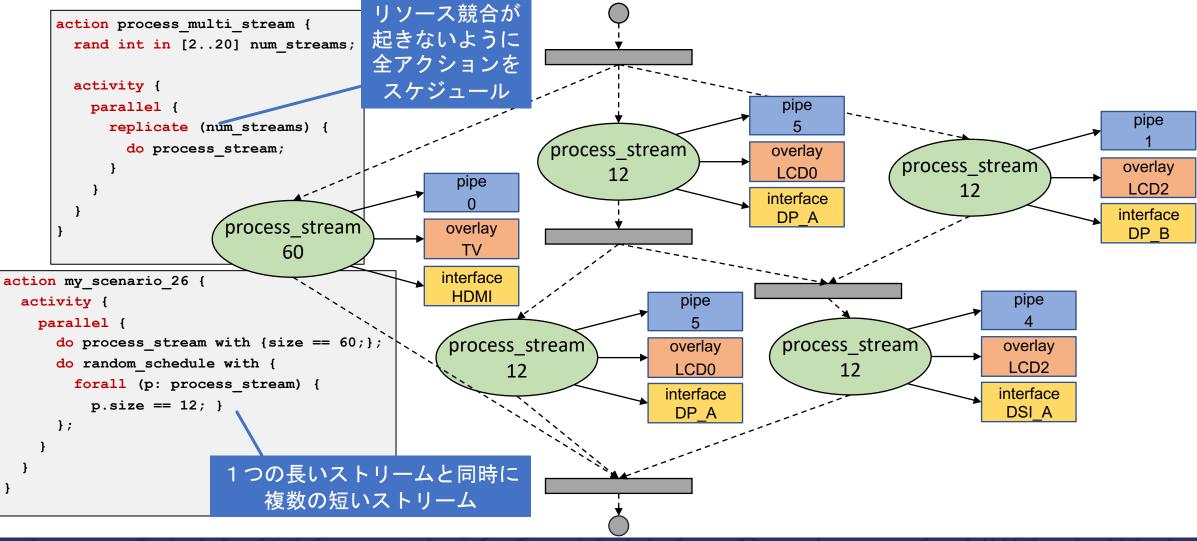

# ディスプレイコントローラの解説

- ・処理用パイプx6

- Pipe 0..2 はVideo用

- Pipe 3..5 はGraphics用

- ・オーバーレイエンジンx4

- LCD0, LCD1, LCD2, TV

- インタフェースエンジンx5

- DSI\_A, DSI\_B, DP\_A, DP\_B, HDMI

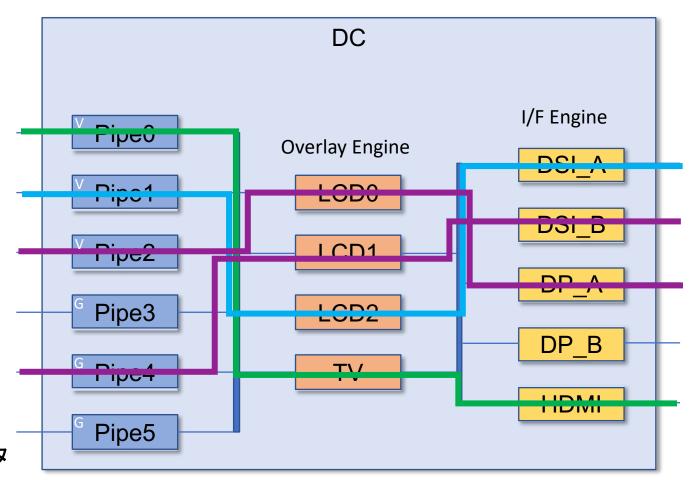

# ディスプレイコントローラの解説(続き)

- 各エンジンは同時には1つの データストリームのみを処理

- 1..4のストリームを同時処理

- ・データパスのルール

- Video Pipeはオーバーレイエンジン LCD1にデータ渡し不可

- Graphics Pipeはオーバーレイエンジン LCD0にデータ渡し不可

- LCD0はDP Aのみにデータ渡し可

- LCD1はDSI A / DSI Bにデータ渡し可

- LCD2はDSI\_A、DSI\_B / DP\_Bにデータ 渡し可

- TVはDP\_AまたはHDMIにデータ渡し可

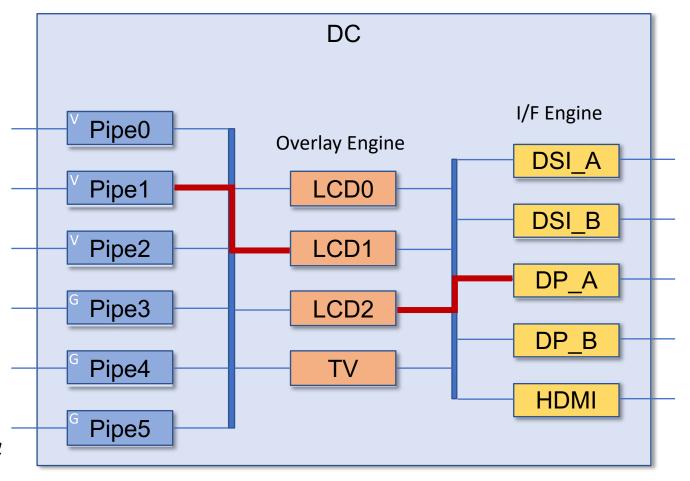

# ディスプレイコントローラの解説(続き)

- 各エンジンは同時には1つの データストリームのみを処理

- 1..4のストリームを同時処理

- ・データパスのルール

- Video Pipeはオーバーレイエンジン LCD1にデータ渡し不可

- Graphics Pipeはオーバーレイエンジン LCD0にデータ渡し不可

- LCD0はDP\_Aのみにデータ渡し可

- LCD1はDSI A / DSI Bにデータ渡し可

- LCD2はDSI\_A、DSI\_B / DP\_Bにデータ 渡し可

- TVはDP AまたはHDMIにデータ渡し可

# SVによるデータストリームのモデリング

```

typedef enum {VID, GFX} pipe kind e;

typedef enum {LCD0, LCD1, LCD2, TV} overlay kind e;

typedef enum {DSI A, DSI B, DP A, DP B, HDMI}

interface kind e;

データパスに割り上てた

class process_stream extends uvm object;

ストリームのフィールドを

rand int pipe id;

ランダム宣言している

rand overlay kind e overlay kind;

rand interface kind e interface kind;

rand pipe kind e pipe kind;

constraint pipe kind c {

pipe kind == VID -> pipe id inside {0,1,2};

pipe kind == GFX -> pipe id inside {3,4,5};

process_stream

. . .

pipe id

endclass:

overlay kind

interface kind

```

# SVによるデータパスのルール設定

process stream

```

class process_stream extends uvm_object;

...

constraint pipe2overlay_c {

pipe_kind == GFX -> overlay_kind != LCD0;

pipe_kind == VID -> overlay_kind != LCD1;

}

constraint overlay2interface_c {

overlay_kind == LCD0 -> interface_kind == DP_A;

overlay_kind == LCD1 -> interface_kind inside {DSI_A, DSI_B};

overlay_kind == LCD2 -> interface_kind inside {DSI_A, DSI_B, DP_B};

overlay_kind == TV -> interface_kind inside {DP_A, HDMI};

}

...

endclass;

```

- rerlay\_kind

rerface\_kind

Graphics PipeはオーバーレイエンジンLCD0にデータ渡し不可

- Video PipeはオーバーレイエンジンLCD1にデータ渡し不可

- LCD0はDP Aのみにデータ渡し可

- LCD1はDSI\_AまたはDSI\_Bにデータ渡し可

- LCD2はDSI\_A、DSI\_BまたはDP\_Bにデータ渡し可

- TVはDP AまたはHDMIにデータ渡し可

# SVによる並列ストリームのモデリング

```

class process multi stream extends uvm object;

1~4の並列

rand process stream streams[];

ストリーム数

constraint num streams {

stream.size inside {[1:4]};

pipe, overlay, interface t

constraint resource unique c {

ストリームごとに異なる種類

foreach (streams[i]) {

でなくてはならない

foreach (streams[j]) {

if (i != j) {

streams[i].pipe id != streams[j].pipe id;

streams[i].overlay kind != streams[j].overlay kind;

streams[i].interface kind != streams[j].interface kind;

endclass;

SV/UVMコードのオーバーヘッド

-> コンストラクタ、配列アロケート、

uvm object utils .....

```

```

process_multi_stream

streams[0]

pipe id = 1

overlay kind = LCD2

interface kind = DSI A

streams[1]

pipe id = 2

overlay kind = LCD0

interface kind = DP A

streams[2]

pipe id = 4

overlay kind = LCD1

interface kind = DSI B

```

### どのように一般化するか?

- これまでに達成したこと

- 複数の並列ストリーム間における制約関係のモデリング

- しかしこの例に特化している

- まだ足りていないことは?

- 他のストリーム処理が進む間に新たなストリームを開始/停止できること

- 異なる機能/処理時間のタスクを行うエンジン間での負荷分散

- ストリームのランダムな、または複雑なスケジュールの生成

- •

- このような問題の本質はSystemVerilogでモデリングできない ---問題の本質:限られたリソースを奪い合うようなタスクの表現 .....

# リソースをPSSでモデリング

```

component display c {

resourceオブジェクトの

enum pipe_kind_e {VID, GFX}; タイプで、アトリビュートや

制約を含むことが可能

resource pipe r {

rand pipe kind e kind;

constraint {

ビルトインアトリビュート

kind == VID -> instance_id in [0..2]; である instance_id はPool内

kind == GFX -> instance id in [3..5]; のインデックスを示す

Poolにはリソースタイプを N

インスタンス含むむことが可能

pool [6] pipe r pipe pool;

enum overlay kind e {LCD0, LCD1, LCD2, TV};

resource overlay r {

rand overlay kind e kind;

ユーザ定義の列挙型属性によ

constraint {instance id == (int)knd;

りインスタンスに意味ある名

称が関連付けられる

pool [4] overlay r overlay pool;

enum interface kind e {DSI A, DSI B, DP A, DP B, HDMI};

resource interface r {

rand interface kind e kind;

constraint instance id == (int)kind;

pool [5] interface r interface pool;

```

#### 15. Resource objects

Resource objects represent computational resources available in the execution environment that may be assigned to actions for the duration of their execution.

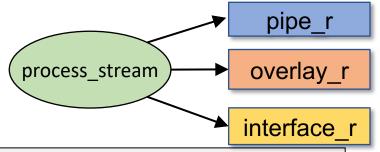

# 1つのデータストリームのモデリング

#### 15. Resource objects

Resource objects represent computational resources available in the execution environment that may be assigned to actions for the duration of their execution.

# データパスのルールを指定

```

action process_stream {

. . .

constraint pipe2overlay_c {

pipe.kind == GFX -> overlay.kind != LCD0;

pipe.kind == VID -> overlay.kind != LCD1;

}

constraint overlay2interface_c {

overlay.kind == LCD0 -> interface.kind == DP_A;

overlay.kind == LCD1 -> interface.kind in [DSI_A, DSI_B];

overlay.kind == LCD2 -> interface.kind in [DSI_A, DSI_B, DP_B];

overlay.kind == TV -> interface.kind in [DP_A, HDMI];

}

}

```

データパス指定におけるPSSの制約指定は SystemVerilogの制約とそれほど変わらない

- Graphics PipeはオーバーレイエンジンLCD0にデータ渡し不可

- Video PipeはオーバーレイエンジンLCD1にデータ渡し不可

- LCD0はDP\_Aのみにデータ渡し可

- LCD1はDSI\_AまたはDSI\_Bにデータ渡し可

- LCD2はDSI A、DSI BまたはDP Bにデータ渡し可

- TVはDP AまたはHDMIにデータ渡し可

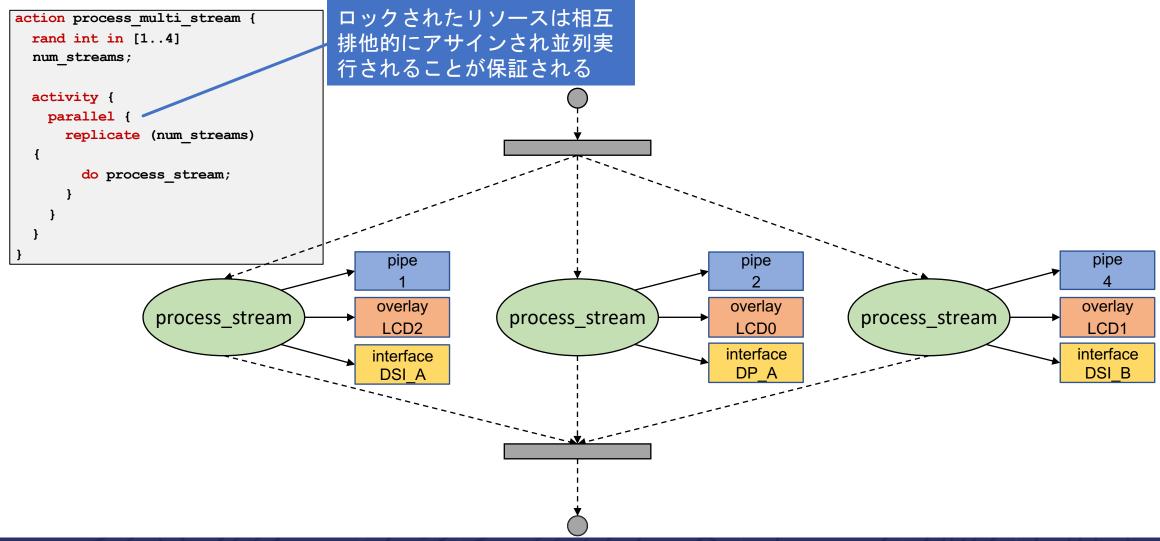

# 並列にストリームをドライブ

# 任意のスケジューリングを生成する

#### このセクションのまとめ

- ・PSSはリソースプールやクレームなどハイレベルなモデリングのコンストラクトをサポート

- コンストラクトでは設計/テストの動作間の依存関係を自然に表現

- 単純ではないフローやスケジューリングを容易に記述したりランダム 化することが可能

- SystemVerilogを始めとする検証言語ではデータの制約付きランダムをサポートし、単純ではないフローやスケジューリングは難しい

# アジェンダ

- PSSの概要と現在の状況

- ディスプレイコントローラの適用例

- メモリ&キャッシュの適用例

- SoCレベルの適用例

- ・まとめ

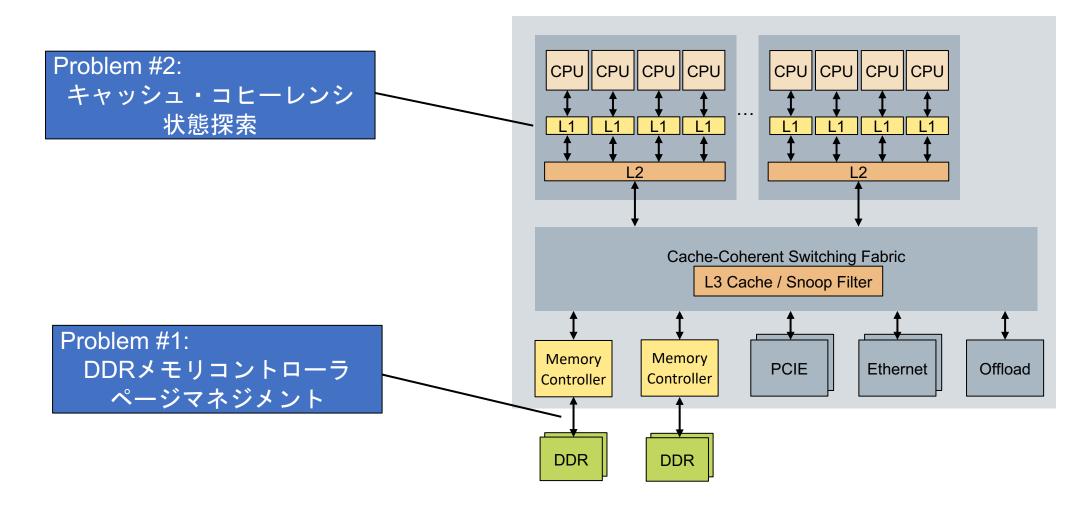

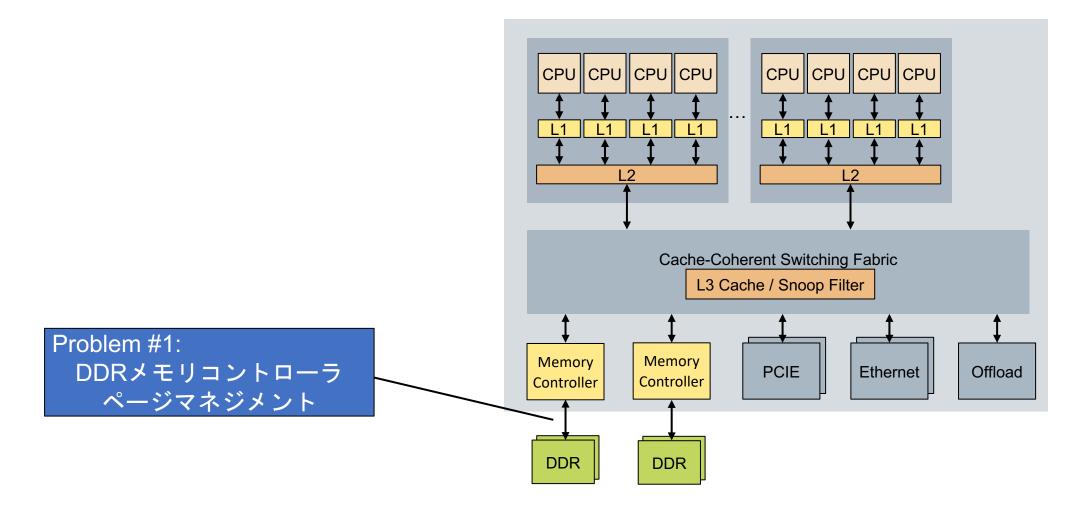

#### このセクションの流れ

- Problem #1: DDR メモリコントローラ・ページマネジメント

- Problem #2: キャッシュ・コヒーレンシの状態遷移の探索

- Problem #3: Problem #1とProblem #2の同一シナリオでの組合せ

- SystemVerilogによるシナリオ・モデリングの課題

- Executor、メモリのモデリングと基本的な read/write テスト

- Solution #1: DDRのページマネジメントをPSSでモデル化

- Solution #2: キャッシュ・コヒーレンシの状態探索をPSSでモデル化

- Solution #3: DDRページマネジメントとキャッシュ・コヒーレンシを組合せたシナリオ

### 問題を解決する多くのソリューション

• Problem #1とProblem #2はそれぞれ独立していれば、より単純に解決可能

このセクションではオペレーションのシーケンスを作成する2つの異なるアプローチと、それをどのように組合せてクロスカバレッジを取るかについて解説

# 解決すべき問題

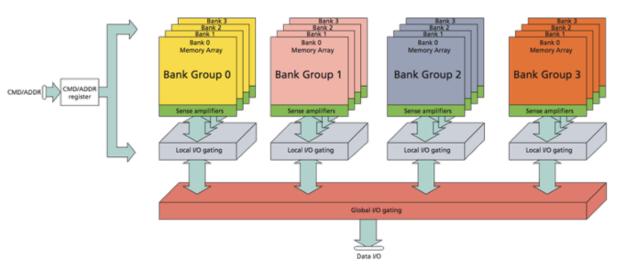

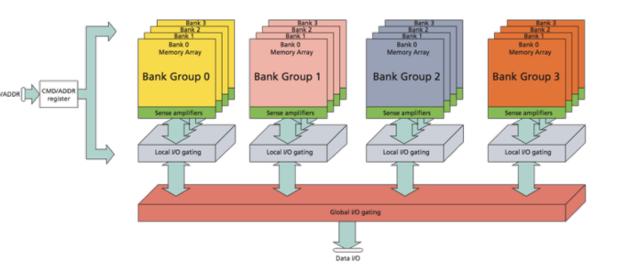

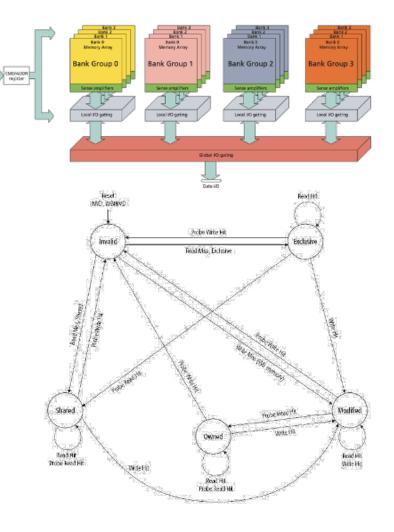

#### Problem #1: DDRページマネジメント

- DDRはページで構成される

- group、bank、row、column で特定 (MO/ADDR) Projuter

- 同一ページ内は高速アクセス

- メモリコントローラはリフレッシュのインタリーブが必要

- 異なるページへのアクセスは遅い

目的:メモリコントローラのページマネジメントをストレス検証するための read/write アドレスのシーケンスを生成する

#### 4 Gb Addressing Table

| Configuration  |                      | 1 Gb x4 |

|----------------|----------------------|---------|

| Bank Address   | # of Bank Groups     | 4       |

|                | BG Address           | BG0~BG1 |

|                | Bank Address in a BG | BA0~BA1 |

| Row Address    |                      | A0~A15  |

| Column Address |                      | A0~A9   |

| Page size      |                      | 512B    |

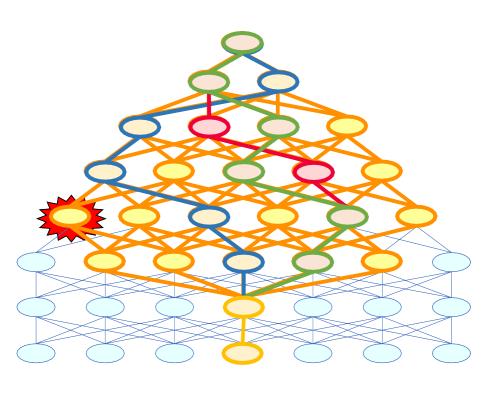

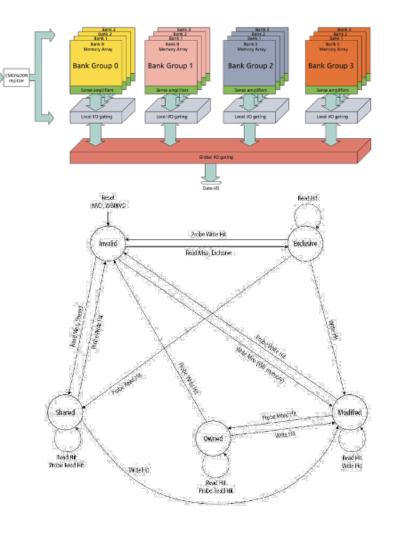

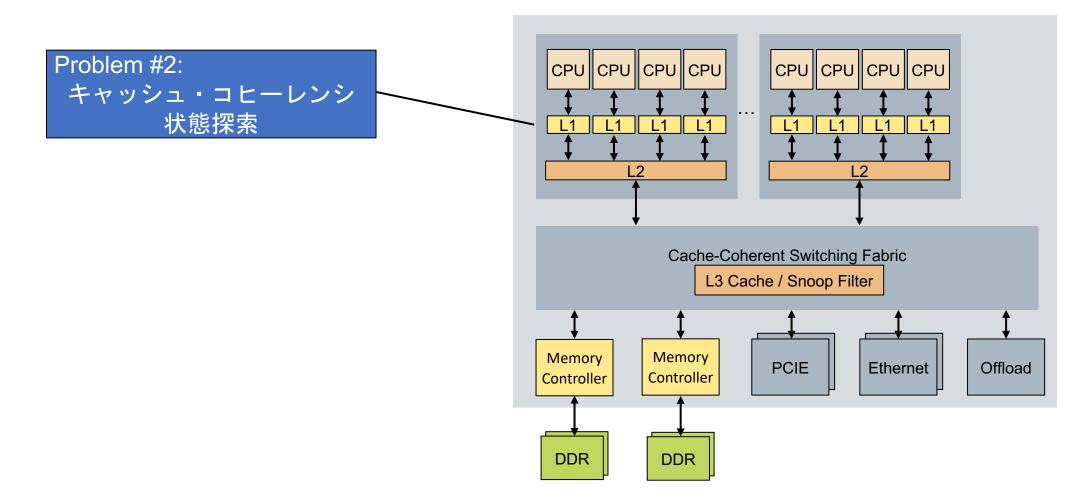

#### Problem #2: キャッシュ・コヒーレンシ状態探索

• SoCには複数段のキャッシュが存在

キャッシュレベルごとに異なる コヒーレンシ・プロトコルが 存在し得る

目的:適切なコア上でスケジューリング されるすべてのコヒーレンシの遷移を探 索するオペレーションのシーケンスを生 成する

# Problem #3: Problem #1 と #2の組合せ

- キャッシュの状態探索においてさまざまなタイミングでDDRメモリにアクセスしなくてはならない

- DDRのread/writeオペレーションはアドレスのページマネジメントのパターンに基づいて異なるタイミングになる

- 目的: DDRページマネジメントにストレスを与えながら、すべてのコヒーレンシの遷移を探索するように、適切なコア上にスケジュールされたオペレーションシの一ケンスを生成する

#### SystemVerilogによるシナリオモデリングの課題

- Problem #1(DDRページマネジメント)もProblem #2(キャッシュ・コヒーレンシの状態遷移)も、異なるCPUコアを超えてスケジュールされる関連オペレーションのシーケンスが必要

- UVM/SystemVerilogでネイティブにモデリングすることが困難

- このような問題に対してPSSは簡潔なソリューションを提供する

#### 基本となる Read/Write テスト

大切なポイント: ランダムな read/write テストが簡単に作れること

- ・システム内にExecutorのコアがいくつ存在するかを定義

- 使用可能なシステムメモリを定義

- 基本的な read/write オペレーションを定義

- ランダムなアドレスジェネレータを定義

- これらすべてを集約する

# Executorとシステムメモリのコンフィギュレーション

```

システムでいくつのcoreが使えるかを定義

package config pkg {

各executorにはそのidとともに"trait"がある

const int NUM CORES = 4;

struct core traits s : executor trait s {

rand int in [0 .. config pkg::NUM CORES -

1] core id;

"trait"を持つcoreの配列

component cores c : executor group_c<core_traits_s>

component pss top rand addrs c {

executor c<core traits s> cores

transparent addr space c<> sys mem;

[config pkg::NUM CORES];

exec init up {

exec init down {

各core_idを初期化

foreach (c : cores[i]) {

transparent addr region s<> region;

region.size = ( 1 << 40 );

c.trait.core id = i;

add executor(c);

region.addr = 0x80000000;

使用可能なシステム

(void) sys mem.add region(region);

メモリの宣言

```

※ "trait" は特質という意味、PSS仕様書では Executor などのコアライブラリに定義されているアトリビュートのため英語とした

# 基本的な read/write 動作: State Object

```

State Objectは次の動作で使う

メモリアドレスを追跡

state addr_s {

rand bit[64] addr;

rand transparent_addr_claim_s <> claim;

constraint claim.addr == addr;

constraint claim.size in [1,2,4,8];

}

read/write の自然なサイズへと制約

```

# 基本的な read/write 動作

#### State Objectの入力

```

component mem ops c {

ランダムなCPU coreの claim

action write a

input addr s inp;

rand executor_claim_s<core_traits_s> core;

rand bit [64] data;

exec body {

addr handle t h = make_handle_from_claim(inp.claim);

match (imp.claim.size) {

[1]: write8(h, data[7:0]);

[2]: write16(h, data[15:0]); claimからハンドルをゲット

[4]: write32(h, data[31:0]);

[8]: write64(h, data[63:0]);

writeの実行

```

```

action write a {

input addr s inp;

rand executor claim s<core traits s> core;

bit [64] data;

exec body {

addr_handle_t h = make_handle_from_claim(inp.claim);

match (imp.claim.size) {

[1]: data[7:0] = read8(h);

[2]: data[15:0] = read16(h);

[4]: data[31:0] = read32(h);

[8]: data[63:0] = read64(h);

} // mem ops c

```

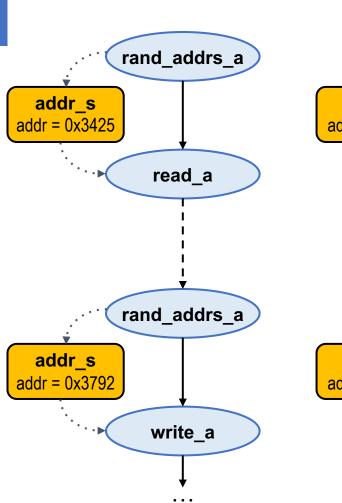

# ランダムアドレス生成とインスタンス化

```

component rand_addrs_c {

action rand_addrs_a {

output addr_s out;

}

制約を受けない

ランダムなアドレスを出力

```

```

component rand_addr_test_c {

rand_addr_c rand_addrs;

mem_ops_c mem_ops;

pool addr_s addr_p;

bind addr_p *;

action rand_addr_test_a {

activity {

do rand_addrs_c::rand_addrs_a;

select {

do mem_ops_c::write_a;

do mem_ops_c::read_a;

} }

}

```

### 基本的なメモリテスト

```

システムで使用可能な

component pss_top_rand_addrs_c {

メモリとコアを宣言

transparent addr_space_c<> sys_mem;

インスタンス

exec init_up {...}

cores_c cores;

rand addr test c rand addr test[10];

action entry a {

activity {

schedule {

replicate (100) {

do rand addr test c::rand addr test a;

アクションをスケジュール

```

### Solution #1: DDRページマネジメント

#### Solution #1: DDRページマネジメント

- DDRはページで構成される

- group、bank、row、column で特定 MOADOR PROJECT

- ・同一ページ内は高速アクセス

- メモリコントローラはリフレッシュのインタリーブが必要

- 異なるページへのアクセスは遅い

目的:メモリコントローラのページマネジメントをストレス検証するための read/write アドレスのシーケンスを生成する

#### 4 Gb Addressing Table

| Configuration  |                      | 1 Gb x4 |

|----------------|----------------------|---------|

| Bank Address   | # of Bank Groups     | 4       |

|                | BG Address           | BG0~BG1 |

|                | Bank Address in a BG | BA0~BA1 |

| Row Address    |                      | A0~A15  |

| Column Address |                      | A0~A9   |

| Page size      |                      | 512B    |

大切なポイント: アドレスのシーケンスを State Object を用いてモデリングすること

```

component ddr page addrs c {

state ddr page s {

rand bit [ 2] group;

rand bit [ 2] bank;

rand bit [16] row;

rand bit [10] column;

rand bit [64] addr

constraint addr[18: 9] == column;

constraint addr[34:19] == row;

constraint addr[36:35] == bank;

constraint addr[38:37] == group;

pool ddr page s ddr page p;=

bind ddr page p *;

```

State Object はビルトイン変数 prevによりシーケンス生成を制約できる

DDRのページ識別

解決されたアドレス

メモリタイプ固有の制約

pool を作成して bind する

```

action ddr same page a {

output ddr page s ddr page;

constraint c {

ddr page.group == ddr page.prev.group

ddr page.bank == ddr page.prev.bank

ddr page.row == ddr page.prev.row

ddr page.column == ddr page.prev.column

};

action ddr same bank a {

output ddr page s ddr page;

constraint c {

ddr page.group

== ddr page.prev.group

ddr page.bank

== ddr page.prev.bank

( ddr page.row

!= ddr page.prev.row ||

ddr page.column != ddr page.prev.column )

};

```

同じページのアクセスヒット 高速だがリフレッシュが必要

同一バンクの異なるページ へのアクセスヒット ページスイッチングが遅い 他のアドレス指定方法の 戦略を複数準備しておく

```

action select_strategy_a {

activity {

select {

[8]: do ddr same page a;

[1]: do ddr next col a;

[1]: do ddr same bank a;

action constrain addr a {

input ddr page s ddr page;

output addr s out;

constraint out.addr == ddr page.addr;

// component ddr page addrs c

```

次のアドレスを選択 – 80%の確率で同一ページ

状態からaddrを出力

インスタンス化と bind

アドレスを選択して read か write を実行

```

component ddr test c {

ddr page addrs c ddr page addrs;

mem ops c mem ops;

pool addr s addr p;

bind addr p *;

action ddr test a {

activity {

do

ddr_page_addrs_c::select_strategy_a;

do ddr page addrs c::constrain addr a;

select {

do mem ops c::write a;

do mem ops c::read a;

```

```

component pss_top_ddr_addrs_c

インスタンス化

ddr_next_col_a

ddr same page a

cores c cores;

ddr test c ddr test[10];

transparent addr space c<> sys mem;

ddr_page_s

ddr_page_s

exec init up {...}

使用可能な

action entry a {

constrain_addr_a

constrain_addr_a

システムメモリの宣言

activity {

schedule {

replicate (100) {

addre_s

addre s

do ddr test_c::ddr_test_a;

read a

write_a

アクションの

スケジュール

```

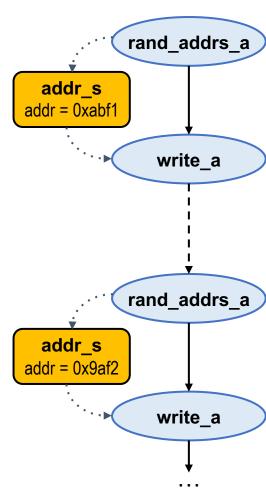

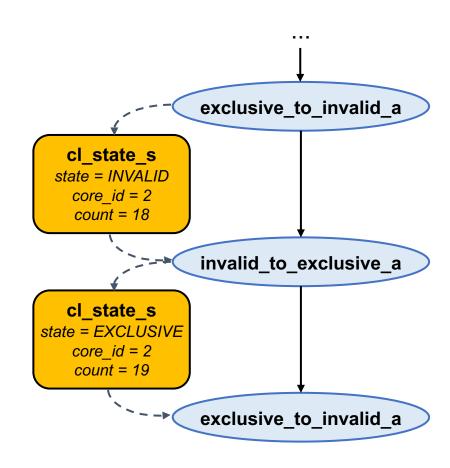

#### Solution #2: キャッシュ・コヒーレンシ状態探索

### キャッシュ・コヒーレンシ状態遷移

• SoCには複数段のキャッシュが存在

キャッシュレベルごとに異なる コヒーレンシ・プロトコルが 存在し得る

目的:適切なコア上でスケジューリング されるすべてのコヒーレンシの遷移を 探索するオペレーションのシーケンスを 生成する

# キャッシュ・コヒーレンシ状態遷移

大切なポイント:コヒーレンシのシーケンスを action 推定を用いてモデリングすること

```

component coherency c {

enum cl state e {INVALID, EXCLUSIVE, MODIFIED, OWNED, SHARED};

state cl state s {

rand cl state e cl state;

constraint initial -> cl state == INVALID;

ターゲットのキャッシュ

ステートを追跡

rand int home_core_id;

シナリオの "Home"

rand int count;

constraint initial -> count == 0;

となる core id

テスト長のカウンタ

pool cl state s cl state p;

bind cl state p *;

pool を作成して bind する

```

action reset\_counter\_a {

output cl\_state\_s out;

constraint out.count == 0;

}

カウントをリセットする action

```

abstract action transition_base_a {

input cl_state_s inp;

output cl_state_s out;

constraint out.cout == inp.count +1;

constraint out.home_core_id == inp.home_core_id;

Home" core id を管理

```

```

action invalid_to_exclusive_a : transition_base_a {

constraint transition {

inplcl_state == INVALID;

out.cl_state == EXCLUSIVE;

}

activity {

do mem_ops_c::read_a_with {

core.trait.core_id == this.inp.home_core_id;

};

}    Home" core から読出す

```

```

action exclusive_to_invalid_a : transition_base_a {

constraint transition {

inp.cl_state == EXCLUSIVE;

out.cl_state == INVALID;

}

activity {

do mem_ops_c::write_a with {

core.trait.core_id != this.inp.home_core_id; };

}

} // coherency_c 他の core から書出す

```

```

component ipss top coherency simple c {

cores c cores;

rand addrs c rand addrs;

インスタンス化と bind

mem ops c mem ops;

coherency c coherency;

pool addr s addr p;

bind addr p *;

transparent addr space c<> sys mem;

exec init up {...}

使用可能な

システムメモリを宣言

action entry a {

次のランダムな

activity {

do rand addrs c::rand addrs a;

アドレスを生成

do coherency c::exclusive to invalid a

with { out.count == 20; };

20の状態遷移の

シーケンスを推定

```

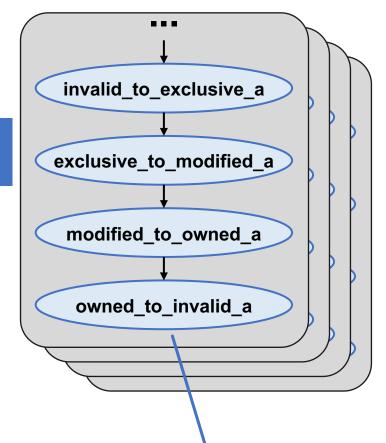

#### すべての遷移を定義

```

component coherency c {

action invalid to modified a

: transition basd a { ...}

action invalid to owned a

: transition basd a { ...}

action invalid to shared a

: transition basd a { ...}

action exclusive to modified a : transition basd a { ...}

action exclusive to shared a

: transition basd a { ...}

"count" 変数は上記

action state selector a {

rand int count;

から制約を受ける

activity {

select {

do exclusive to invalid a with {out.count == this.count;};

do modified to invalid a with {out.count == this.count;};

with {out.count == this.count;};

do owned to invalid a

with {out.count == this.count;};

do shared to invalid a

```

常に invalid で帰結させることで 続く シナリオはアドレスを再利用できる

```

component coherency test c {

rand addrs c rand addrs;

mem ops c mem ops;

インスタンス化と bind

coherency c coherency;

pool addr s addr p;

bind addr p *; :

action coherency test a {

count 変数は上記から制約を受ける

rand int count; -

activity {

ランダムアドレスを選び

シナリオ長のカウンタをリセット

do rand addrs c::rand addrs a;

do coherency c::reset counter a;

do coherency c::state selector a

with { count == this.count;};

コヒーレンシ状態遷移の

ランダムシーケンスを推定

```

```

component pss top coherency c {

インスタンス化

cores c cores;

coherency test c coherency test[10];

使用可能な

transparent addr space c<> sys mem;

exec init up { ... }

システムメモリの宣言

action _entry_a {

activity {

schedule {

replicate (100) {

do coherency test c::coherency test a

with {count == 20;};

一連の20のコヒーレンシ

状態遷移を指定する

```

ランダム遷移のそれぞれの推定では 1つのランダムアドレスを再利用する

### Solution #3: Solution #1 と #2の組合せ

- キャッシュの状態探索においてさまざまなタイミングでDDRメモリにアクセスしなくてはならない

- DDRのread/writeオペレーションはアドレスのページマネジメントのパターンに基づいて異なるタイミングになる

- 目的: DDRページマネジメントにストレスを与えながら、すべてのコヒーレンシの遷移を探索するように、適切なコア上にスケジュールされたオペレーションシの一ケンスを生成する

#### Problem #1 と #2 の組合せ

#### 大切なポイント:複数シナリオによる組立て

```

component coherency ddr test c {

ddr page addrs c ddr page addrs;

mem ops c mem ops;

coherency c coherency;

pool addr s addr p;

bind addr p *; :

action coherency ddr test a {

rand int count;

activity {

do ddr page addrs c::select stragety a;

do ddr page addrs c::constraing addr a;

do coherency c::reset counter a;

do coherency c::state selector a

with {count ==

this {count; };

```

インスタンス化と bind

count 変数は上記から制約を受ける

DDRバンクアドレスを選択

シナリオ長カウンタをリセット

コヒーレンシ遷移のランダムシーケンスを推定

#### Problem #1 と #2 の組合せ

```

component pss_top_coherency_ddr_c {

インスタンス化

cores c cores;

coherency ddr test c coherency ddr test[10];

transparent addr space c<> sys mem;

使用可能な

exec init up { ... }

システムメモリの宣言

action entry a {

activity {

schedule {

replicate(100) {

do coherency ddr test c::coherency ddr test a

with {count == this.count;};

20の一連の

コヒーレンシ状態遷移を指定

```

ランダム遷移のそれぞれの推定では DDRのアドレスシーケンスからの アイテムを再利用する

#### まとめ

- Problem #1: ステート変数を用いてDDRのページアドレスシーケンスをモデル化した

- Problem #2: アクションの推定を用いてコヒーレンシ状態遷移をモデル化した

- Problem #3: 複数モデルを組立て Problem #1 と #2 に対応した

- SystemVerilogやC/C++ではこれらのモデル化は困難かつ膨大な時間を要するだろう

- PSSでは洗練されたソリューションになる

# アジェンダ

- PSSの概要と現在の状況

- ディスプレイコントローラの適用例

- メモリ&キャッシュの適用例

- SoCレベルの適用例

- ・まとめ

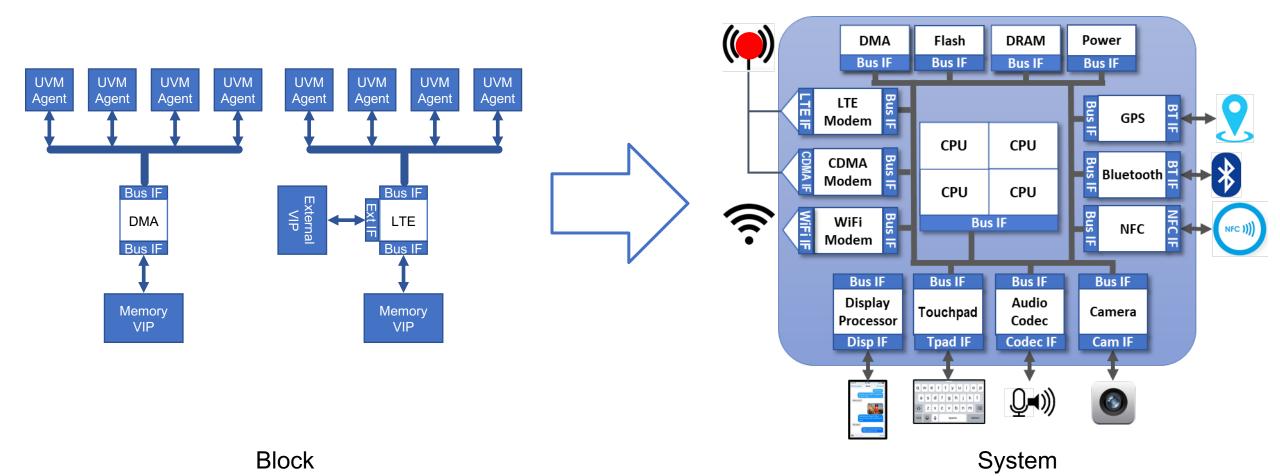

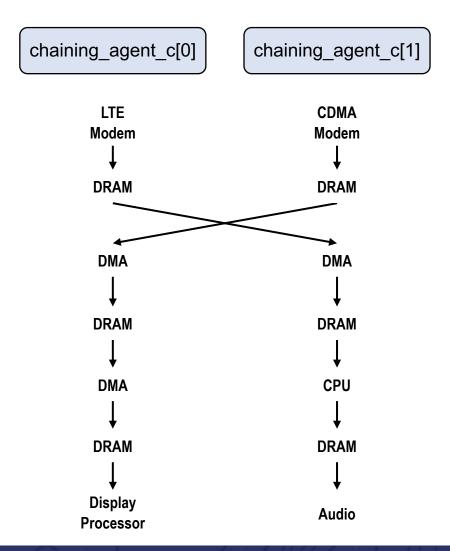

### このセクションの流れ

- SoCにおけるシナリオのチェイニング DVCon US 2020から

- ・DMAパイプライニング・シナリオのモデリング

- 一般的なIPパイプライニング・シナリオのモデリング

- SoCシナリオのチェイニング/パイプライニングのモデリング

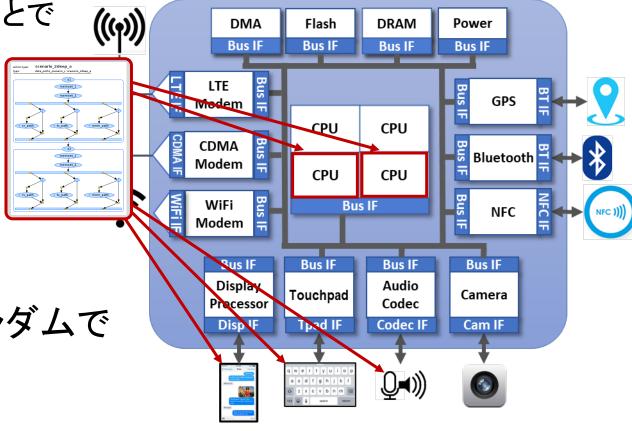

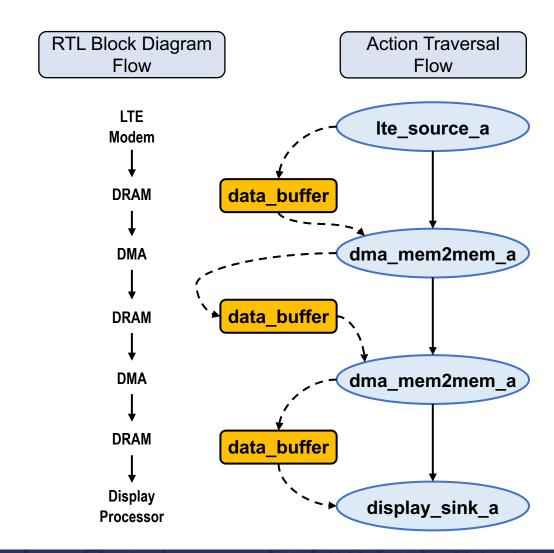

# 複数IPのシナリオインテント

Source = 供給源 Sink = 吸収源

# ブロックからシステムへの可搬性と生産性 (DVCon US 2020より)

# システムレベルの定義

```

extend component pss_top {

// RTL Agents

dma_c dma;

lte_c lte;

display_c display;

...

// Execution agents

pool [4] execution_agent_r cpu;

pool [1] lte_cip_r lte_vip;

...

}

```

```

extend component pss_top {

// Address Space

contiguous_addr_space_c<mem_trait_s> mem_addr_space;

addr_region_s<mem_trait_s> dram_region;

addr_region_s<mem_trait_s> flash_region;

exec int {

dram_region.trait.kind = DRAM;

mem_addr_space.add_region(dram_region);

mem_addr_space.add_region(flash_region);

}

```

# メモリバッファを介した複数IPからのチェイニング・スティミュラス

Flow Object Typeを 共通化して 出力バッファ宣言 チェイニング構成 ; シーケンシャル、 パラレル、グラフ データ保全のため のストレージアロ ケーション割当て の活用

チェイニングの カバレッジ

#### Flow Object Typeを共通化し出力バッファを宣言

```

package common_target {

buffer data_buffer {

rand addr_space_pkg::addr_claim_s<mem_trait_s> mem_seg;

}

abstract action mem_copy_a {

input data_buffer buf_in;

output data_buffer buf_out;

}

}

```

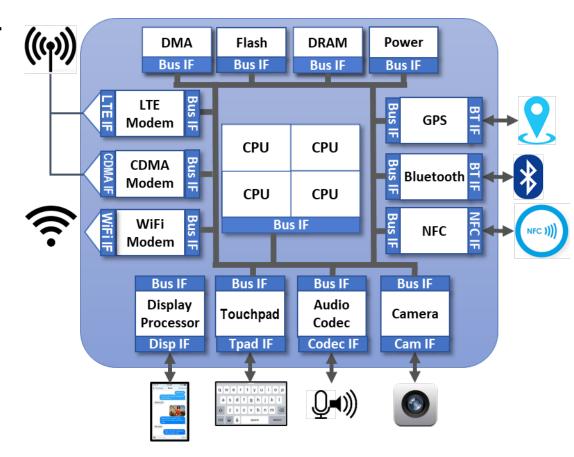

# IP オーナーのスティミュラス

LTE ソース: **GPS** Modem 外部 VIPから Memoryへの侵入 Memory2Memory: **CDMA** (a) Memoryから外部VIPへの退出 Bluetooth Modem (b) 外部VIPループバックからMemoryへの侵入 シンク: WiFi NFC Memoryから外部VIPへ Modem

<u>シンク:</u> <u>ソース:</u> Memoryから外部VIPへ 外部VIPから Memoryへ Audio Display **Touchpad** Camera Codec Processor Memory2Memory: Memory2Memory: CPU

DMA DMA転送

(a) Memory 読出し (b) Memory 書込み

Memory DRAM Flash DMA Flash DRAM Power **Bus IF Bus IF Bus IF** Bus IF LTE By Modem GPS CPU CPU Bluetooth CDMA Modem 🚞 CPU CPU WiFi Book Bus IF NFC Bus IF **Bus IF Bus IF** Bus IF Display Audio Touchpad Camera Codec Processor Codec IF Disp IF Tpad IF Cam IF

# IP オーナーのアクション

```

LTE Modem

CDMA Modem

WiFi Modem

CDMA Modem

CDMA Modem

WiFi Modem

CDMA Mo

```

```

action <device-name>_sink_a

{ input data_buffer ctb_in;

...

}

Audio    Display

Codec    Processor

```

```

DMA action core_mem2mem_a : mem_copy_a {...}

```

```

CPU action <core_mem2mem_a : mem_copy_a {...}

```

```

Memory

DRAM

Flash

DMA

Flash

DRAM

Power

Bus IF

Bus IF

Bus IF

Bus IF

LTE Bus

CPU

CPU

CDMA

Bluetooth

Modem 🚞

CPU

CPU

WiFi Modem

Bus IF

NFC

Bus IF

Bus IF

Bus IF

Bus IF

Display

Audio

Touchpad

Camera

Processor

Codec

Codec IF

Disp IF

Tpad IF

Cam IF

```

# シーケンシャルなチェイニング

```

action sequential chaining a {

activity {

// Source

select {

[10] : do lte source a;

[20] : do cdma source a;

[10] : do camera_source_a;

// Memory2Memory

replicate (2) {

select {

do core_mem2mem_a;

do dma mem2mem a;

do bluetooth mem2mem a;

// Sink

do display sink a;

```

# パラレルのチェイニング

```

extend component pss_top {

action entry {

schedule {

replicate (5) {

do sequential_chaining_a;

}

}

}

```

# チェイニングの組合せのカバレッジ

```

action sequential chaining a {

rand source e source id;

rand mem2mem e mem2mem id0, mem2mem id1;

rand sink e sink id;

rand int size;

activity {

// Source

select {

[10] : do let source a with {

size == this.size;

this.source id == LET SOURCE; }

[20] : do cdma source a with {

size == this.size;

this.source id == CDMA SOURCE; }

[10] : do camera source a with {

size == this.size;

this.source id == CAMERA SOURCE; }

// Memory2Memory

// Sink

```

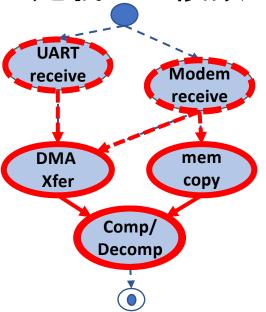

### ストリーミングシナリオのインターリーブ 制御と網羅

#### <u>単純なストリームのインターリーブ例</u>

DMA Pipeline (2ステップ)

- 1. move (Mx xはステップが属する転送番号)

- 2. wait (Wx サイズなどの属性をもとに時間を消費)

このようなシナリオをモジュール化し、 ポータブルなフレームワークによって 制御、網羅することが、多くの検証や バリデーションで求められている

| シナリオ0 | シナリオ1 | シナリオ2 | シナリオ3 |

|-------|-------|-------|-------|

| MO    | MO    | MO    | MO    |

| M1    | W0    | M1    | M1    |

| M2    | M1    | M2    | W1    |

| W0    | W1    | W2    | M2    |

| W1    | M2    | W1    | W0    |

| W2    | W2    | W0    | W2    |

コントローラ(例:組込 コア、AXIバス)が1つ の場合、N個のDMAスト リーム転送を管理する必 要がある。

例えば左の図では3つの DMA転送に対する4つの 可能なシナリオを示して いる。 シナリオ0:最も多くのDMAチャネルを 使用し、コーナーケースのバグを発見す ることができる

シナリオ3: DMAチャンネルが2つしかない場合に使用可能

シナリオ2: DMAの特定のトランザクションタイプにおいて、最良のパフォーマンス結果を得られる可能性がある

#### DMAストリームのインターリーブシナリオ - SV

```

while (j < NOF SCENARIOS) begin

// Randomly pick a new step at a time, accounting for transfer steps that

// have already been picked. There is no obvious set of constraints that

// can quarantee: (1) Exactly 2 steps will be picked for each transfer

(2) first step will appear before second step for all transfers.

while (i < NOF TRANSFERS*2) begin

if (available(move) and available(wait))

step = $random % 2; // 2 available steps

else if(available(move))

step = 0;

else

step = 1;

scenario step[i].type=step

scenario step[i].transfer id=get available transfer id(step);

i++;

end

if (!exists(scenario step) begin add scenario(scenario step);

j++;

end

end

```

アルゴリズムは、様々なシナリオを提供する上で効率的ではない

シナリオを制御するためには、疑似コードで 使用している関数を変更する必要がある

ステップ数が増えたら、別の異なる実装が 必要になる

同じリソースの一部を使用する他のスティミュラスと混在させることができない

組込みコア用のC言語実装コードに移植ができないため、書き直す必要がある。

PSSではシナリオの制御、調整、混在化、網羅、移植を宣言的に表現できる

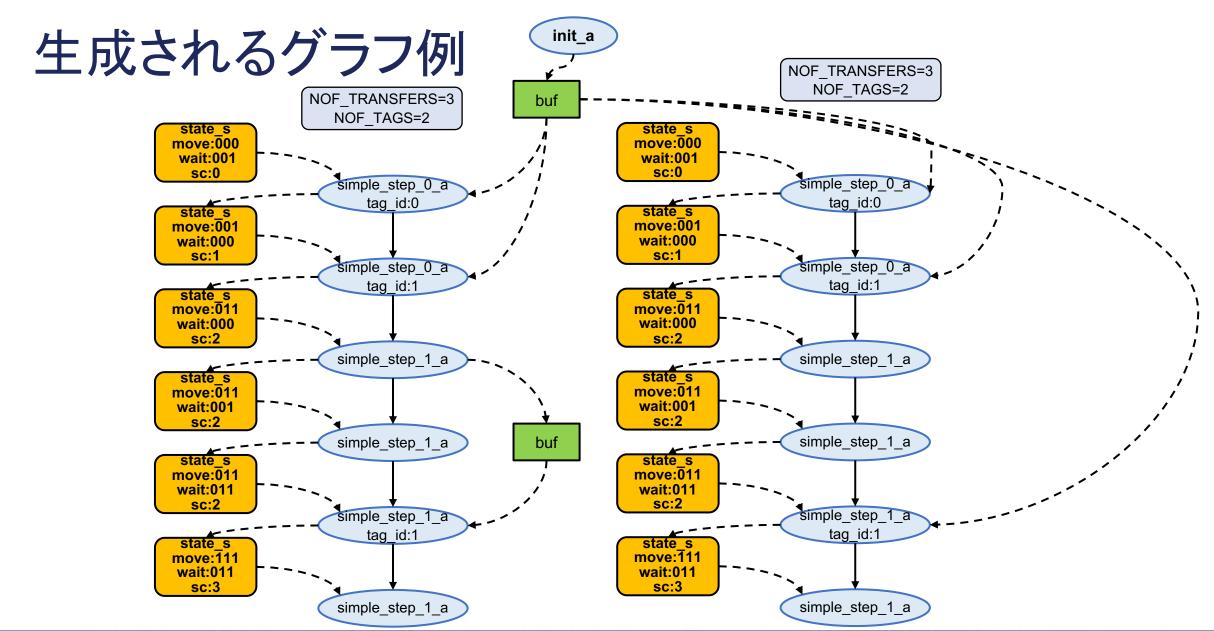

#### DMAストリームのインターリーブをモデリング

```

package dma_pkg {

const int NOF_TRANSFERS = 4;

state state_s {

rand bit move [NOF_TRANSFERS] ;

rand bit wait [NOF_TRANSFERS] ;

constraint initial -> {

foreach (move[i]) {

move[i] == 0;

wait[i] == 0;

}

}

}

```

state オブジェクトの フィールドを初期化

```

action move a {

MOVEの転送が

input state s in s;

終わった事の印

output state s out s;

rand int transfer num;

constraint out s.move[transfer num] == 1'b1;

constraint {

foreach(out s.move[i]) {

out s.wait[i] == in s.wait[i];

他のstateの値が

if (i != transfer num) {

変化しない

out s.move[i] == in s.move[i];

という制約を設定

action wait a {

input state s in s;

WAITの転送が

output state s out s;

終わった事の印

rand int transfer num;

constraint out s.wait[transfer num] == 1'b1

constraint {

foreach(out s.wait[i]) {

out_s.move[i] == in_s.move[i];

if (i != transfer num) {

他のstateの値が

out s.wait[i] == in s.wait[i];

変化しない

という制約を設定

```

#### インターリーブ時のDMAステップのスケジュール

```

component dma c {

import ip0 pkg::*;

pool state s state p;

bind state p *;

action dma transfer a {

rand int transfer num;

move a M;

wait a W;

activity {

M with {transfer num == this.transfer num; }

scheduleオペレータが

W with {transfer num == this.transfer num; };

複数回の転送の間に

MとWをインターリーブ

action all dma transfers a {

dma transfer a DT[NOF TRANSFERS];

activity {

schedule {

replicate (i:NOF TRANSFERS) {

DT[i] with {transfer num == i;} ;

```

```

NOF TRANSFERS=2

state s

move:00

wait:00

move a

state s

move:01

wait:00

move a

state s

move:11

wait:00

wait a

state s

move:11

wait:01

wait a

state s

move:11

wait:11

```

# 制約の上書きも簡単

```

extend action wait_a {

constraint countones(in_s.move) == NOF_TRANSFERS;

}

```

すべての転送 (move) が終わってから待機 (wait) する

```

action move a {

input state s in s;

output state s out s;

rand int transfer num;

constraint out s.move[transfer num] == 1'b1;

constraint {

foreach(out s.move[i]) {

out s.wait[i] == in s.wait[i];

if (i != transfer num) {

out s.move[i] == in s.move[i];

action wait a {

input state s in s;

output state s out s;

rand int transfer num;

constraint out s.wait[transfer num] == 1'b1;

constraint {

foreach(out s.wait[i]) {

out s.move[i] == in s.move[i];

if (i != transfer num) {

out s.wait[i] == in s.wait[i];

```

#### インターリーブするストリームのリソースパイプライン

タスクを複数のサブタ スクにパイプライン化 し、スティミュラスト のやり取りを要するIP 用のスティミュラスを どのようにモデルリン グするか

異なるサブタスクのインターリーブを可能にするIP用のマルチステップ・スティミュラスのモデリング

リソースがパイプラインの異なるステージで 解放された際に異なる ストリームで共有されるようにモデリング

異なる複数のタスクが 存在する際の意味深い インターリーブシナリ オのカバレッジ

#### 具体例:

- 複数のチャネルリソースを持ち、MOVEと転送完了を待つWAITをサブタスクとして持っている DMA IPの例。DMA転送ではMOVE、WAITともに同じチャネルを使用する必要がある。

- PIPE、OVERLAY、INTERFACEのリソースを持っているDISPLAY IPの例。それぞれのリソースを処理するサブタスクが存在する。

## パイプライン化スティミュラス – PSSモデリング

State Flowオブジェクトと共にScheduleオペレータを使うことで、パイプライン化シナリオの生成とキャラクタライズが可能なモデルとなる

actionの命名則: stream\_step\_<i>\_a

ここで <i>は0からストリームで必要なサブタスク数-1を取る

(例:DMAでは2つ、 DISPLAYでは3つ) 各サブタスクに必要 となる resource オブ ジェクトの使い方 covergroup をモデリングしサンプリング することで、生成されたテストのインターリーブをキャラクタライズする

入力の state オブジェクトに追加の制約を 加えてパイプライニ ングを制御する

# 3-Step Display パイプラインのモデリング

```

package display pkg {

resource display engine step0 r {}

resource display engine step1 r {}

resource display engine step2 r {}

state state s {

rand bit step0 [NOF TRANSFERS] ;

rand bit step1 [NOF TRANSFERS] ;

rand bit step2 [NOF TRANSFERS] ;

rand bit [NOF TRANSFERS] step0 b;

rand bit [NOF TRANSFERS] step1 b;

rand bit [NOF TRANSFERS] step1 b;

constraint {foreach([step0[i]) {

step0 b[i] == step0[i];

step1 b[i] == step1[i];

step2 b[i] == step2[i];

constraint initial -> {

foreach (step0[i]) {

step0[i] == 0;

step1[i] == 0;

step2[i] == 0;

```

```

component display c {

action stream step0 a {

input state s in s;

output state s out s;

rand int transfer num;

lock display engine step0_r engine_1;

constraint out s.step0[transfer num] == 1'b1;

constraint {

foreach(out s.step0[i]) {

out s.step1[i] == in s.step1[i];

out s.step2[i] == in s.step2[i];

if (i != transfer num) {

out s.step0[i] == in s.step0[i];

covergroup {

step0: coverpoint in s.step0 b;

step1: coverpoint in s.step1 b;

step2: coverpoint in s.step2 b;

all: cross step0, step1, step2 {

ignore bins interleaving = all with (

((step0 | step1) == step0) &&

((step1 | step2) == step1)

);

} cg;

```

Stepに応じてリソースをロック 1つ目のリソースはPIPE、 2つ目はOVERLAY、 3つ目はINTERFACE

Stepごとのカバレッジを サンプリングし そのクロスで特徴づけられる 全インターリーブを 実現することがゴール

詳細は次スライド・・・

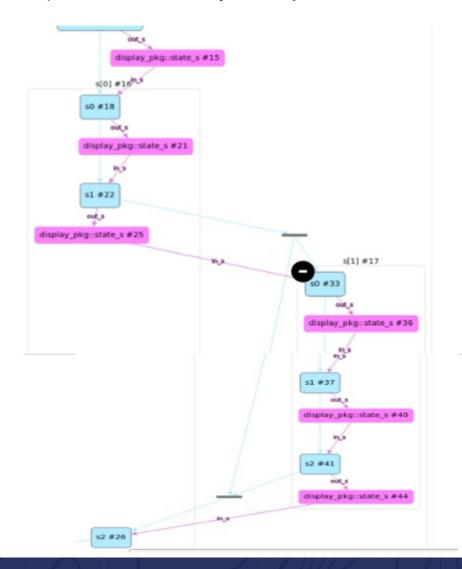

#### インタリーブされるステップのスケジューリング

```

component display_c {

import display pkg::*;

pool state s state p;

bind sample state p *;

action stream a {

rand int transfer num;

stream step0 a s0;

stream step1 a s1;

stream step2_a s2;

activity {

s0 with {transfer num == this.transfer num;}

s1 with {transfer num == this.transfer num;}

s2 with {transfer num == this.transfer num;}

action all stream a {

stream a s[NOF TRANSFERS];

activity {

schedule {

replicate (i:NOF TRANSFERS) {

s[i] with {transfer num == i;};

```

#### パイプラインでインターリーブするストリームのモデリング (リソースがステップから解放される際に共有される)

```

extend component soc c {

import display pkg::*;

pool [6] display engine step0 r display engine step0 p;

bind display engine step0 p *;

pool [4] display_engine_step1_r display_engine_step1_p;

bind display engine step1 p *;

pool [5] display engine step2 r display engine step2 p;

bind display engine step2 p *;

action all ip all tasks a {

activity {

schedule {

replicate (i:DISPLAY STREAMS) {

do display c::all stream a

with {comp == pss top.soc.display[i];};

```

DISPLAYリソースはプールされ 複数のコントローラで共有可能

あるコントローラが リソースを解放すると 別のコントローラが リソースを取得できるため リソースを持っていた ストリームの終了を 待つ必要がない

# DISPLAY例からリソース制約を汎用ストリームのインターリーブ・パイプライン・パターンに適用

```

package display pkg {

enum pipe kind e {VID, GFX};

extend resource display engine step0 r {

rand pipe kind e kind;

constraint {

kind == VID -> instance id in [0..2];

kind == GFX -> instance id in [3..5];

enum overlay kind e {LCD0, LCD1, LCD2, TV};

extend resource display engine step1 r {

rand overlay kind e kind;

constraint instance id == int(kind);

enum interface kind e {DSI A, DSI B, DP A, DP B, HDMI};

extend resource display engine step2 r {

rand interface kind e kind;

constraint instance id == int(kind);

```

```

extend action display_c::stream_a {

constraint pipe2overlay_c {

s0.engine_l.kind == GFX -> s1.engine_l.kind != LCD0;

s0.engine_l.kind == VID -> s1.engine_l.kind != LCD1;

}

constraint overlay2interface_c {

s1.engine_l.kind == LCD0 -> s2.engine_l.kind == DP_A;

s1.engine_l.kind == LCD1 -> s2.engine_l.kind in [DSI_A, DSI_B];

s1.engine_l.kind == LCD2 -> s2.engine_l.kind in [DSI_A, DSI_B, DP_B];

s1.engine_l.kind == TV -> s2.engine_l.kind in [DP_A, HDMI];

}

}

```

# インターリーブ・シナリオのカバレッジ

```

covergroup {

step0: coverpoint in_s.step0_b;

step1: coverpoint in_s.step1_b;

all: cross step0, step1 {

ignore_bins interleaving = all with (((step0 | step1) != step0));

}

} cg;

```

|       | move | wait |

|-------|------|------|

| Pt #1 | 1111 | 0000 |

| Pt #2 | 1111 | 0011 |

| Pt #3 | 0011 | 0001 |

転送前に始まった待機は無視する

#### 複数IPのパイプラインタスクを組合わせたSOCシナリオ

```

extend component soc c {

import dma pkg::*;

pool [8] dma engine step0 r dma engine step0 p;

bind dma engine step0 p *;

pool [8] dma engine step1 r dma engine step1 p;

bind dma engine step1 p *;

import display pkg::*;

pool [6] display engine step0 r display engine step0 p;

bind display engine step0 p *;

pool [5] display engine step1 r display_engine_step1_p;

bind display engine step1 p *;

pool [4] display engine step2 r display engine step2 p;

bind display engine step2 p *;

action all ip all tasks a {

activity {

parallel {

schedule {

replicate (i:DISPLAY STREAMS) {

do display c::all stream a with {comp == pss top.soc.display[i];};

schedule (

replicate (i:DMA STREAMS) {

do dma c::all stream a with {comp == pss top.soc.dma [i];};

```

異なるIPからなる インターリーブシナリオは 互いに独立して 実行される

# すべてのパイプラインをチェイニング

```

action simple_a {

input buf in_buf;

output buf out_buf;

rand int transfer_num;

simple_step_0_a s0;

simple_step_1_a s1;

simple_step_2_a s2;

activity {

s0 with {transfer_num == this.transfer_num; };

s1 with {transfer_num == this.transfer_num; };

s2 with {transfer_num == this.transfer_num; };

}

}

```

パイプラインのストリームは 入力バッファからのデータを処理して その結果を出力バッファに出力し その後に異なるIPに消費される

これでチェイニングパターンと インターリーブパターンを 組合わせることができる

#### シナリオのチェイニング/インターリーブ まとめ

- チェイニング例を用いてIPのモデルを純粋にSOCに適用する手法を 紹介した

- ストリームのインターリーブ/パイプライニングのシナリオに対して schedule と state flow オブジェクトを併用することで微調整する手 法を紹介した

- ・ストリームのインターリーブ/パイプライニング例に対してPSSの宣言型構文の使用方法を示し、SystemVerilogでは困難または不可能であることを示した

- ストリームのチェイニングおよびインターリーブ/パイプライニングの 組合せなど、異なるタイプのSoCシナリオを容易に生成できることを 示した

# アジェンダ

- PSSの概要と現在の状況

- ディスプレイコントローラの適用例

- メモリ&キャッシュの適用例

- SoCレベルの適用例

- ・まとめ

## PSSのまとめ

- ・IPテスト空間のフォーマルな指定

- IPライフサイクルの早期からテスト空間のドキュメンテーションとして

- ・システム・シナリオのフォーマルなドキュメンテーション

- SoCアーキテクチャを定義する際に作成可能

- ・複数のIPのテストシナリオを簡単に構成

- テストにおける state、resource、schedule の依存関係を自動ハンドリング

- 部分的なテストシナリオ

- SoCの完全に深く理解しなくてもテスト生成が可能

- テスト生成時およびテスト実行時のカバレッジレポート

- ・パワーステートの遷移、機能モードなどのカバレッジ

- ・テストそのものがポータブル

- IP (UVM/SystemC) からSoCの組込みプロセッサ、ポストシリコンまで

# まとめ

PSSは宣言型のフォーマルかつポータブルなテスト指定ができ プラットフォーム固有のテストを自動的に生成することができる

PSS 2.0は今日現在、正式プロダクションリリースの状態

PSS 2.1およびその先に向けた優れたアイデアがある

PSSの未来を一緒にかたちにしていきましょう

# JAPAN

がとうございました Any Questions?