#### Accelerating Complex System Simulation using Parallel SystemC and FPGAs

Stanislaw Kaushanski, MINRES Technologies GmbH, Duisburg, Germany (<u>stas@minres.com</u>) Johannes Wirth, ESA Group, TU Darmstadt, Darmstadt, Germany (<u>wirth@esa.tu-darmstadt.de</u>) Eyck Jentzsch, MINRES Technologies GmbH, Munich, Germany (<u>eyck@minres.com</u>) Andreas Koch, ESA Group, TU Darmstadt, Darmstadt, Germany (<u>koch@esa.tu-darmstadt.de</u>)

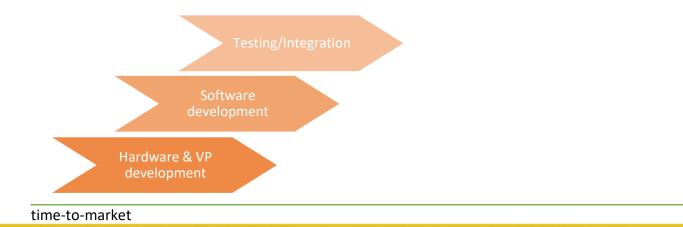

# Classical SoC Development

- Sequential workflow

- Late firmware integration

- Late issue discovery

- Protracted timelines

# The Shift-Left Concept

#### • Virtual Prototypes (VPs)

- Very early availability

- Powerful debugging tools

- No resource limitations

#### • Physical Prototypes (FPGAs)

- Real hardware interaction

- Very fast simulation

- Accurate timing

### Limitations

- Virtual Prototype:

- Single-threaded SystemC bottlenecks complex systems

- Model accuracy with respect to Hardware

- Simulation Trade-off: Speed vs. Accuracy

- Physical Prototype:

- FPGA simulation requires complete synthesizable RTL

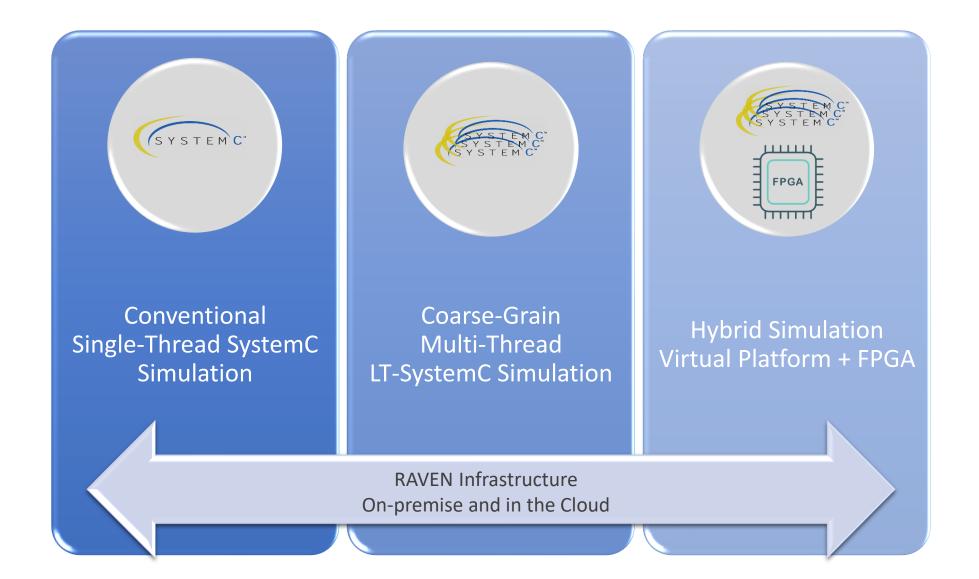

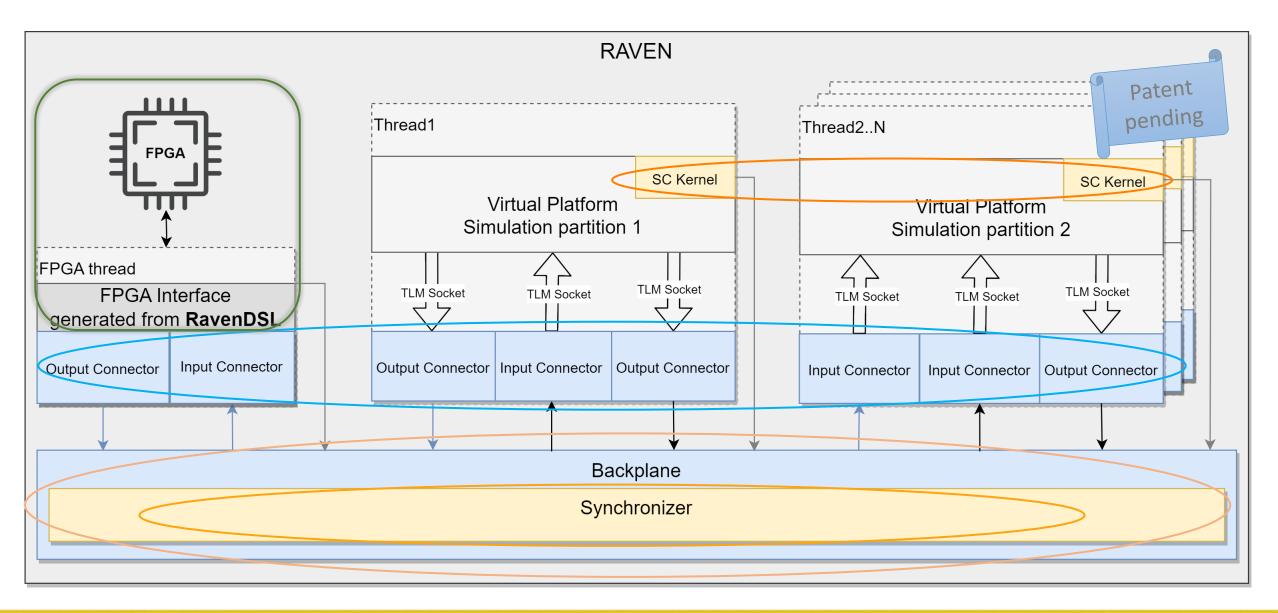

# RAVEN as a solution

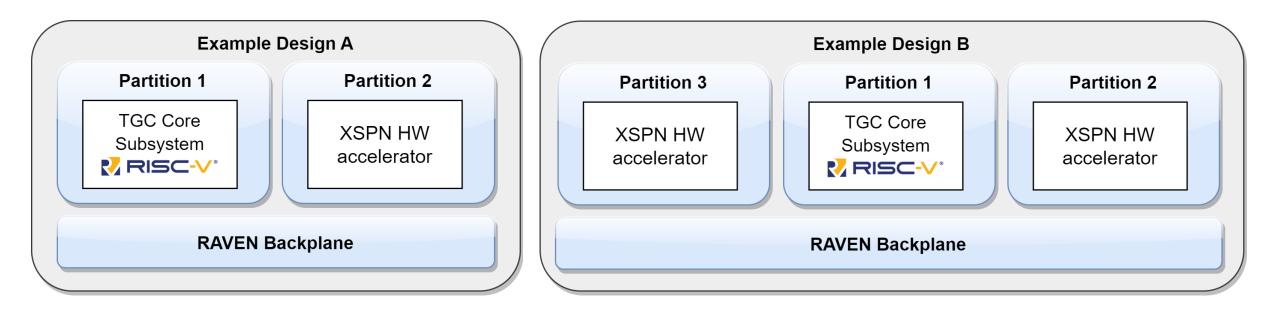

# DUT integration process

- Step 1: Analyze Design to determine partition boundaries.

- Minimal interactions between partitions to prevent bottlenecks.

- Consider computational load within partitions for meaningful parallelization.

- Step 2: Partition the Design

- Divide the design into partitions.

- Connect open connections to RAVEN interthread connectors.

- Step 3: FPGA Integration

- Generate wrapper for data exchange and synchronization.

# Automation with RavenDSL

- Automating the Integration

- RavenDSL to automate the integration process.

- Reducing manual effort and minimizing errors.

- RavenDSL

- Describes RTL interfaces and signal transitions.

- RavenDSL Compiler

- Tool-flow automatically creates hardware and software components.

- TaPaSCo Framework for FPGA bitstream generation.

- Optionally adjust FPGA synthesis.

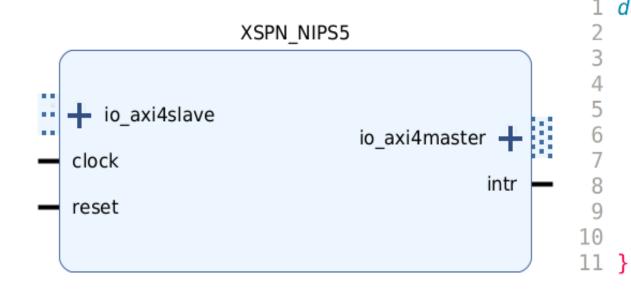

#### RavenDSL example

# Scalability

- Challenge:

- High upfront costs for FPGA resource availability.

- Waiting times for FPGA slots.

- RAVEN's Solution:

- Cloud-Ready Infrastructure.

- No upfront investments in FPGAs.

- No Waiting Times.

- GUI for user-friendly cloud usage.

- Flexibility: scale resources as needed.

| ID                                                                                                                                                       | Name                                                                                                                                                                                                                               | Туре                                             | Status  | Ip Adress      | Access Key       | Update list      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------|----------------|------------------|------------------|

| ✓ i-00c2f732f0e51006f                                                                                                                                    | KWS_Demo                                                                                                                                                                                                                           | f1.2xlarge                                       | running | 52.16.119.75   |                  | opulate list     |

| i-024b5cab618a76                                                                                                                                         | kws_bitstream                                                                                                                                                                                                                      | z1d.2xlarge                                      | running | 54.74.167.25   | CLOS ILLOPPIA LD |                  |

| i-06bafb2fe429b7a42 Raven_0.7.1_XSPN                                                                                                                     |                                                                                                                                                                                                                                    | f1.2xlarge                                       | stopped | None           | stas_minres_ts   | Start Selected   |

| i-08828fb12e83144 Demonstrator                                                                                                                           |                                                                                                                                                                                                                                    | f1.2xlarge                                       | stopped | None           | stas_minres_ts   |                  |

| i-0e3831ddda5d5f7 FpgaDevVivado19                                                                                                                        |                                                                                                                                                                                                                                    | r5.xlarge                                        | stopped | None           | stas_minres_ts   |                  |

| i-0fab91bc3948a94                                                                                                                                        | i-0fab91bc3948a94 Raven_0.7.1_setup                                                                                                                                                                                                |                                                  | stopped | None           | stas_minres_ts   | Stop Selected    |

| i-09d1bd696d61bb                                                                                                                                         | r5.xlarge                                                                                                                                                                                                                          | stopped                                          | None    | stas_minres_ts |                  |                  |

| i-0adac151264552 gabriel_docker                                                                                                                          |                                                                                                                                                                                                                                    | r5.xlarge                                        | stopped | None           | abriel_docker    |                  |

| i-066cbd011cc4ef7ab env4tgc_ci                                                                                                                           |                                                                                                                                                                                                                                    | r5.xlarge                                        | stopped | None           | stas_minnes_ts   | Remove Selected  |

| i-07a53260479df5c                                                                                                                                        | t2.micro                                                                                                                                                                                                                           | stopped                                          | None    | eabriel_docker |                  |                  |

| i-0fd26d2a37cbff0bf                                                                                                                                      | offsiteMuc                                                                                                                                                                                                                         | t3.xlarge                                        | stopped | None           | stas_minres_ts   |                  |

| i-0f5072cba82fe61a3                                                                                                                                      | BitstreamGen170123                                                                                                                                                                                                                 | z1d.2xlarge                                      | stopped | None           |                  | Create EC2 Setup |

| 9:08:01.520 ::INFO:: i<br>9:08:01.520 ::INFO:: f<br>9:08:01.520 ::INFO:: s<br>9:08:01.520 ::INFO:: s<br>9:08:01.520 ::INFO:: a<br>9:08:01.520 ::INFO:: i | nstance_name = Kws_Demo<br>nstance_id = i-00c2/732/0e51<br>pga_dev_ami = ami-07c55ad<br>ecurity_group = sg-03ec2aac.<br>rc = /scratch/stas/repos/Multi<br>gfi = agfi-04c062c86a0213bd<br>p = None<br>di instance i-00c2f732f0e5100 | 4d829b266e<br>4d9a612ed<br>PartFpga/Validat<br>1 | tion-VP |                |                  |                  |

|                                                                                                                                                          | ng for instance i-00c2f732f0e510c                                                                                                                                                                                                  |                                                  |         |                |                  |                  |

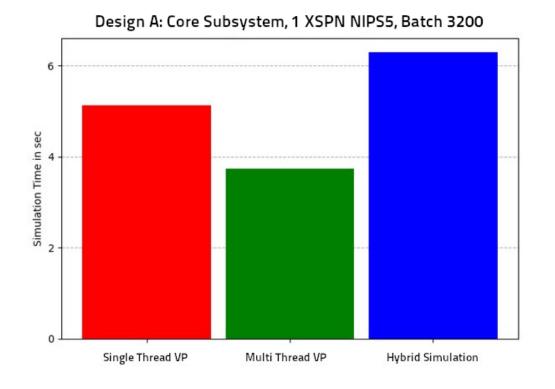

# **RAVEN Simulation Performance**

|          | NIPS5 |       |                   | NIPS80 |                 |                 | Available |

|----------|-------|-------|-------------------|--------|-----------------|-----------------|-----------|

|          | DUT   | RAVEN | Total             | DUT    | RAVEN           | Total           |           |

| LUT      | 17k   | 25k   | 167k (12.8%)      | 99k    | 25k             | 250k (19.2%)    | 1304k     |

| Register | 7.7k  | 24k   | $214k \ (8.19\%)$ | 159k   | 24k             | 361k (13.9%)    | 2607k     |

| CLB      | 3.3k  | 6.0k  | 36k (21.8%)       | 20k    | $4.3\mathrm{k}$ | 52k (31.8%)     | 163k      |

| BRAM     | 11    | 103   | 222 (11.0%)       | 71     | 103             | 282 (14.0%)     | 2016      |

| DSP      | 23    | 0     | 26~(0.25%)        | 736    | 0               | $739\ (8.16\%)$ | 9024      |

#### RAVEN performance analysis

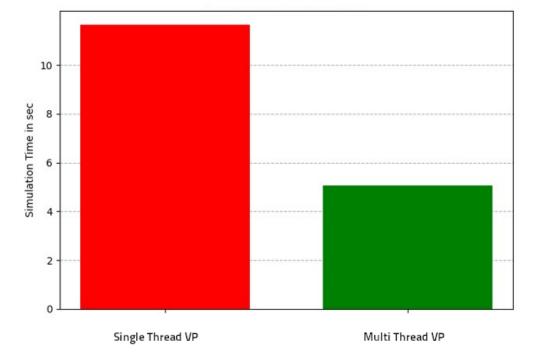

Design B: Core Subsystem, 2 XSPNs NIPS5, Batch 3200

#### RAVEN performance analysis

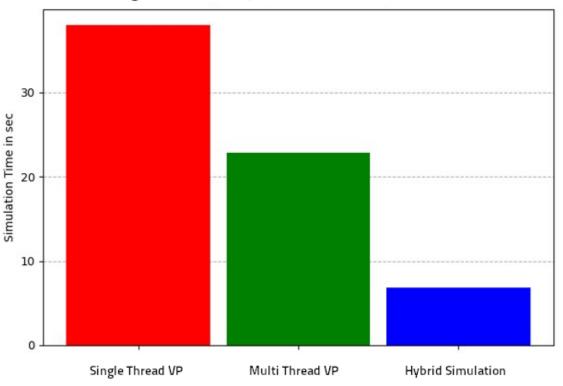

Design A: Core Subsystem, 1 XSPN NIPS80, Batch 3200

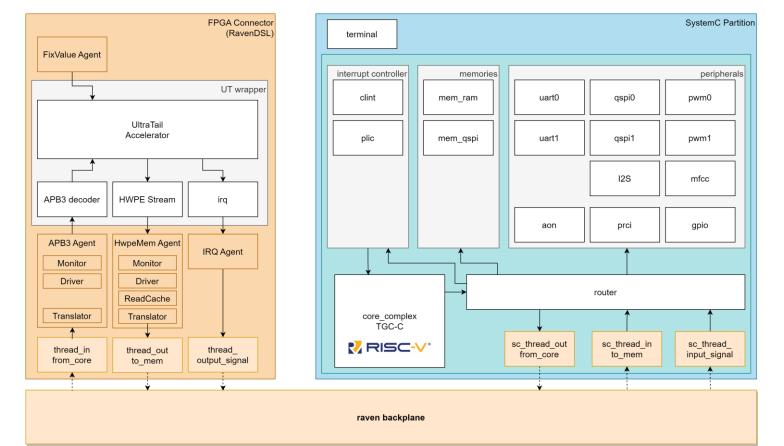

# Showcase Setup: Keyword Spotting System

- Audio Data Preprocessing: Performed in Virtual Prototype

- HW ML Accelerator on FPGA

- Live Demonstration at Our Booth

### Conclusion

- Easy parallel and hybrid simulation

- Simple partitioning

- Automated RTL wrapper generation

- Low entry barrier for hybrid simulation

- Highly flexible and scalable through unified use of on-premise and Cloud resources

- Significant Speed Gains for large Virtual Prototypes as well as Complex HW Blocks

#### Questions