A scalable VIP component to increase robustness of co-verification within an ASIC

Mario de Matteis – Matteo Barbati

### Agenda

- Co-verification adoption

- State-of-the-art Vs novel approach

- Description on the novel approach

- Overview on FW\_VIP solution

- Case study analysis

- Conclusion and next step

# Co-verification adoption to meet complexity

- Increasing complexity of the ASIC product (e.g. power regulator) is pushing platform to include SOC-like architectures.

- Standalone verification of the firmware with FPGA emulators doesn't meet the signoff requirements of the complete DUT application:

- A full-chip **co-verification approach** is required to qualify the device.

- A testbench where **the entire DUT (digital, analog logic plus the firmware)** is instantiated should be adopted.

- A fully featured **UVM environment** should be adopted.

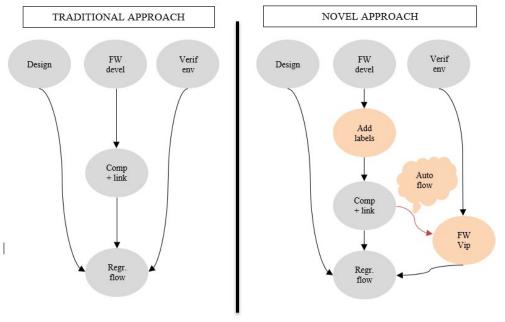

## State-of-the-art Vs novel approach

- FPGA Centric approach: firmware engineers verify their own code. A.k.a. "Traditional Approach".

- UVM-centric (VAL approach): "fake" register map to map verification component functionalities into firmware world and to develop test in firmware with randomization and UVM checkers in place.

- **Novel approach:** using FW\_VIP component which reduces the impact of co-verification to the verification and firmware workflow.

# Workflow changes

Figure 1 - Workflow changes

- Inserting labels within firmware to identify significant functions linked to product capabilities.

- Identifying significant variables that are linked to product capability.

- Automation of generation inputs for FW\_VIP to manage changes of the firmware code.

# FW\_VIP: monitored events

Once the flow is in place the FW\_VIP automatically translates the firmware events into UVM transactions which will be passed to the scoreboards and checkers.

The pictures is showing the some types of events the FW\_VIP is able to monitor.

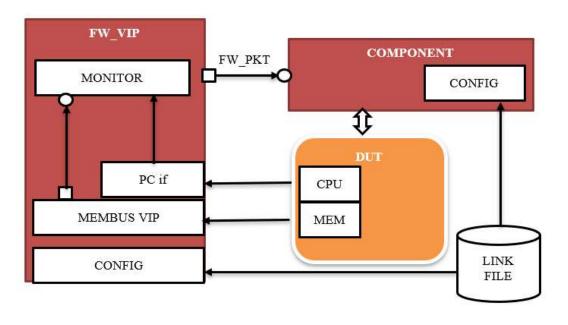

# FW\_VIP: block description

The verification IP topology is composed by:

- **MEMBUS VIP**: to monitor memory transactions (e.g. ahb).

- **PC IF**: to monitor addressing on Program counter.

- **MONITOR**: to translate events into transaction

- **CONFIG**: for automatic configuration to adapt to the firmware releases.

FW VIP: the packet

typedef enum {pc,dut\_state,variable} event\_type; class fw\_packet extends uvm\_sequence\_item; event\_type currentEvent; string pc\_event;

| string     | variableName;  |  |

|------------|----------------|--|

| bit [31:0] | variableValue; |  |

`uvm\_object\_utils\_begin(fw\_packet)

`uvm\_field\_enum(event\_type, currentEvent, UVM\_ALL\_ON)

`uvm\_field\_string(pc\_event, UVM\_ALL\_ON)

Element for another store

`uvm\_field\_string(variableName, UVM\_ALL\_ON)

`uvm\_field\_int(variableValue, UVM\_ALL\_ON)

`uvm\_object\_utils\_end

function new(string name = "fw\_packet");

super.new(name);

endfunction

endclass : fw\_packet

# The **fw\_packet** of the FW\_VIP is suited to communicate to other components:

- Hardware and firmware synchronization events (e.g. interrupt calls) for which "pc\_event" variable carries on the information.

- Variable updates within the firmware for which "variableName" and "variableValue" carries on the information.

## Configuration from case study

vout\_max\_ra 2000054E vout\_min\_ra 20000550 vout\_transition\_rate\_ra 20000556 vout\_max\_rb 200005A2 vout\_min\_rb 200005A4 vout\_transition\_rate\_rb 200005AA

Figure 6 - ramAddressList configuration file

load\_configuration\_end DEFAULT 00003f78 load\_configuration HIDDEN 00003f09 load\_user\_configuration\_from\_OTP\_end DEFAULT 00002ef6 load\_user\_configuration\_from\_OTP HIDDEN 00002ec5 Figure 7 - pcValueList configuration file At the beginning of the simulation the components which are listening transactions and events related to the firmware load the values from two files.

The contents of these files are "solution dependent" and has to be defined by verification and firmware engineers together.

## Monitoring variables

function void write(ahb3\_master\_packet p);

### \$cast(abb pkt, p.clone);

`uvm info("fw monitor", \$gformatf("AHB packet triggered \n %s",p.sprint()),UVM\_FULL)

if (ahb pkt.hwrite == AHB3\_WRITE) begin

`uvm\_info("fw\_monitor", \$sformatf("AHB write packet triggered \n %s<u>",p.sprint()</u>),UVM FULL) if (ramAddressList.exists(ahb pkt.haddr)) begin ram pkt.pc event = "NULL": ram pkt.variableName = ramAddressList[ahb\_pkt.haddr]; if ( (ram pkt.variableName == "vrStateA") || (ram pkt.variableName == "vrStateB") ) begin \$cast(ram\_pkt.dutStateValue,ahb\_pkt.hwdata[7:0]); ram pkt.currentEvent = dut state; end else begin ram\_pkt.variableValue = ahb\_pkt.hwdata; ram pkt.currentEvent = variable; end `uvm info("fw monitor", \$sformatf("AHB address %8X is in the list \n %s",ahb pkt.haddr,ram pkt.sprint()),UVM FULL) uvm\_info("fw\_monitor", \$sformatf("RAM\_event\n %s", ram pkt.variableName), UVM NONE) send pkt.write(ram pkt); end

The monitor of the FW\_VIP operates as bridge for memory transactions between MEMBUS VIP and other parts of the verification environment.

The **ramAddressList** is the array filled up during configuration phase and contains the trigger points used to monitor the firmware variables. After the analysis of the MEMBUS VIP transaction the **fw\_packet** is sent.

end

endfunction: write

### Monitoring Program Counter

virtual task run phase (uvm phase phase); forever begin @(posedge vif.clk); `uvm info("fw monitor", \$sformatf("program counter triggered: %4X", vif.program counter),UVM FULL) if (pcValueList.exists(vif.program counter)) begin pc pkt.pc event = pcValueList[vif.program counter]; pc pkt.variableName = "NULL"; pc pkt.currentEvent = pc; `uvm info("fw monitor", \$sformatf("PC %8X is in the list \n %s", vif.program counter, pc pkt.sprint()), UVM FULL) `uvm info("fw monitor", \$sformatf("PC event\n %s",pc pkt.pc event),UVM\_NONE) send pkt.write(pc pkt); end end endtask: run phase

The monitor of the FW\_VIP operates as bridge for memory transactions between program counter interface and other parts of the verification environment.

The **pcValueList** is the array filled up from configuration phase and contains the trigger points used to monitor events related to program counter.

After the analysis of the program counter event the **fw\_packet** is sent.

### Automation process

Automation to deal with different firmware releases is achieved through configuration files which are generated by scripts.

The firmware and verification engineers works together to agree on the content of this files. Eventually label has to be inserted within the firmware.

# Case Study1: intercept pc to trigger self-check

function void write pc pkt(fw packet p);

| uvm_event start_copy;                                                |

|----------------------------------------------------------------------|

| uvm_event copy_finished;                                             |

| <u>fw_packet_pkt:</u>                                                |

| <pre>\$cast(pkt, p.clone());</pre>                                   |

| case ( <u>pkt.currentEvent</u> )                                     |

| pc: begin                                                            |

| int res [\$ <u>]:</u>                                                |

| res = pc_start_labels.find_index(x) with (x == p.pc_event)           |

| <pre>if(<u>res.size()</u> == 1) begin</pre>                          |

| <pre>copy_t = labels_map(p.pc_event);</pre>                          |

| <pre>start_copy = ep.get("start_copy");</pre>                        |

| <pre>start_copy.trigger();</pre>                                     |

| end                                                                  |

| <pre>res = pc_end_labels.find_index(x) with (x == p.pc_event);</pre> |

| <pre>if(<u>res.size()</u> == 1) begin</pre>                          |

| <pre>copy_finished = ep.get("copy_finished");</pre>                  |

| <pre>copy_finished.trigger();</pre>                                  |

| end                                                                  |

| end                                                                  |

| dut state: begin end                                                 |

| variable: begin <u>end</u>                                           |

| endcase                                                              |

| dfunction: write pc pkt                                              |

The **fw\_packet** is received through a port and it generates a trigger for the checker.

eccellera systems initiative

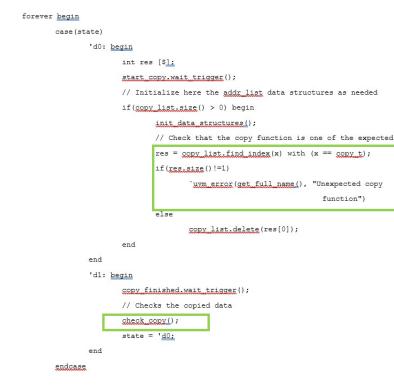

# Case Study1: copy check

The checker is started to check the correct execution of an operation.

eccellera Systems Initiative

### Case Study2: variable checkers

| function void write fw p | kt(fw packet fw pkt):                                                         |

|--------------------------|-------------------------------------------------------------------------------|

| fw packet pkt;           |                                                                               |

| Scast(pkt, fw pkt.clos   | ne()):                                                                        |

| case (pkt.currentEvent   |                                                                               |

| pc: pegin                |                                                                               |

| end                      |                                                                               |

| dut state: begin         |                                                                               |

| end                      |                                                                               |

| variable: begin          |                                                                               |

| if(fw_rea                | dy) begin                                                                     |

|                          | ase (pkt.variableName)                                                        |

|                          | "vout min ra" : begin                                                         |

|                          | void' (CHECK yout min var (pkt.variableValue, 0));                            |

|                          | end                                                                           |

|                          | " <u>vout min rb" :</u> begin                                                 |

|                          | <pre>void'(CHECK vout min var(pkt.variableValue,1));</pre>                    |

|                          | end                                                                           |

|                          | " <u>vout max ra" :</u> begin                                                 |

|                          | <pre>void'(<u>CHECK vout max var(pkt.variableValue</u>,0));</pre>             |

|                          | end                                                                           |

|                          | " <u>yout_max_rb"</u> : begin                                                 |

|                          | <pre>void'(CHECK yout max var(pkt.variableValue,1));</pre>                    |

|                          | end                                                                           |

|                          | "yout transition rate ra" : begin                                             |

|                          |                                                                               |

|                          | <pre>void'(CHECK vout transition rate var(pkt.variableValue,0));</pre>        |

|                          | end                                                                           |

|                          | "yout_transition_rate_rb" : begin                                             |

|                          | <pre>void'(<u>CHECK vout transition rate var(pkt.variableValue</u>,1));</pre> |

|                          | end                                                                           |

|                          | licase                                                                        |

| end                      |                                                                               |

| end                      |                                                                               |

| endcase                  | len .                                                                         |

| endfunction : write fw p |                                                                               |

The **fw\_packet** is received through a port. The expected hardware properties (e.g.a register content) is checked according the value of the variable within the packet .

### Conclusion

|                            | Pros                                                                                                                                             | Cons                                                                                                                                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FW-Centric (FPGA) approach | Can be used for Performance Analysis/Stress<br>testing on FPGA/HW-emulator                                                                       | Limited debug capabilities<br>Limited code coverage<br>No self-checking capabilities from UVM<br>world<br>Few capabilities of analog emulation                                                                              |

| UVM-Centric (VAL) approach | Full self-checking capabilities from UVM<br>world<br>Easy to debug<br>High Code Coverage                                                         | Scenarios written in FW language<br>Verification eng. must manage aspects<br>related to FW development (scatter file,<br>compiler option etc.)<br>Can't be used for Performance<br>Analysis/Stress test on FPGA/HW-emulator |

| Novel Approach             | Full self-checking capabilities from UVM<br>world<br>Easy to debug<br>High Coverage<br>Limited changes to usual FW and Verification<br>workflows | Can't be used for Performance<br>Analysis/Stress test on FPGA/HW-emulator                                                                                                                                                   |

We successfully implement the novel methodology and reached all the predefined target.

### Next step

1. To extend the approach to a multi-core IC.

2. To implement coverage analysis of the firmware with specific covergroup and/or line code coverage

### Questions

Any question is well accepted... 😳