# A Unified Framework for Multilanguage Verification IPs Integration

UVC

Surinder Sood, Selvakumar Krishnamoorthy, Gaurav Jalan

SmartPlay Technologies

#### Introduction

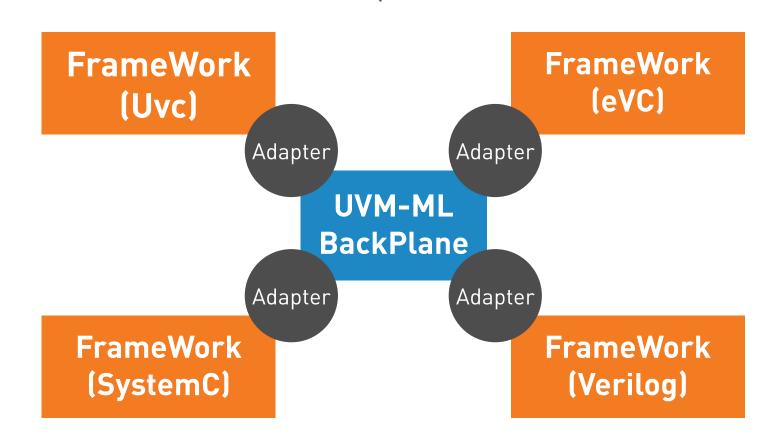

UVM –ML framework combines multi language IP and make them work together for any verification task. The basic ML setup is as shown below:

### The Setup

Example demonstrating 2 + 1 IP integration: 1 UVC and 2 eVC

#### **SV TOP** uvm\_test (SV) uvm\_env (SV) **Virtual Sequencer** Virtual Sequende Exported sequence & seq Exported sequence & seq item of eVC1 item of eVC2 Framework 1 Framework 2 **SV UVC** ml\_sequencer\_proxy ml\_sequencer\_proxy Config eVC 2 eVC 1 Config Config Sequencer Sequencer Monitor Driver BFM BFM Monitor Monitor

#### Objectives

#### Deploying ML framework to achieve -

- Reuse existing verification IPs irrespective of HVL used for representation

- Enabling faster bring-up of SoC testbench

- More focus on verification than testbench development at SoC level

- Optimized code with proven verification IPs

- Minimize verification environment bugs

- Faster time to market

#### Framework to support -

- Heterogeneous Objection Mechanism

- Configuration mechanism across multiple eVCs and UVCs

- Reuse of existing sequences, assertions, coverage and scoreboard

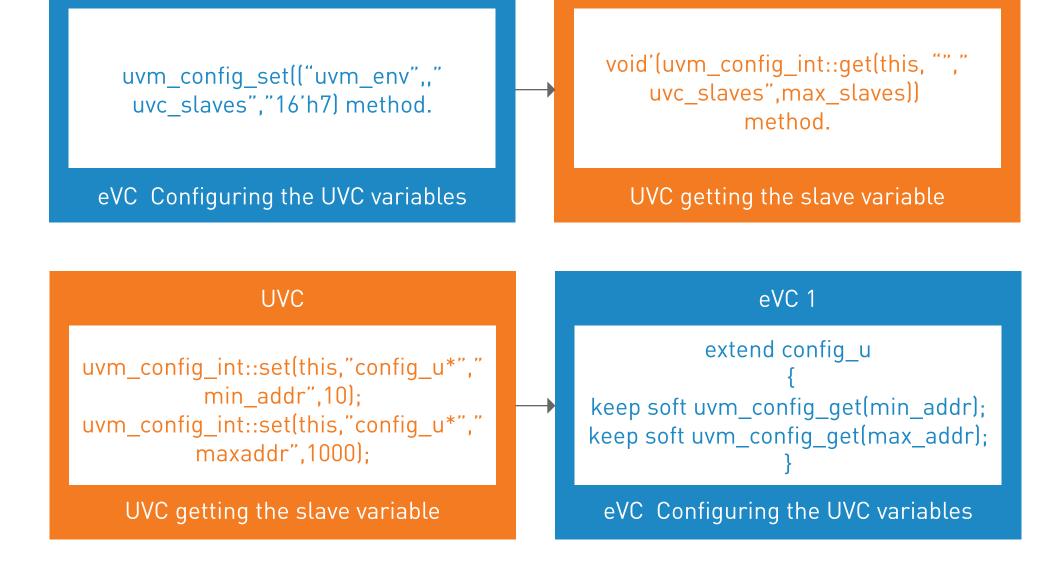

# Configuration Mechanism: eVC to UVC

#### and Vice Versa

eVC 1

The Heterogeneous configuration mechanism

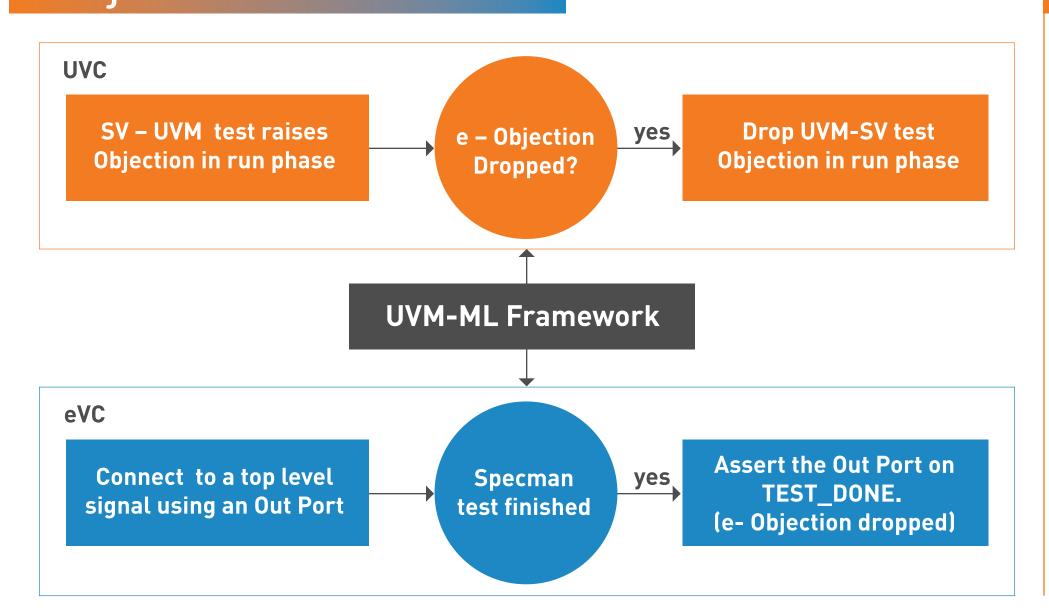

#### Objection Mechanism

Heterogeneous Objection Mechanism

## Conclusions

#### UVM-ML framework helps in achieving -

- 1. SV based Virtual sequencer to control the multi-eVC sequences

- 2. Phase propagation across frameworks, e.g. build phase from UVC to underlying eVC

- 3. Configuration of the eVC from UVM-SV environment both statically and dynamically

- 4. Phase Synchronization

- 5. Graceful termination of tests from top-level

#### Proposed future work -

- 1. Enhanced Debugging and tracing capabilities

- 2. Messaging service mechanism at the ML level

- 3. Propagating Errors to the underlying slaves (eVC in this case)

- 4. A global objection mechanism

#### References:

- 1. B. Sniderman, V. Yankelevich, "Techtorial: UVM Multi-Language: Technology and Reference Application", CDNLive Users Conference, Santa Clara CA, March 2013, http://www.cadence.com/cdnlive/na/2013/Pages/default.aspx.

- 2.G. Leshem, V. Yankelevich, B. Sniderman. "UVM-ML Whitepaper. A Modular Approach for Integrating Verification Frameworks" (available for download at http://forums.-accellera.org/files/file/65-uvm-ml-open-architecture.

#### Organization:

SmartPlay Technologies (I) Pvt. Ltd. Golden Towers, Kodihalli, Old Airport Road, Bangalore – 560 017 Tel: +91 80 43504444