## A Methodology for Interrupt Analysis in Virtual Platforms

### Puneet Dhar **Synopsys**® Silicon to Software™

## Agenda

- Introduction

- Interrupts in Virtual Prototyping

- Challenges in Debugging Interrupts

- Proposed Analysis Methodology

© Accellera Systems Initiative

- RH850 Adaptation

- Conclusions

### **Pre-Requisites**

- Basic understanding of

- System C scheduling

- Temporal Decoupling

- Interrupt Handling in Instruction Set Simulators (ISS)

DESIGN AND V

## Introduction

- An interrupt is a request to the processor to suspend its current program and transfer control to the *Interrupt Service Routine* (ISR).

- A developer must know if the design is

- Processor intensive

- Interrupt intensive

- Interrupt handling should be

- Timely (esp. when safety critical)

- Memory and processor efficient

# Interrupts in Virtual Prototyping

- A key usecase of any Virtual Prototype(VP) is system software development

- Use of Interrupts is common in system software

- Important for developers to understand interrupts and prevent associated issues – interrupt overloading, stack overflows etc.

- Empirically its known, interrupts

- Hard to get completely right

- Difficult to track down

With right means, VP can be a powerful tool to design efficient software for interrupt based systems

## Challenges in Debugging Interrupts

- Peculiar/rare preconditions

- Multiple sources and sinks

- Interrupt Enable/Disable

- Masks/Priority settings

- Missed Interrupts

- Separate Execution Flow

- Nested Interrupts, Reentrancy

- Context management/Stack Corruption

- Multi-level ISR, Delayed Procedural Calls (DPC)

- Unnoticed Faults/Violations/Traps

## Additional challenges in a VP

- If the VP uses temporarily decoupled ISS :

- Interrupts are only handled at quantum boundaries.

- Interrupts external to VP (e.g. pulse from USB) can be missed

- A large static quantum leads to

- Loss of Inter Processor Communication

- Missed Peripheral Interrupts

- Timing Issues

### Shortcomings in existing methodology

- Investigate various traces

- Debug Log trace

- Instruction, function, register trace

- Pin Value trace

- Verify correct execution by

- Assembly level debugging

- Putting breakpoints on pins/registers/instructions

- Examining values in pins, registers

- Manual, time and effort intensive

- Sparsely distributed information

- Time to converge to actual issue may take multiple days

© Accellera Systems Initiative

## A solution helps if it

- Is easy to integrate with an ISS

- Meaningfully presents the distributed information on

- Events, register settings and actual handling

- Latencies and execution of ISR

- Missed/Pending/Masked interrupts

- Helps developer assess if it's an interrupt related problem

- Helps developer to profile the software

### Proposed Interrupt Analyzer based Methodology

### A Quick Glance

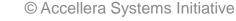

### How to integrate an ISS

#### Implement an IssIf to

- Register interrupt capabilities

- HW , SW Interrupts

- No. of channels for HW

- HW IRQ pins

- HW ACK pins

- ISR Addresses

- Allow Analyzer to fetch

- Core Time

- Register Values

- Program Counter

- Pin Values

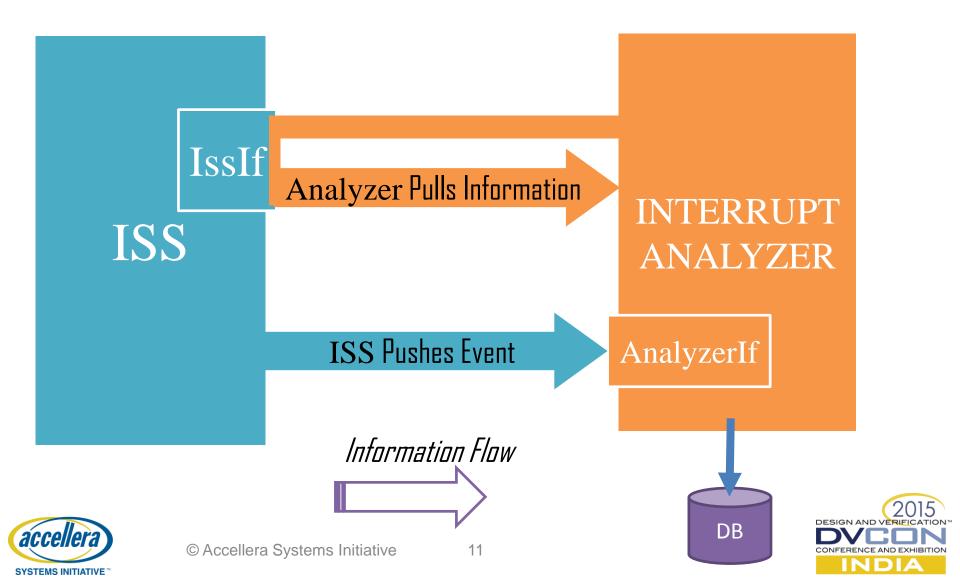

#### Use AnalyzerIf to

- Signal Pin Events:

- IRQ

- ACK

- Signal ISR Event:

- Request check/Notify for ISR entry

- Notify returns from ISR

### Implementation Overview

#### Analysis ISS Interface (PULL Interface)

- Pull Initial information on

- Interrupt Names

- HW/SW type

- Channel Nos.

- Register Set

- ISR Address Strategy

- Pull information at relevant PUSH Events

- Core Time

- Program Counter Info

- Register Values

- Pin Values

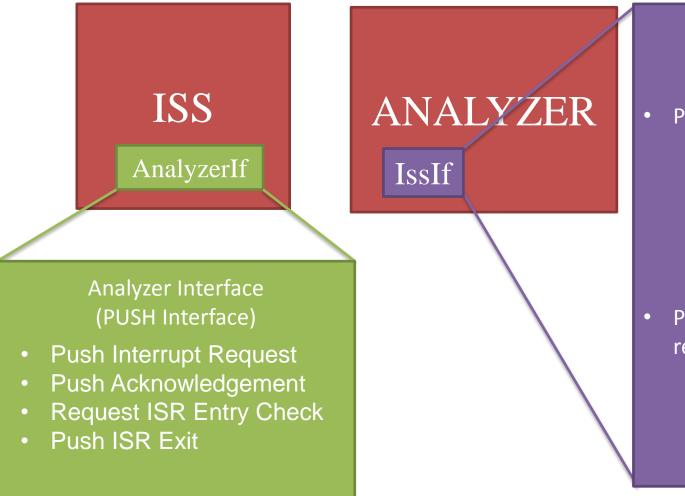

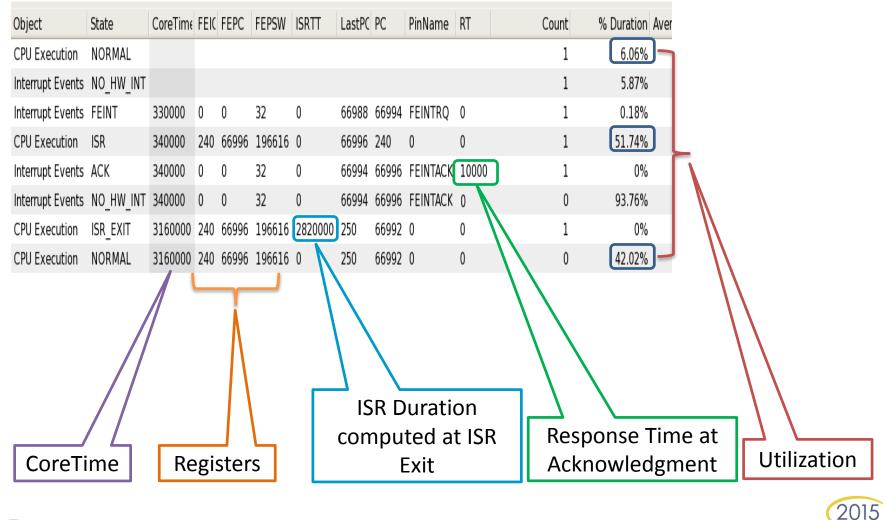

## **Output: Informatics**

| Analysis Elements  | Details covered                                 |  |  |  |

|--------------------|-------------------------------------------------|--|--|--|

| Pin Events         | IRQ, ACK, Messages                              |  |  |  |

| ISR Events         | Entry, Exit, Fall-Through                       |  |  |  |

| Latencies          | ACK Response, ISR Duration<br>(DPC not covered) |  |  |  |

| IRQ Special Events | Masked IRQ, Pending IRQ,<br>Missed IRQ          |  |  |  |

| Register Set       | Mask, Status and Cause registers                |  |  |  |

DESIGN AND VERIEIC

## **Information Table**

#### Example 1 from Use Cases

© Accellera Systems Initiative

DESIGN AND VERIFICA

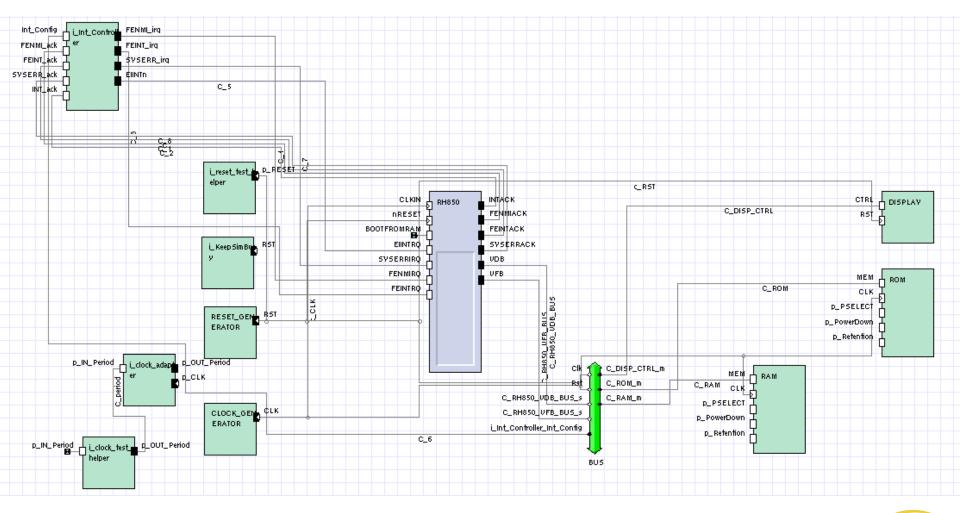

## **RH850** Based Adaption

- A platform with Renesas RH850 ISS interfaced with an interrupt controller and peripherals

- Quantum: Both dynamic and static configurations

- Virtual Platform is designed running in Synopsys

Virtualizer environment

### Platform in use

2015 DESIGN AND VERIFICATION

### Example Use Cases

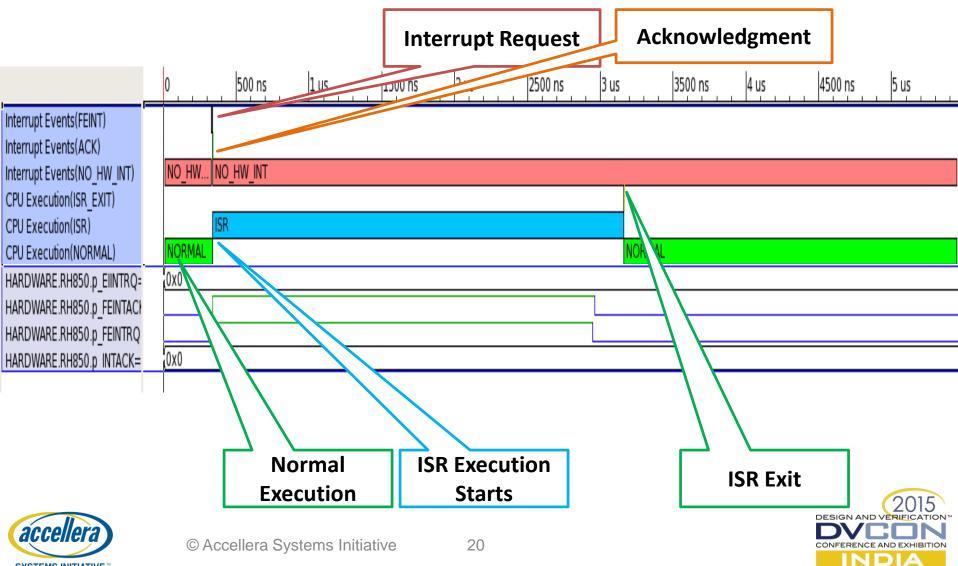

## (1) Analyzing a HW Interrupt:

SYSTEMS INITIATIVE

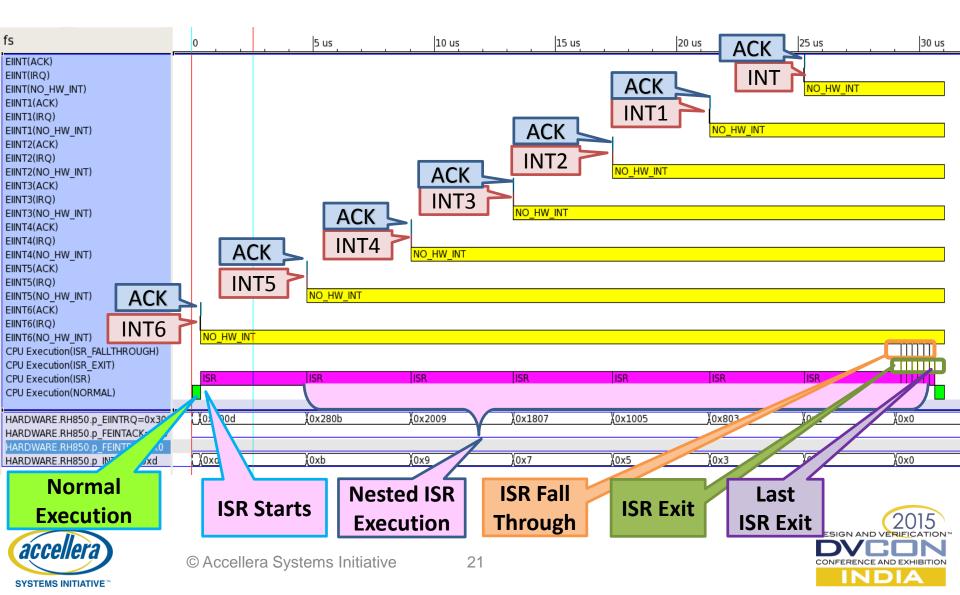

## (2) Analyzing Nested Interrupts

# (2) Analyzing Nested Interrupts

| Object        | State    | CoreTime | ISRNam€ | ISRTurnaroundTime |

|---------------|----------|----------|---------|-------------------|

| CPU Execution | ISR_EXIT | 30400000 | EIINT5  | 25650000          |

| CPU Execution | ISR_EXIT | 30170000 | EIINT4  | 21120000          |

| CPU Execution | ISR_EXIT | 29940000 | EIINT3  | 16690000          |

| CPU Execution | ISR_EXIT | 29710000 | EIINT2  | 12360000          |

| CPU Execution | ISR_EXIT | 29480000 | EIINT1  | 8130000           |

| CPU Execution | ISR_EXIT | 29250000 | EIINT   | 4000000           |

| Object | Stat€ | CoreTime | PinName  | ResponseTime | Object        | State | CoreTime | ISRName | % Duration |

|--------|-------|----------|----------|--------------|---------------|-------|----------|---------|------------|

| EIINT  | ACK   | 25250000 | EIINTACK | 10000        | CPU Execution | ISR   | 350000   | EIINT6  | 14.18%     |

| EIINT1 | ACK   | 21350000 | EIINTACK | 10000        | CPU Execution | ISR   | 4750000  | EIINT5  | 13.86%     |

| EIINT2 | ACK   | 17350000 | EIINTACK | 10000        | CPU Execution | ISR   | 9050000  | EIINT4  | 13.54%     |

| EIINT3 | ACK   | 13250000 | EIINTACK | 10000        | CPU Execution | ISR   | 13250000 | EIINT3  | 13.21%     |

| EIINT4 | ACK   | 9050000  | EIINTACK | 10000        | CPU Execution | ISR   | 17350000 | EIINT2  | 12.89%     |

| EIINT5 | ACK   | 4750000  | EIINTACK | 10000        | CPU Execution | ISR   | 21350000 | EIINT1  | 12.57%     |

| EIINT6 | ACK   | 350000   | EIINTACK | 10000        | CPU Execution | ISR   | 25250000 | EIINT   | 12.89%     |

DESIGN AND VERIE

CONFERENCE AND EXHIBITION

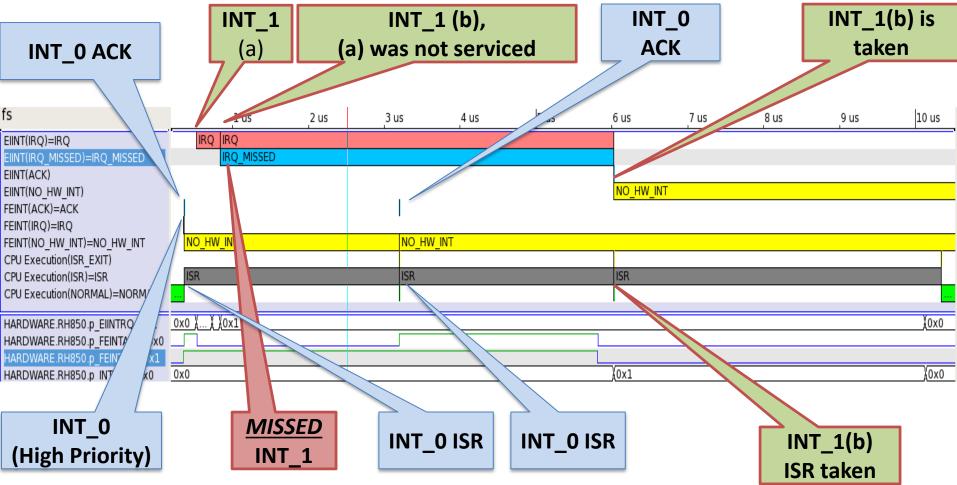

## (3) Analyzing Missed Interrupts

23

2015

DESIGN AND VERIFICA

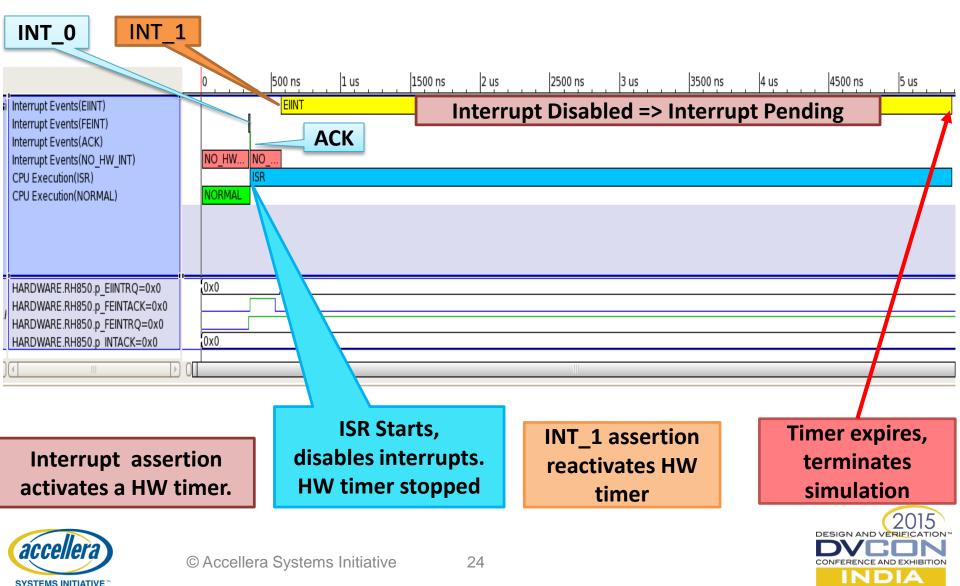

## (4) Analyzing Pending Interrupts

## Conclusions

Analyzer consolidates the distributed debugging techniques and helps

- Organize interrupt data in tables

- Graphically assess interrupt handling

- Point out interrupt anomalies

- Track software exceptions

- Expedite debugging and profiling

- Expedite setting of optimal static quantum

- Present a post-silicon use case for debugging interrupt issues

### Questions