# A Holistic Overview on Preventive & Corrective Action To Handle Glitches

Rohit Kumar Sinha Parimal Das

### What are Functional Glitches

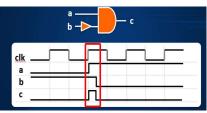

- ✓ Perennial problem in digital designs and functional glitches occur frequently in combination logic but are not simulated accurately.

- ✓ Difference between the event-driven simulation engine and the physical implementation of the RTL.

- ✓ Glitches in the clock domain crossing paths or glitches in the synchronous paths with exception such as set\_false\_path, set\_multicycle\_paths, set\_max\_delaypaths, path margins etc can also lead to Silicon failures.

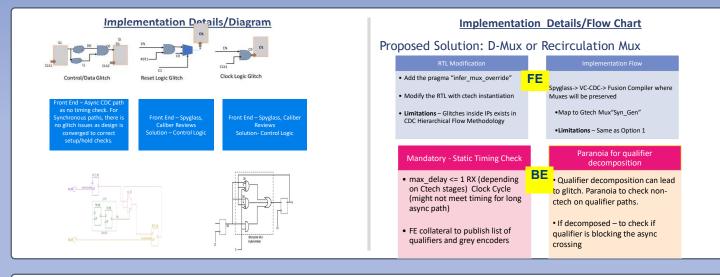

#### Proposed Methodology/Advantages

- 1. The data on the bus must always be stable before the synchronized edge-triggered qualifier signal goes high in the receive domain.

- 2. The data on the bus must remain stable after the qualifier has gone high, long enough to meet the hold-time requirements in the receive domain

- 3.Due to the uncertainty of how many receive clock cycles it will take for the qualifier to go through the synchronizer, there is a further requirement that the data on the CDC bus must be stable for at least two/three receive-domain clock cycles.

## Results Table

Glitch Validation for the Synchronous Paths with Exceptions

There are multiple categories of paths reported and only glitch prone paths are identified. In cross domain crossing paths there are five ways of constraining the timing paths:

- asynchronous paths

- max\_delay constraining paths

- mcp exception

- path margin based paths

- single cycle paths

Unintentional glitches can alter the desired functionality of the circuit and design could fail

Conclusion

For the first time both in front end and backend automation is developed to have glitch free design for clock crossing paths.

Glitches are difficult to catch in the design flows because of its unpredictable nature

Finding glitches and relying on back-end flows are very late and expensive, hence defining the design practices to prevent them is the only scalable solution

In this paper a successful method of avoiding and prevention of glitches in clock cross domain paths is achieved and proposed for future use

## **REFERENCES**

**References**

<u>Rohit Kumar Sinha(s), Left Shift Mechanism to Mitigate Gate Level Asynchronous Design</u> Challenges, DVCon-India, 2021