# An Elegant scoreboard eco-system deploying UVM Callbacks, Parameterization for Multimedia designs from Imaging perspective

Chakravarthi Devakinanda Vurukutla, Samsung Semiconductor India Research, chakravart.d@samsung.com

Sahana Ranganathan, Samsung Semiconductor India Research, <u>sahana.ranga@samsung.com</u> Devendra Satish Bilaye, Samsung Semiconductor India Research, <u>dev.bilaye@samsung.com</u> Vivek Kumar, Samsung Semiconductor India Research, <u>vivek9.kumar@samsung.com</u> Karthik Majeti, Samsung Semiconductor India Research, <u>k.majeti@samsung.com</u>

*Abstract*— One of the principal features driving mobile market is the camera specification. Based on the needs of consumer market, there is a demand for camera sensors from the entry level to premium ones. An Image Sensor SOC will have many image processing sub-blocks to capture a high quality image. A CMOS image sensor has an Analog component which captures light, converts it to digital value and feeds it to digital pipeline. There are noises involved in Analog operation and manufacturing defects during fabrication. The digital pipeline has to mitigate these noises and defects for a high quality image output. Finally, the high quality image is sent to the host via Industry standard serial protocol. For a high quality image, advanced image processing IPs and algorithms are developed, resulting in increased design complexity. Additionally, the ever increasing need for higher resolution Image Sensors leads to larger designs. Due to market demand and aggressive schedules, the timelines for Design Verification shrink along with emphasis on quality validation. The key component for verification of any ISP (Image Signal Processing) algorithm is scoreboard, where we compare RTL output against golden reference model. A robust, configurable scoreboard architecture is vital to meet the verification quality in a short time frame. This architecture needs to be reusable across all sub-blocks. This paper details the practices followed in scoreboard implementation to achieve high quality verification within the stipulated time.

Keywords— scoreboard; callbacks; verification; parameterization; image sensor; multimedia; adaptability; scalability; reusability;

# I. INTRODUCTION

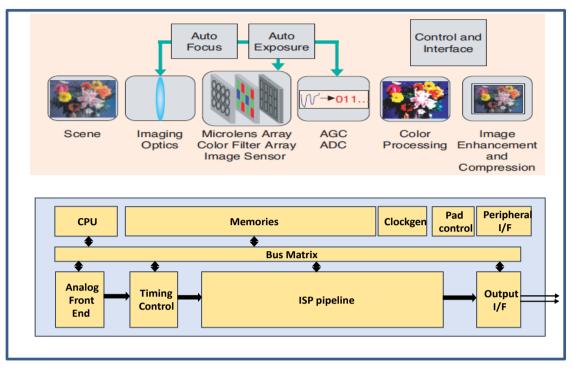

A typical CMOS Image Sensor (Figure 1.) has Analog and Digital components. Analog components consist of the Active Pixel sensor(APS) and Analog-to-Digital converters(ADC). An APS can be considered as 2d-array with rows and columns. Each entry in an array is a photo-diode. This photo-diode along with analog circuitry is called as pixel. Pixel is the building block of Image Sensor which captures light and converts to electric signal. These electric signals are converted to digital values using ADCs. The timing block in digital logic generates the control signals to Analog, extracts the information from pixel array and sends the data to digital pipeline. Different kinds of Analog noises emerge during the operation of pixels and ADCs. Defects like dead-pixel arise while manufacturing. The digital pipeline, which has the image processing algorithms has to alleviate these noises and defects for a high quality image output. The processed image data is sent to the host via industry standard serial protocol. Every complete readout of APS is termed as a Frame. Sending out first pixel indicates the start of the frame and the last pixel, as end of the frame. Based on the application and use-case, multiple frames can be readout. The number of such frames captured in a second is called FPS (Frames per Second).

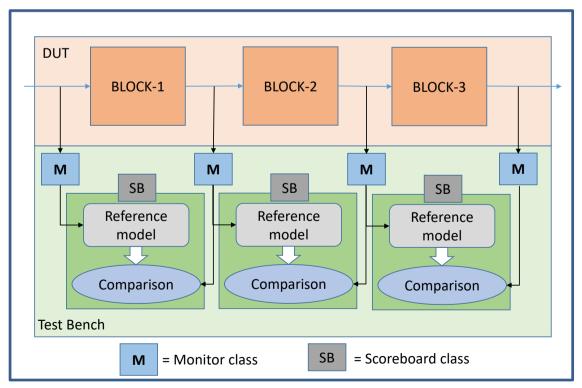

There are multiple sub-blocks involved in image processing to mitigate different kinds of noises and defects. To validate the functionality of these image processing blocks, we use the reference models in our scoreboard. A typical scoreboard architecture has been depicted in Figure 2.

Figure 1. A typical CMOS Image Sensor

A high level language is used to implement the image processing algorithms, which serve as golden reference models. Generally, the reference model is written in 'C'. In scoreboard, the RTL is qualified using the C-models. Each sub-block has an individual scoreboard. For the industry standard output protocol, we use VIPs (Verification IPs) to verify the functionality.

Figure 2. A typical Scoreboard architecture

### II. CHALLENGES IN VERIFICATION

With short design timelines and time to market, verification team need to have stable base verification environment which can be tuned easily for new designs. The scoreboard architecture needs to address the following challenges:

#### A. Scalability and Adaptability

The end consumer is expecting DSLR (Digital Single-Lens Reflex Camera) like performance in Mobile Camera. To meet such emerging market trends, combined with the ever increasing demand for higher resolutions, the CMOS image sensor for mobiles has become very sophisticated. The rise in number of blocks associated in enhancing the image quality as well as their increasing algorithm complexity adds to the challenge. As an illustration, there are more than 40 blocks(IPs) in a premium Image Sensor. Verification team has to ensure that all the blocks are thoroughly verified with their respective reference models. Due to aggressive timelines, the scoreboard setup for all the IPs has to be brought up in quick time. Therefore, the scoreboard structure should be generic to be easily scalable for all the blocks. Further, we are witnessing the growth in market for Image Sensors in Automotive Industry and other security applications. The design of Image Sensors for these industries will be different from that of Mobile phones. The scoreboard structure should be easily adaptable to cater to different design needs.

#### B. Reusablity and Portability

We have seen the increase in resolution of Image Sensors from 5MP(Mega Pixel) to 200MP. With the increase in resolution of Image sensors, the simulation times have shot up from hours to days. Now verification teams have to use Emulation (Simulation Acceleration) along with simulation to meet the timelines. Hence, the scoreboard architecture should be reusable across simulation and emulation platforms.

With newer and complex algorithms, need arises to do both IP and sub-system level verification. This IP setup should be seamlessly portable to the SOC testbench to verify the entire pipeline. This becomes easy if we have a standard scoreboard architecture across IP and SOC environments.

# C. Resource Management

With larger resolutions, the amount of data to be stored and processed by scoreboard of each block increases. With many blocks, this creates a cascading effect that may lead to simulation crashes. In addition to this, the simulation time is in order of days for such designs. Even though Simulation Acceleration setup on emulation is able to solve the large run-time issue, it is limited by high cost hardware and limited licenses.

Considering aggressive timelines, members in team have to work in parallel on different blocks independently. There is a need to manage the manpower, licenses and run times to meet the product schedule. The scoreboard architecture should be versatile to solve the above concerns.

From the challenges mentioned above, it is evident that lack of proper scoreboard architecture will leave out gaps in verification. So, for high quality functional verification and faster execution, it is necessary to streamline the scoreboard framework.

# III. PROPOSED SOLUTION

To address all these challenges, we have developed a Scoreboard eco-system using parameterization, UVM Callbacks, and a file-based monitor.

#### A. Parameterization

Parameters are like constants local to that particular class instance. The parameter value can be used to define a set of attributes in class. Default values can be overridden by passing a new set of parameters during instantiation. This is called parameter overriding [1]. We will discuss how we used parameterization in UVC (Universal Verification Component) and Scoreboard classes to address the defined challenges.

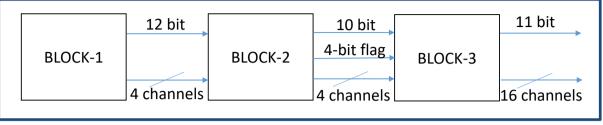

There are standard design specifications which change across SOCs as well as IPs within a SOC. In an Image sensor, there are multiple sub-blocks, each working with different number of data channels, data bit-width, along

with different sideband signals. Figure-3 illustrates this for few blocks. Typically, there are 10-15 standard design parameters that vary across blocks in the chain.

Further, we need scoreboard for each block to find the source of issue with the help of reference model. Based on its implementation, reference model interface format can be different as compared to RTL. For example, reference model works on 1-channel interface whereas RTL has 4-channel interface. Hence, there is a need to maintain the same format for proper comparison between reference model and RTL.

To address these challenges, in the proposed scoreboard architecture, we have defined 2 types of parameters – UVC parameters and Scoreboard parameters.

• UVC parameters: These parameters are used in UVC logic which constitutes the driver, sequencer, sequences and monitor. UVC parameters can be defined as shown in Figure 4. These parameters are incorporated in logic of UVC to make the code generic and easily reusable. Transaction packet and interface can be defined as shown in Figure 5. In Figure 6, it is shown how monitor logic is parameterized and incorporated in testbench.

| interface uvc_if#(uvc_params_t params=uvc_default_params);                      | parameter uvc_params_t uvc_block1_params = |  |

|---------------------------------------------------------------------------------|--------------------------------------------|--|

| logic clock;                                                                    | '{                                         |  |

| logic [(params.DATA_WIDTH-1):0] data[params.NUM_CHANNELS];                      | 4, //NUM_CHANNELS                          |  |

| logic [(params.HADDR_WIDTH-1):0] haddr;                                         | 12, //DATA_WIDTH                           |  |

| logic [(params.VADDR_WIDTH-1):0] vaddr;                                         | 16, //HADDR_WIDTH                          |  |

| logic [(params.FLAG_WIDTH-1):0] flag;                                           | 16, //VADDR_WIDTH                          |  |

| endinterface : uvc_if                                                           | 0, //FLAG_WIDTH                            |  |

|                                                                                 | };                                         |  |

| typedef struct packed {                                                         |                                            |  |

| int NUM_CHANNELS; //This parameter captures the info on number of data channels | parameter uvc_params_t uvc_block2_params = |  |

| int DATA_WIDTH; //This parameter captures the bit-width of data channels        |                                            |  |

| int HADDR_WIDTH; //This parameter captures the horizontal addrress width        | 4, //NUM_CHANNELS                          |  |

| int VADDR_WIDTH; //This parameter captures the vertical addrress width          | 10, //DATA_WIDTH                           |  |

| int FLAG_WIDTH; //This parameter captures the bit-width of flag                 | 16, //HADDR_WIDTH                          |  |

| } uvc_params_t;                                                                 | 16, //VADDR_WIDTH                          |  |

|                                                                                 | 4, //FLAG_WIDTH                            |  |

| parameter uvc_params_t uvc_default_params = '{                                  | };                                         |  |

| //Default values using defines                                                  |                                            |  |

| `NUM_CHANNELS,                                                                  | parameter uvc_params_t uvc_block3_params = |  |

| `DATA_WIDTH,                                                                    | '{                                         |  |

| `HADDR_WIDTH,                                                                   | 16, //NUM_CHANNELS                         |  |

| `VADDR_WIDTH,                                                                   | 11, //DATA_WIDTH                           |  |

| `FLAG_WIDTH                                                                     | 16, //HADDR_WIDTH                          |  |

| };                                                                              | 16, //VADDR_WIDTH                          |  |

|                                                                                 | 0, //FLAG_WIDTH                            |  |

|                                                                                 | };                                         |  |

Figure 4. UVC parameters

| //UVC INTERFACE<br>interface uvc_if#(uvc_params_t params=uvc_default_params);<br>logic clock;<br>logic [(params.DATA_WIDTH-1):0]<br>data[params.NUM_CHANNELS];<br>logic [(params.HADDR_WIDTH-1):0] haddr;<br>logic [(params.VADDR_WIDTH-1):0] upden | <pre>//TRANSACTION PACKET class uvc_data_packet_c#(uvc_params_t params = uvc_default_params) extends uvm_sequence_item; //{ rand bit [(params.DATA_WIDTH-1):0] data_channel[params.NUM_CHANNELS-1:0]; rand bit [(params.HADDR_WIDTH-1):0] haddr; rend bit [(params_VADDR_WIDTH-1):0] haddr;</pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| logic ([params.VADDR_WIDTH-1):0] vaddr;<br>logic [(params.FLAG_WIDTH-1):0] flag;<br>endinterface : uvc_if                                                                                                                                           | rand bit [(params.VADDR_WIDTH-1):0] raddi;<br>rand bit [(params.FLAG_WIDTH-1):0] vaddr;<br>rand bit [(params.FLAG_WIDTH-1):0] flag;<br>endclass: uvc_data_packet_c //}                                                                                                                            |

Figure 5. UVC Interface and Transaction packet

| //UVC_MONITOR<br>class uvc_monitor_c#(uvc_params_t params=uvc_default_params) extends<br>uvm_monitor;<br>uvc_data_packet_c#(params) packet_collected;<br>virtual interface uvc_if #(params) vif;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <pre>//TESTBENCH TOP module testbench_top(); virtual interface uvc_if#(uvc_block1_params) uvc_block1_if; virtual interface uvc_if#(uvc_block2_params) uvc_block2_if; virtual interface uvc_if#(uvc_block3_params) uvc_block3_if;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>function void build_phase(uvm_phase phase);<br/>super.build_phase(phase);<br/>assert(uvm_config_db#(virtual interface pvi_if#(params))::get(this, "",<br/>"vif",vif);<br/>packet_collected = uvc_data_packet_c#(params)::type_id::create<br/>(\$sformatf("packet_collected"),this);<br/>endfunction : build_phase<br/>virtual task run_phase(uvm_phase phase);<br/>forever begin<br/>@(posedge vif.clock)<br/>if(CONDITION) begin //{<br/>packet_collected.haddr &lt;= vif.haddr;<br/>packet_collected.haddr &lt;= vif.haddr;<br/>for(int i=0; i<params.num_channels;i++)<br>packet_collected.dta_channel[i] &lt;= vif.data[i];<br/>for(int i=0; i<params.flag_width;i++)<br>packet_collected.flag[i] &lt;= vif.flag[i];<br/>end //}<br/>end<br/>endtask : run_phase<br/>endclass: uvc_monitor_c</params.flag_width;i++)<br></params.num_channels;i++)<br></pre> | <pre>dut dut_inst(); //DUT instantiation<br/>initial<br/>begin<br/>uvm_config_db #(virtual interface<br/>uvc_if#(uvc_block1_params))::set (null, "*",<br/>"vif",uvc_block1_if);<br/>uvm_config_db #(virtual interface<br/>uvc_if#(uvc_block2_params))::set (null, "*",<br/>"vif",uvc_block2_if);<br/>uvm_config_db #(virtual interface<br/>uvc_if#(uvc_block3_params))::set (null, "*",<br/>"vif",uvc_block3_if);<br/>end<br/>//Example for block1/block2/block3 connections<br/>assign uvc_block1_if.data[0] = `DUT_BLOCK1.data_channel0;<br/>assign uvc_block2_if.flag = `DUT_BLOCK1.data_channel1;<br/>assign uvc_block3_if.haddr = `DUT_BLOCK3.haddr;<br/>assign uvc_block3_if.vaddr = `DUT_BLOCK3.vaddr;<br/>endmodule</pre> |

Figure 6. Monitor parameterization example

• Scoreboard parameters: These are used to keep the attributes configurable across different blocks in the scoreboard framework. Parameters can be defined as in Figure 7.

| typedef struct{<br>int INPUT_DATAW; //Reference model Input data width<br>int OUTPUT_DATAW; //Reference model Output data width<br>int NUM_OF_IN_CHANNEL; //Reference model data channels<br>int NUM_OF_OUT_CHANNEL; //Expected data channels for<br>comparison<br>string REF_OUT_FILE_HIER; // Directory name.<br>int ADDR_CHECK_EN; //To enable address checks<br>int FLAG_CHECK_EN; //To enable flag checks<br>} sb_params_t; | parameter sb_params_t sb_params_block2 = '{ 12,//INPUT_DATAW ; 10, //OUTPUT_DATAW 4, //NUM_OF_IN_CHANNEL ; 'BLOCK2", //REF_OOUT_FILE_HIER; 1, //ADDR_CHECK_EN 1 //FLAG_CHECK_EN };                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>parameter sb_params_t sb_params_default_params = '{ 10,/INPUT_DATAW ; 10, //OUTPUT_DATAW 4, //NUM_OF_IN_CHANNEL ; 4, //NUM_OF_OUT_CHANNEL ; "DEFAULT", //REF_OOUT_FILE_HIER; 1, //ADDR_CHECK_EN 1 //FLAG_CHECK_EN };</pre>                                                                                                                                                                                                  | <pre>parameter sb_params_t sb_params_block3 = '{ 10.//INPUT_DATAW ; 11, //OUTPUT_DATAW 4, //NUM_OF_IN_CHANNEL; 16, //NUM_OF_OUT_CHANNEL; "BLOCK3", //REF_OOUT_FILE_HIER; 1, //ADDR_CHECK_EN 0 //FLAG_CHECK_EN };</pre> |

Figure 7. Scoreboard Parameters

# B. UVM\_CALLBACKS

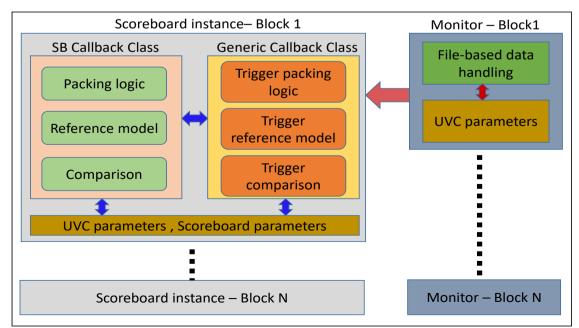

Callbacks are empty methods with a call to them. UVM provides a set of classes, methods and macros to implement callbacks [2]. In this section, we will discuss how we used UVM callbacks in our scoreboard architecture. In the proposed scoreboard architecture, there are two main components - Scoreboard Callback class and Generic Scoreboard Class. We will discuss how we utilized these two components along with parameterization to make the scoreboard easily scalable.

Scoreboard callback class: In this class, we have the implementation details of packing logic and comparison logic between reference model and RTL outputs, as demonstrated in Figure 8. A base callback class is defined first and callback class for each block is extended from the base callback class. In this base callback class, we implement the packing and comparison logic in common tasks. As per the requirement of dedicated packing and comparison logic for different blocks, this can be achieved by using function override in their respective callback classes.

//SB\_CALLBACK\_CLASS //{ //INDIVIDUAL BLOCK CALLBACK CLASS class sb\_callback\_base#(sb\_params\_t params\_sb = class sb\_callback\_block2#(sb\_params\_t params\_sb = sb\_default\_params,uvc\_params\_t input\_params = uvc\_default\_params, sb\_default\_params,uvc\_params\_t input\_params = uvc\_default\_params,uvc\_params\_t output\_params = uvc\_default\_params) uvc\_params\_t output\_params = uvc\_default\_params) extends uvm\_callback; extends sb\_callback\_base#(params\_sb,input\_pvi\_params,output\_pvi\_params); virtual function void pack input data(): //callback usage //Implement the input packing needed for Reference model function new(string name="sb\_callback\_block2"); endfunction: pack\_input\_data super.new(name); endfunction: new virtual function void pack\_input\_data (); //{ virtual function void pack\_output\_data(); //FUNCTION OVERRIDE //callback usage endfunction : pack\_input\_data //} //Implement the output packing needed for comparison endfunction: pack\_output\_data virtual function void pack\_output\_data (); //{ virtual function void pack\_flag\_data(); //FUNCTION OVERRIDE //callback usage endfunction : pack\_output\_data //} //Implement the flag packing. virtual function void run\_ref\_and\_compare (); //{ endfunction: pack\_output\_data //FUNCTION OVERRIDE virtual function void run\_ref\_and\_compare(); endfunction : run\_ref\_and\_compare //} //callback usage //Implement the reference model call and comparison logic endclass : sb\_callback\_block2 endfunction: run\_ref\_and\_compare class sb\_callback\_block3#(sb\_params\_t params\_sb = virtual task reset\_sb(); sb\_default\_params,uvc\_params\_t input\_params = uvc\_default\_params,uvc\_params\_t output\_params = uvc\_default\_params) //callback usage //Implement the reset logic extends endtask: reset\_sb sb\_callback\_base#(params\_sb,input\_pvi\_params,output\_pvi\_params); endclass : sb\_callback\_block3 endclass: sb\_callback\_class

Figure 8. Scoreboard Callback class

• Generic scoreboard class: In this class (Figure 9), we have the logic to control when to trigger the packing logic, reference model execution and the comparison logic. As the name suggests, this class is generic and

#### //GENERIC SB

class generic\_sb\_c#(sb\_params\_t params\_sb = sb\_default\_params,uvc\_params\_t input\_params = uvc\_default\_params, uvc\_params\_t output\_params = uvc\_default\_params) extends uvm\_scoreboard;

#### `uvm\_register\_cb(generic\_sb\_c#(params\_sb,input\_params,output\_params),sb\_callback\_base)

// TLM PORTS

`uvm\_analysis\_imp\_decl(\_in\_data) `uvm\_analysis\_imp\_decl(\_out\_data) `uvm\_analysis\_imp\_decl(\_flag\_data)

uvm\_analysis\_imp\_in\_data #(transaction\_packet#(input\_params), generic\_sb\_c#(params\_sb,input\_params,output\_params)) input\_data; uvm\_analysis\_imp\_out\_data #(transaction\_packet#(output\_params), generic\_sb\_c#(params\_sb,input\_params,output\_params)) output\_data; uvm\_analysis\_imp\_flag\_data #(transaction\_packet#(output\_params), generic\_sb\_c#(params\_sb,input\_params,output\_params)) flag\_data;

#### //Trigger via TLM ports

function void write\_in\_data (input transaction\_packet#(input\_params) data\_pkt); //{ `uvm\_do\_callbacks(generic\_sb\_c#(params\_sb,input\_params,output\_params),sb\_callback\_base,pack\_input\_data()) `uvm\_info(params\_sb.BAS\_OUT\_FILE\_HIER, "CAPTURED\_INPUT\_DATA\_WRITE", UVM\_LOW) endfunction: write in data //} function void write\_out\_data (input transaction\_packet#(output\_params) data\_pkt); //{ `uvm\_do\_callbacks(generic\_sb\_c#(params\_sb,input\_params,output\_params),sb\_callback\_base,pack\_output\_data())  $`uvm_do_callbacks(generic\_sb\_c\#(params\_sb,input\_params,output\_params), sb\_callback\_base,run\_ref\_and\_compare()) \\$ endfunction: write\_out\_data //} function void write\_flag\_data (input transaction\_packet#(output\_params) data\_pkt); //{ `uvm\_do\_callbacks(generic\_sb\_c#(params\_sb,input\_params,output\_params),sb\_callback\_base,pack\_flag\_data()) endfunction: write\_out\_data // } virtual task run\_phase(uvm\_phase phase); super.run\_phase(phase); fork begin //{ forever @(negedge vseqr.vintf.Rstn pad or negedge vseqr.vintf.frame reset) begin //{ Trigger via EVENT `uvm\_do\_callbacks(generic\_sb\_c#(params\_sb,input\_params,output\_params),sb\_callback\_base,reset\_sb()) end// } end // } join\_none endtask: run\_phase endclass: generic\_sb\_c

Figure 9: Generic scoreboard class

controlled by parameters. The trigger can be done by TLM ports or through events. We register scoreboard callback class with this generic scoreboard class using uvm\_register\_cb. The generic scoreboard and the callback classes are connected as shown in Figure 10.

```

// sb_callback instances

sb_callback_block2#(sb_params_block1,uvc_block1_in_params,uvc_block2_in_params) callback_block2;

sb_callback_block3#(sb_params_block1,uvc_block2_in_params,uvc_block3_in_params) callback_block3;

//generic_scoreboard instances

generic_sb_c#(sb_params_block2,uvc_block1_in_params,uvc_block2_in_params) sb_block2;

generic_sb_c#(sb_params_block3,uvc_block2_in_params,uvc_block3_in_params) sb_block3;

//Callback connections

uvm_callbacks#(generic_sb_c#(sb_params_block2,uvc_block1_in_params,uvc_block2_in_params),sb_callback_base)::add(sb_block2,

callback_block2);

uvm_callbacks#(generic_sb_c#(sb_params_block3,uvc_block2_in_params,uvc_block3_in_params),sb_callback_base)::add(sb_block3,

callback_block3);

```

Figure 10. Callbacks and Scoreboard connections

# C. File-based data handling

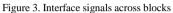

With the help of parameterization and callback-based scoreboard, we have implemented a portable, adaptable, scalable and reusable scoreboard architecture. As the scoreboard is streamlined, the emphasis is on the possible methods to improve simulation speed. Reference models are designed to work on complete frame information. Therefore, the entire frame data needs to be captured before we can trigger the reference model and scoreboard. Monitor uses queues to capture the data from RTL and send it to the scoreboard using TLM ports. With higher resolutions and addition of HDR (High Dynamic Range) like features, monitor has to capture many folds of data in each block monitor. The huge amount of data causes the simulator to slow-down and possibly crashing at times, while transferring the data from monitor to scoreboard. It is observed that in Emulation (Simulation Acceleration) setup, this data transfer takes lot of time. To tackle this, we approached data handling through files. In this section, we will discuss how we used file-based monitor to solve the crash issue and speed up the simulation.

In this approach, we write the data into a file instead of accumulating entire data in queues. At the start of frame, we open a file and the incoming data is collected in it. We adopted a hybrid approach of capturing small amounts of data in a queue and then storing in a file, instead of performing continuous file operations. We achieved better performance with this hybrid approach. At frame end, the file is closed and scoreboards are triggered. As the entire eco-system (Figure 11) is parameterized, the scoreboard knows the file name based on parameter and perform the desired operation. This logic is easily portable for emulation as well.

Figure 11. Scoreboard eco-system

# IV. CONCLUSION AND RESULTS

- 1. With this highly reusable setup, scoreboard can be quickly sanitized in Acceleration platform and regressions can be run in simulation. We can leverage the benefits of both simulation and emulation in parallel.

- 2. Owing to generic implementation and configurability, the setup is easily scalable to large designs and members of the team can work on it independently which helps in faster execution.

- 3. With the new approach in monitor, gain is achieved in run-time (Table I). A high resolution image sensor simulation which earlier ran for 2 days before facing simulator crash without reference model execution, completed in a day with the proposed updates, with all scoreboard logic executed.

- 4. The scoreboard setup can be easily ported to other multimedia teams and applications with minimum effort.

- 5. The readability of code improved a lot and is easy for everyone to ramp up on it.

- 6. The entire scoreboard architecture is automated and it reduces the bring-up time. A large sensor with 45 blocks is brought up in 2 days.

- 7. Need for big\_mem LSF (Load Sharing Facility) has come down with file-based monitor. This is very helpful as big\_mem licenses are limited.

| Category(with scoreboard)                   | Queue based Monitor | File based monitor | Improvement |

|---------------------------------------------|---------------------|--------------------|-------------|

| Simulation time for<br>200MP – Single frame | 50 hours            | 28 hours           | 44%         |

| Simulation time for 200MP – 2 frames        | 105 hours           | 45 hours           | 57%         |

| Simulation time for 12.5<br>MP – 2 frames   | 12 hours            | 10 hours           | 16%         |

| Emulation run time for 200MP – Single frame | 14 hours            | 10 hours           | 28%         |

Table I. Improvements with file-based monitor

#### REFERENCES

- $[1] \quad https://verificationguide.com/systemverilog/systemverilog-parameterized-classes/$

- [2] https://verificationguide.com/uvm/uvm-callback/