SECURE CONNECTIONS FOR A SMARTER WORLD

DVCONFERENCE AND EXHIBITION

EUROPE

MUNICH, GERMANY DECEMBER 6 - 7, 2022

# uvm\_mem – challenges of using UVM infrastructure in a hierarchical verification

Joachim Geishauser, NXP Deutschand GmbH, Munich, Germany (joachim.geishauser@nxp.com)

Aditya Chopra, NXP Semiconductors India Pvt Ltd, Noida, India (aditya.chopra@nxp.com)

Stephan Ruettiger, NXP Deutschand GmbH, Munich, Germany (stephan.ruettiger@nxp.com)

Luca Rossi, NXP Semiconductors France, Mougins, France (luca.rossi@nxp.com)

Sanjay Kakasaniya, NXP USA INC, Austin, USA (sanjay.kakasaniya@nxp.com)

L.N. Zhang, NXP Qiangxin (Tianjin) IC Design Co., Ltd, Tianjin, China(lina.zhang1@nxp.com)

# Agenda

- Use Cases

- UVM Memories

- Basics

- Limitations

- NXP memory driver API

- Architecture

- Hierarchical Simulation

- Emulation

- Conclusion

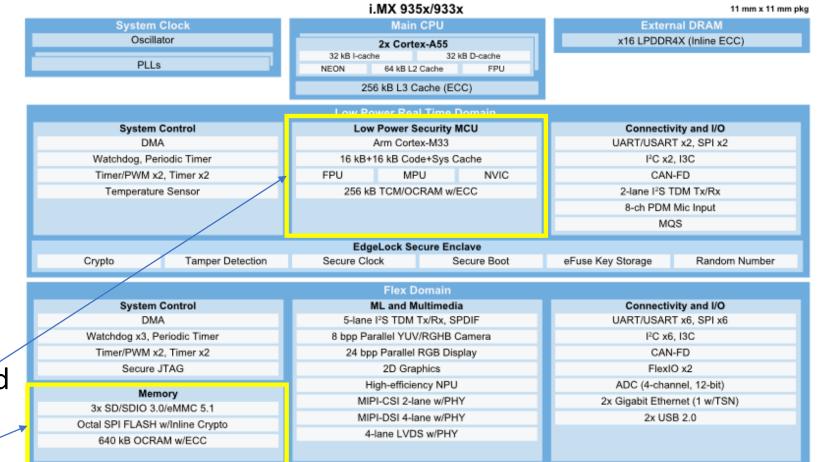

#### Use Case

- SoC are build out of subsystems

- SoC contains many cores

- Every core can have its own map

- SoC contains multiple memories

- Memories are shared

Subsystems with Core

Subsystems with Memory

# **UVM** Memories

- The uvm\_mem is an extension of the uvm\_object, therefore it is not a UVM component, and it will not be phased like a component.

- The closest class in the UVM framework to the uvm\_mem is the uvm\_reg class.

## UVM Memories: Basics

- Like the uvm\_reg the uvm\_mem support front door and back door access

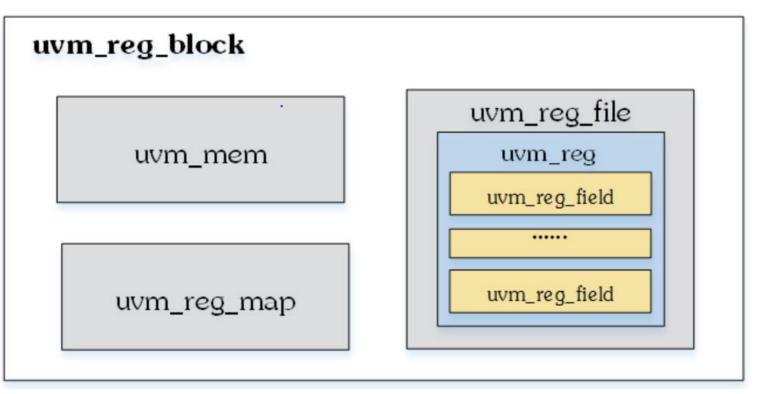

- The uvm\_reg\_block base class can be used to represent a design hierarchy which contains an address map uvm\_reg\_map and a memory modelized with the memory abstraction base class uvm\_mem accessible via the address map.

- Based on the topology and complexity of the design and of the physical interfaces, one or more memories could be added to the address map, and a register block could contain one or more address maps.

# UVM Memories: Basics (cont.)

- In the UVM top\_env multiple instances of class uvm\_reg\_block can be used to create a model representing the design hierarchy

- For example, a m\_root\_reg\_block can contain 2 sub-blocks m\_a\_reg\_block and m\_b\_reg\_block, derived from the same class and mapped to different memory addresses of the m\_root\_reg\_block in the uvm\_reg\_map.

- Through add\_mem method, memory can be added to multiple address maps if it is accessible by different interfaces, however the address maps to which it is added need to have the same parent block of the memory.

- The register blocks need to be locked to allow the computation of the final memory map.

## UVM Memories: Limitations

• One uvm\_reg\_block supported for a uvm\_reg\_map

```

if (mem.get_parent() != get_parent()) begin

_uvm_error("RegModel",

{"Memory '",mem.get_full_name(),"' may not be added to address map '",

get_full_name(),"' : they are not in the same block"})

return;

end

```

• A uvm\_reg\_map can only have one parent map

```

'uvm_error("RegModel",

{"Submap '",child_map.get_full_name(),"' may not be added to this ",

"address map, '", get_full_name(),"', as the submap's parent block, '",

child_blk.get_full_name(),"', is not a child of this map's parent block, '",

m_parent.get_full_name(),"'"})

```

if (m\_parent\_map != null) begin <u>`uvm\_error</u>("RegModel", \$sformatf("Map \"%s\" already a submap of map \"%s\" at offset 'h%h", get full name(), m parent map.get full name(), m parent map.get submap offset(this))); return; end

• A uvm\_mem can only be in one uvm\_reg\_block

\_\_uvm\_warning("RegModel",

{"Memory '",get\_full\_name(),"' is not contained within map '",map.get\_full\_name(),"'",

(caller == "" ? "": {" (called from ",caller,")"})})

## NXP memory driver API: Motivation

- Almost all NXP devices contain an embedded core which needs memory from which SW will be executed.

- Every testbench need to load memory with content to verify the device.

- Safety, geometry and size requirements cause that the memory implementation becomes not straight forward

- Loading memory cuts and calculate ECC need to be handled by infrastructure

- Due to SoC complexity, SoC assembly is done hierarchically

- Hierarchical structure needs to be supported.

- Devices have multiple cores, with different address maps associated.

- Verification spawns the whole space from system to gate level as well as different engines

- Infrastructure need to support the usage of the same code along the 9 yards.

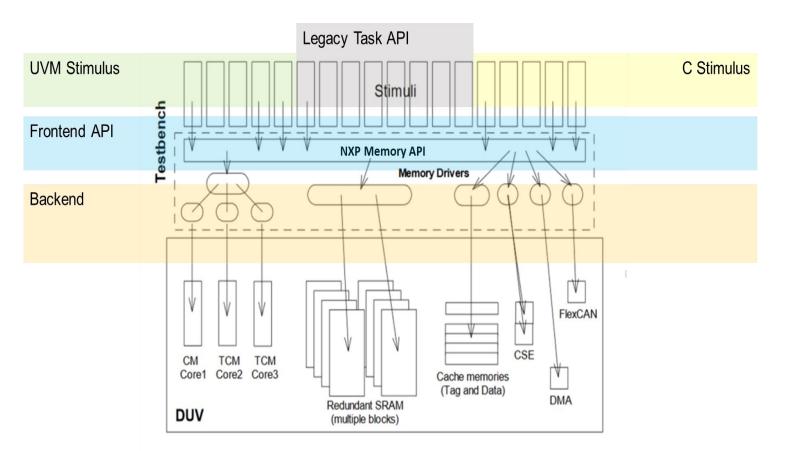

# NXP memory driver API: Architecture

- Architecture is split into frontend and backend.

- Frontend API available for

- UVM sequences

- Verilog tasks

- C stimulus

- Connection to backend uses TLM2

- To support SC and emulation use cases

# NXP memory driver API: Frontend View

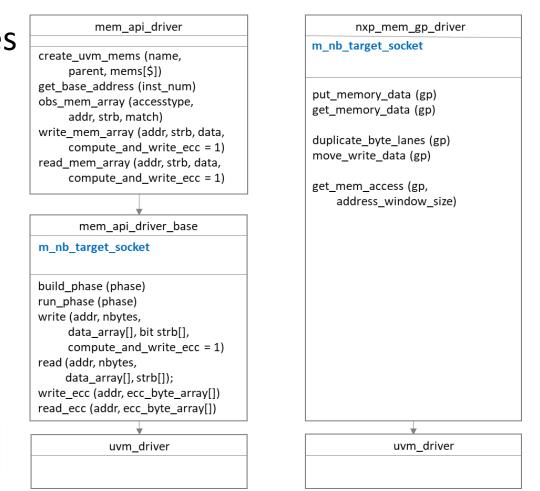

# NXP memory driver API: Backend View

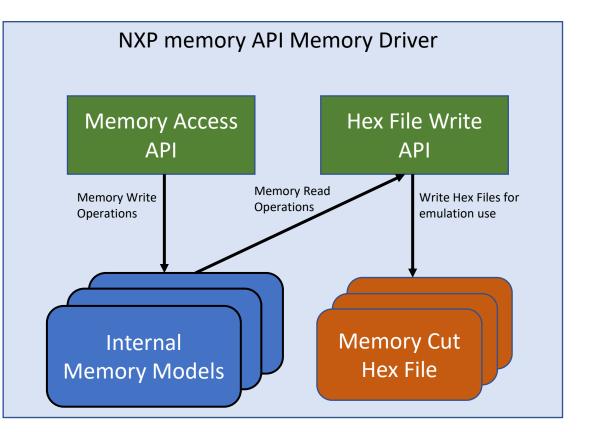

- Two types of memory driver's base classes are provided

- mem\_api\_driver is used for design internal memories

- nxp\_mem\_gp\_driver is used as a base for testbench memories

- Connection to the frontend is done via TLM2

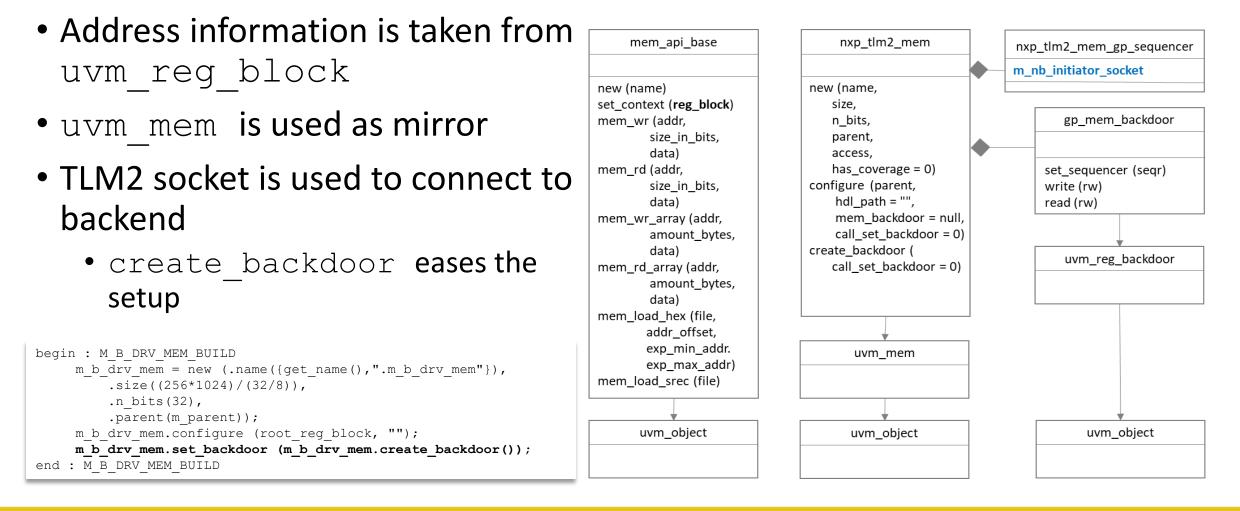

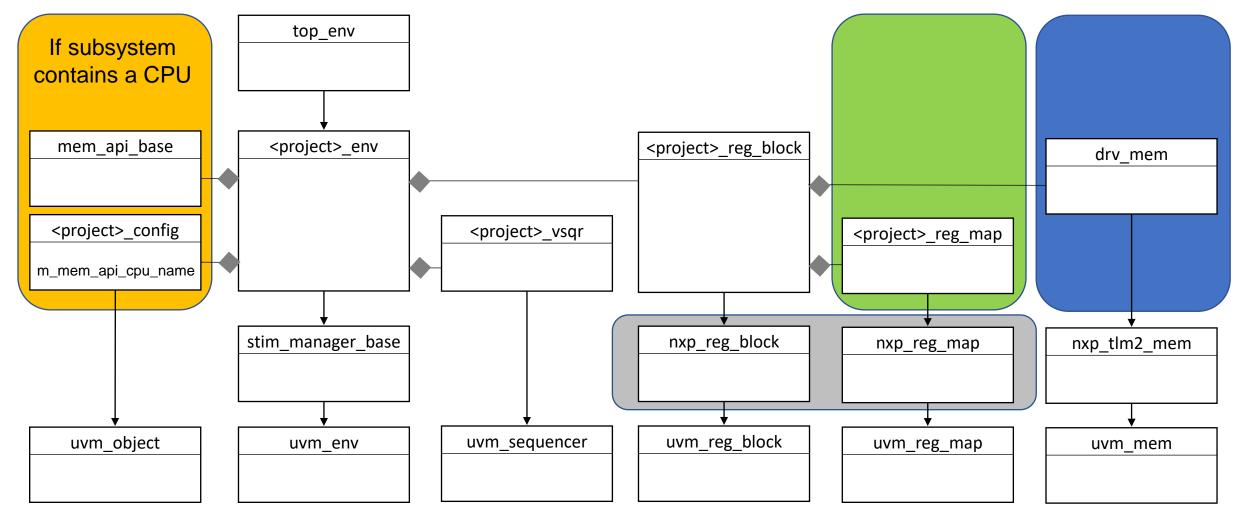

## NXP memory driver API: Building Blocks

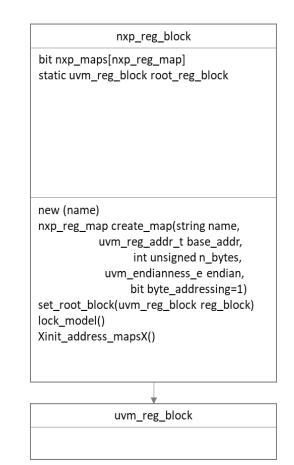

## NXP memory driver API: Overcome Limitations

• Multiple submap use case

m\_b\_reg\_block.m\_top\_b\_mem\_map.set\_submap\_offset(

m\_a\_reg\_block.m\_top\_a\_mem\_map, 32'h0A00\_0000);

• Map use in multiple uvm\_reg\_blocks

function void my\_nxp\_reg\_block::build ();

set\_root\_block (this); m\_top\_b\_mem\_map = create\_map (.name("m\_top\_b\_mem\_map"), .base\_addr(0), .n\_bytes(4), .endian(UVM\_LITTLE\_ENDIAN));

#### • To calculate the address map

function void my\_env::end\_of\_elaboration\_phase (uvm\_phase phase);

begin: A\_REG\_MODEL\_LOCK

m\_a\_reg\_block.lock\_model();

m\_a\_reg\_block.Xinit\_address\_mapsX();

end: A REG MODEL LOCK

nxp\_reg\_map

uvm\_reg\_addr\_t m\_reg\_maps[nxp\_reg\_map] uvm\_reg\_block m\_nxp\_parent uvm\_reg\_map m\_nxp\_root\_map

new (name) set\_submap\_offset (uvm\_reg\_map submap, uvm\_reg\_addr\_t offset)

get\_root\_map() Xinit\_address\_mapX()

set\_parent (uvm\_reg\_block parent) set\_root\_map (uvm\_reg\_map map) get\_parent\_map()

uvm\_reg\_map

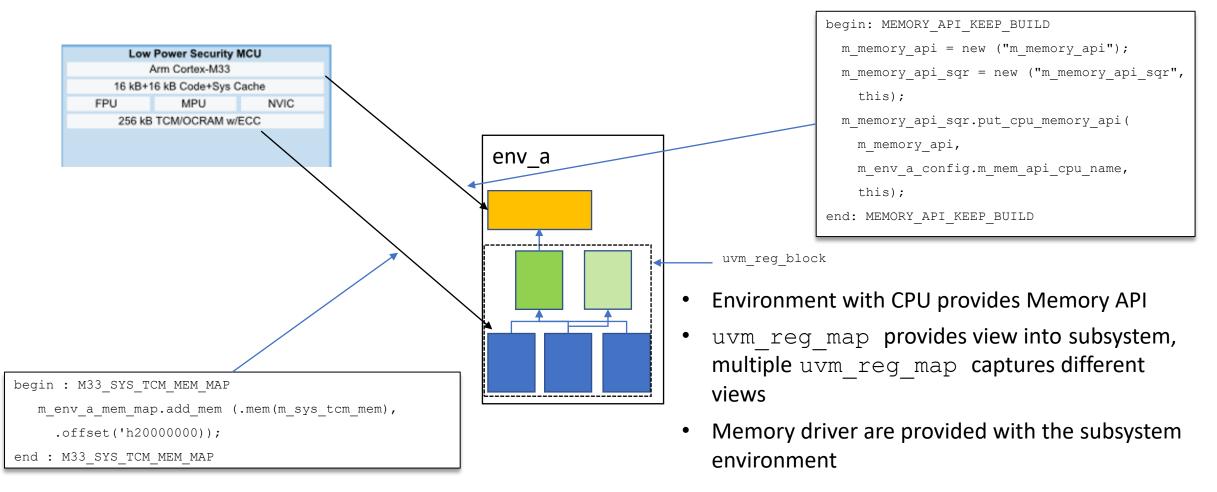

# Hierarchical Simulation: CPU Example

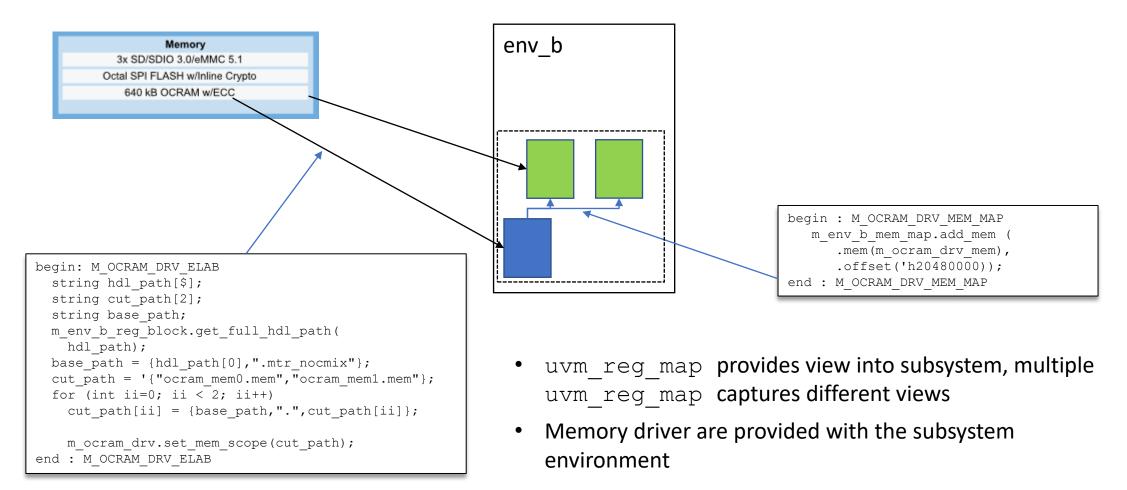

## Hierarchical Simulation: Memory Example

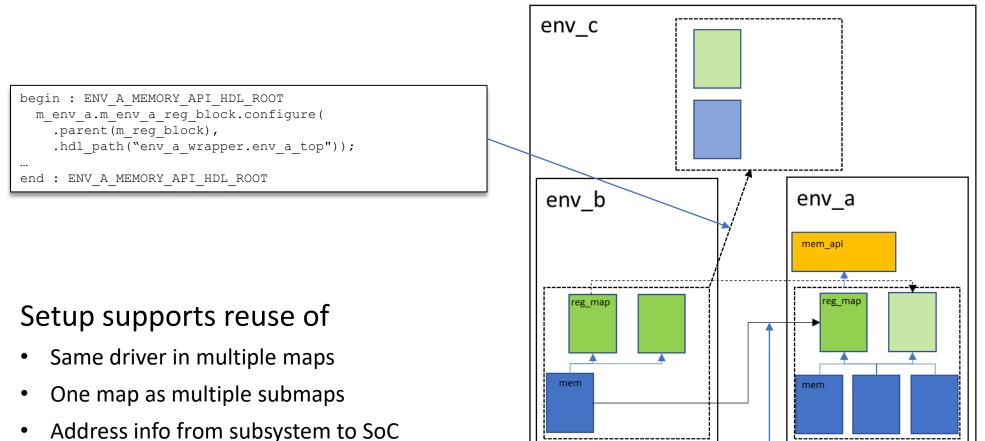

# Hierarchical Simulation: Assembly View

m\_env\_a.m\_env\_a\_reg\_block.m\_env\_a\_mem\_map.add\_mem(

m\_env\_b.m\_env\_b\_reg\_block.m\_sys\_tcm\_drv\_mem, 32'h20400000);

## NXP memory driver API: Emulation

- Infrastructure Reuse from Simulation to Emulation

- Increases efficiency and reduces development time

- Parameterized memory driver API Memory Drivers

- Easy portability to emulation memory models

- Supports different bit reordering and memory repair schemes in emulation models

- Models Internal Memories

- Internal memory models for each DUT memory cut

- Dynamic memory write operations to internal memories

- API to write hex files for each DUT memory cut executed after all memory write operations

- Dumped hex files loaded on corresponding DUT memory cuts

#### Conclusion

- Presented infrastructure addresses all requirements of the use case

- UVM limitations got addressed via extended UVM classes

- Overwritten UVM functions should have been renamed to make change visible

- Hierarchical assembly code captures level depended properties only

- Properties can be tested in a divide and conquer approach

- Assembly of testbench is accelerated

# Questions?

# Thank You for Attending this Presentation