DVCCONFERENCE AND EXHIBITION

EUROPE

MUNICH, GERMANY DECEMBER 6 - 7, 2022

# Unified firmware debug throughout SoC development lifecycle

D. Ciaglia <sup>1</sup>, *T. Winkler* <sup>1</sup>, J. Kundrata <sup>2</sup> <sup>1</sup> ams-OSRAM International GmbH <sup>2</sup> University of Zagreb

am osram

2

. . . . . .

### Agenda

- Introduction

- Background

- Proposed Approach

- Implementation of the DPI-based SoC Simulator

- Conclusions

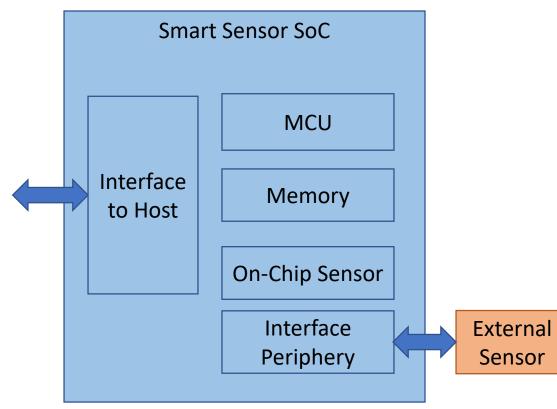

### Smart Sensors

- Consumer and automotive market demand

- Build-up intelligence

- Provide a smart sensor solution is key

#### **Pre-Silicon Verification**

- Create a test-bench close to the real system

- Leverage complete system internal observability

- Ensure bug-free design (hardware and firmware)

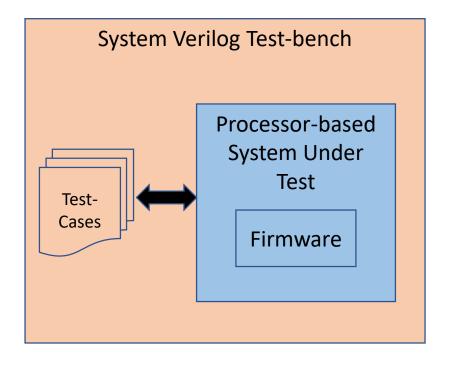

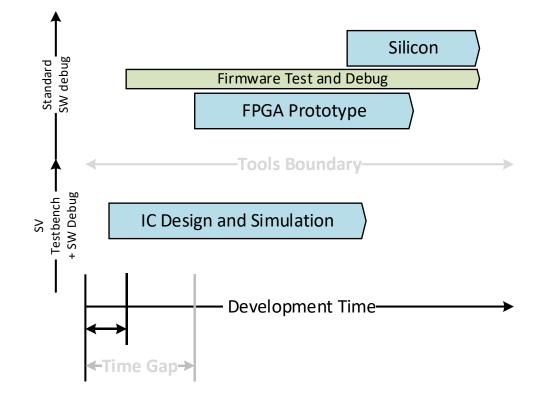

# Pre-Silicon Firmware Debugging

SYSTEMS INITIATIVE

- Build FPGA Prototype

- Implement SW test-cases

- Use the standard debug and test tools

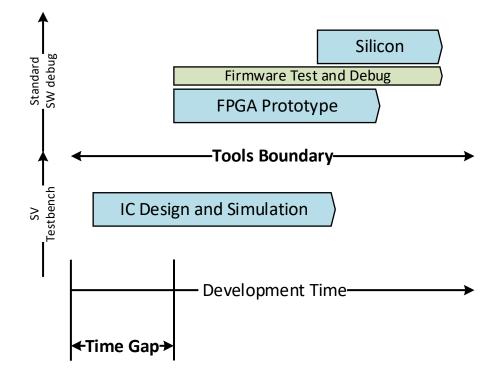

#### Limitations of Standard Approach

STEMS INITIATIVE

- System-Verilog tests cannot be reused for firmware debugging

- Firmware debugging is bound to FPGA prototype availability

#### **Co-Verification Techniques**

|  | Technique                  | Speed     | Timing | Software | Debug     | Cost      |

|--|----------------------------|-----------|--------|----------|-----------|-----------|

|  | Instruction set simulation | Medium    | No     | C Model  | Algorithm | Low       |

|  | HW/SW<br>co-verification   | Slow      | Yes    | Real     | HW/SW     | High      |

|  | Rapid<br>Prototyping       | Fast      | Yes    | Real     | Low       | Medium    |

|  | Emulation                  | Very fast | Yes    | Real     | Low       | Very high |

S INITIATIVI

- Use a technique during design phase

- Ensure high observability

- Maximize tests re-use

#### HW/SW Co-verification

- Key enabler for "shift left"

- Maximize firmware tests reuse

- Enables on-chip debugging

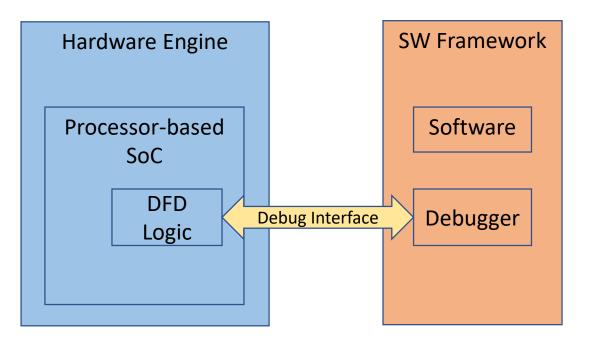

#### **Co-verification Environment**

- Direct SW interaction with HW

- Full observability guaranteed by HW Engine

- Design for Debug Logic for standard interface

- "Soft" debug interface

ESIGN AND VERIEICATION TO DESIGN AND VERIEICATIO

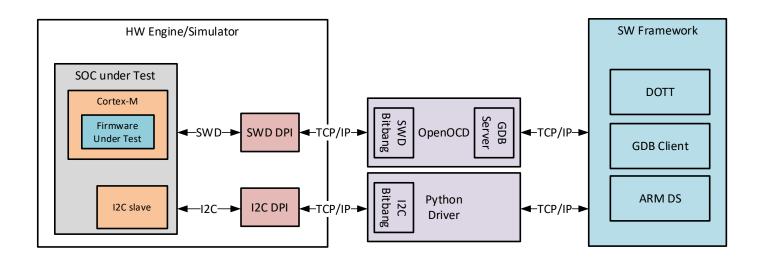

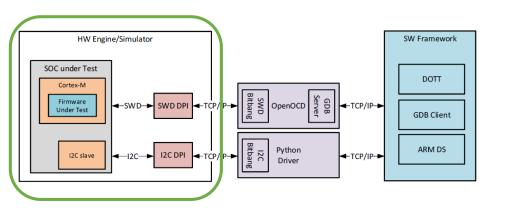

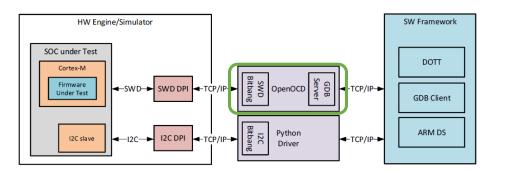

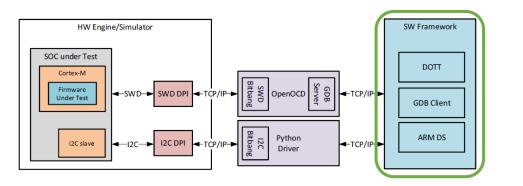

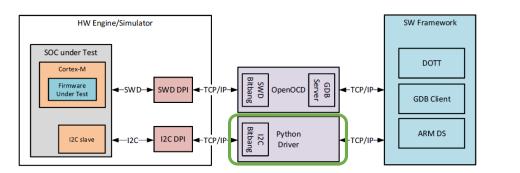

### Proposed Approach – Case Study

- Direct programming interface for HW/SW interaction

- Open source debugger

- Standard SW framework based on GDB

- Python-based DOTT for tests development

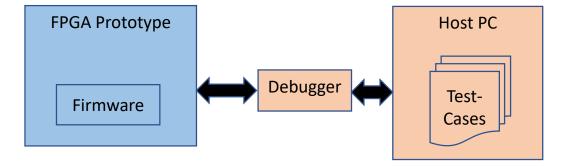

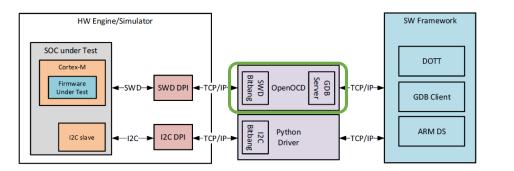

#### FPGA or Post-Si Debug Environment

- Swap the DPI with real debug probe

- Re-use of standard SW debug tools

- Re-use of test-cases

#### Simulation environment

- SV testbench --> SoC under Test + DPIs

- **SoC under Test** --> ARM Cortex-M core with SWD and I2C interfaces

- **SWD DPI** --> SWD debugger probe controlled via TCP port using a bitbang protocol and OpenOCD tool

- **I2C DPI** --> I2C master core controlled via TCP port using a bitbang protocol and a Python driver module

### Implementation of the SWD-DPI

- Based on OpenTitan implementation of JTAG DPI

- JTAG --> all pins are unidirectional

- SWD --> the data pin (SWDIO) is bidirectional

1 module swddpi #( parameter string Name = "swd0", // name of the SWD interface (display only) parameter int ListenPort = 44853 // TCP port to listen on 4)( 5 input logic clk i, input logic rst\_ni, output logic swd swclk, inout logic swd\_swdio, output logic swd nrst n 10 11); // bidirectional behaviour of SWDIO signal 13 reg swd swdoen, swd swdi, swd swdo; 14 15 assign swd swdio = swd swdoen ? swd swdo : 1'bZ; 16 assign swd swdi = swd swdio; 17 import "DPI-C" 19 function void swddpi tick(input chandle ctx, output bit swclk, output bit swdo, 20 21 output bit swdoen, input bit swdi, output bit nrst n);

#### swddpi.sv

#### Implementation of the SWD-DPI

| 1 | struct | swddpi_ | ctx | { |

|---|--------|---------|-----|---|

|---|--------|---------|-----|---|

- 2 // Server context

- 3 struct tcp\_server\_ctx \*sock;

- 4 // Signals

- 5 uint8\_t swclk;

- 6 uint8\_t swdo;

- 7 uint8\_t swdoen;

- 8 uint8\_t swdi;

- 9 uint8\_t nrst\_n;

#### 10 };

22

```

12 // parse received command byte

```

```

13 if (cmd >= 'd' && cmd <= 'g' || cmd == '0' || cmd == 'o') {

```

14 // swd write

```

15 char cmd_bit = cmd - 'd';

```

```

16 ctx->swclk = (cmd_bit >> 1) & 0x1;

```

```

17 ctx->swdo = (cmd_bit >> 0) & 0x1;

```

```

18 if (cmd == '0')

```

```

19 ctx->swdoen = 1;

```

```

20 if (cmd == 'o')

21 ctx->swdoen = 0;

```

```

ctx->swdoen = 0;

```

swddpi.c

| Command | Description                       |  |

|---------|-----------------------------------|--|

| 0       | Set the SWDIO line to output mode |  |

| 0       | Set the SWDIO line to input mode  |  |

| С       | Read the SWDIO line               |  |

| d       | Set SWCLK = 0 and SWDIO = 0       |  |

| е       | Set SWCLK = 0 and SWDIO = 1       |  |

| f       | Set SWCLK = 1 and SWDIO = 0       |  |

| g       | Set SWCLK = 1 and SWDIO = 1       |  |

# Configuration of the OpenOCD tool

- OpenOCD compiled using the SWD remote bitbang protocol patch

- Changes #3908, #4205 & #6044

- Configuration file:

- 1 adapter driver remote\_bitbang 2 remote\_bitbang\_host localhost 3 remote\_bitbang\_port 44853 4 transport select swd

5

- 6 swd newdap cortex\_m0p\_sim cpu -dp-id 0x0BC11477

- 7 dap create cortex\_m0p\_sim.dap -chain-position cortex\_m0p\_sim.cpu

- 8 target create cortex\_m0p\_sim cortex\_m -endian little -dap cortex\_m0p\_sim.dap

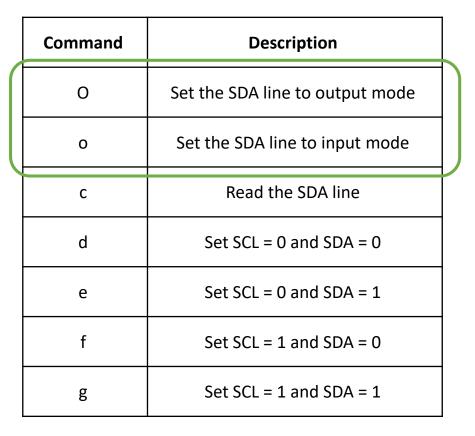

### Implementation of the I2C-DPI

- Based on OpenTitan implementation of JTAG DPI

- JTAG --> all pins are unidirectional

- I2C --> the data pin (SDA) is bidirectional

1 module i2cdpi #(

20

```

parameter string Name = "i2c0", // name of the i2c interface (display only)

parameter int ListenPort = 44855 // TCP port to listen on

4)(

input logic clk_i,

5

input logic rst ni,

output logic i2c_scl,

inout logic i2c sda

10);

// bidirectional behaviour of the sda line

12

13

reg i2c_sdaoen, i2c_sdai, i2c_sdao;

14

assign i2c sda = i2c sdaoen ? i2c sdao : 1'bZ;

15

assign i2c sdai = i2c sda;

16

************

import "DPI-C"

18

function void i2cdpi tick(input chandle ctx, output bit scl, output bit sdao,

19

output bit sdaoen, input bit sdai);

```

#### i2cdpi.sv

#### Implementation of the I2C-DPI

#### 1 struct i2cdpi\_ctx {

- 2 // Server context

- 3 struct tcp\_server\_ctx \*sock;

- 4 // Signals

- 5 uint8\_t scl;

- 6 uint8\_t sdao;

- 7 uint8\_t sdaoen;

- 8 uint8\_t sdai;

#### 9};

SYSTEMS INITIATIVE

11 // parse received command byte

```

12 if (cmd >= 'd' && cmd <= 'g' || cmd == '0' || cmd == 'o') {

```

- 13 // i2c write

- 14 char cmd\_bit = cmd 'd';

- 15 ctx->scl = (cmd\_bit >> 1) & 0x1;

```

16 ctx->sdao = (cmd_bit >> 0) & 0x1;

```

```

17 if (cmd == '0')

```

```

18 ctx->sdaoen = 1;

```

```

19 if (cmd == 'o')

20 ctx->sdaoen =

```

```

ctx->sdaoen = 0;

```

i2cdpi.c

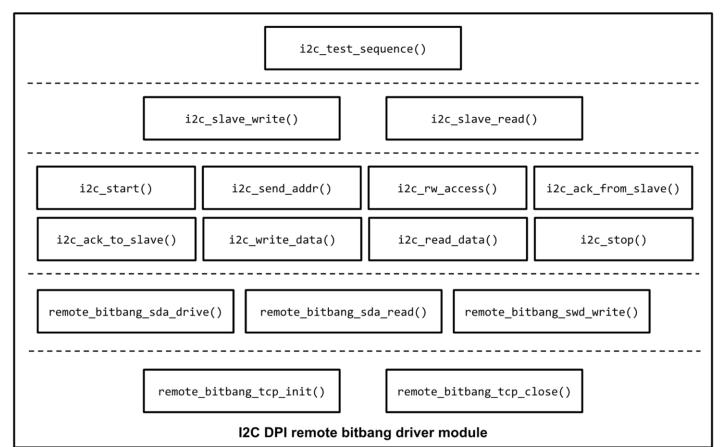

### The I2C DPI remote bitbang driver

- I2C test sequence

- I2C writes and reads

- Atomic I2C steps

- Bitbang protocol

- TCP connection handling

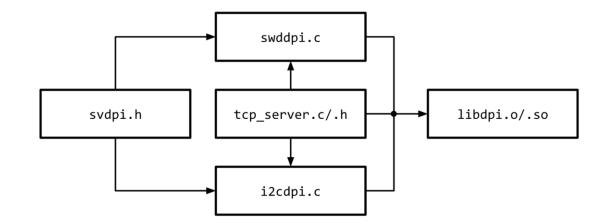

### Compilation of the DPI library

• File organization

Compilation script

1 #!/bin/sh

2 g++ -c -fPIC tcp\_server.c -o libdpi.o -include swddpi.c -include i2cdpi.c 3 g++ -shared -Wl,-soname,libdpi.so -o libdpi.so libdpi.o

### Testing results

| Xcelium              | <b>I2C Testing</b>           |  |

|----------------------|------------------------------|--|

| Simulation           | <b>Sequence</b>              |  |

| (SoC, SWD & I2C DPI) | (I2C remote bitbang via TCP) |  |

| <b>Telnet</b>        | <b>OpenOCD</b>               |  |

| <b>Client</b>        | <b>Server</b>                |  |

| (SWD via OpenOCD)    | (SWD remote bitbang via TCP) |  |

#### Testing results - Xcelium Simulation

xcelium> run

swd: Virtual SWD interface swd0 is listening on port 44853. Use OpenOCD and the following configuration to connect:

interface remote\_bitbang

remote\_bitbang\_host localhost

remote\_bitbang\_port 44853

I2C: Virtual I2C interface i2c0 is listening on port 44855.

i2c0: Accepted client connection I2C DPI: Remote disconnected. swd0: Accepted client connection

SYSTEMS INITIATIVE

### Testing results - OpenOCD Server (I)

S INITIATIVI

[user@linux openocd]\$ ./openocd Open On-Chip Debugger 0.11.0-rc2+dev-00003gb5563b75d-dirty (2022-09-02-17:21) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.h tml Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : Initializing remote bitbang driver Info : Connecting to localhost:44853 Info : remote bitbang driver initialized Info : This adapter doesn't support configurable speed

#### Testing results - OpenOCD Server (II)

Info : SWD DPIDR 0x0bc11477 Info : cortex m0p sim: hardware has 4 breakpoints, 2 watchpoints Info : starting gdb server for cortex\_m0p\_sim on 3333 Info : Listening on port 3333 for gdb connections Info : accepting 'telnet' connection on tcp/4444 target halted due to debug-request, current mode: Thread xPSR: 0x01000000 pc: 0x20000180 msp: 0x20000508

#### Testing results - Telnet Client

[user@linux openocd]\$ telnet localhost 4444 Connected to localhost. Escape character is '^]'. **Open On-Chip Debugger** > halt target halted due to debug-request, current mode: Thread xPSR: 0x01000000 pc: 0x20000180 msp: 0x20000508 > reg ==== arm v7m registers (0) r0 (/32): 0xe000e100 (13) sp (/32): 0x20000508 (14) lr (/32): 0x20000e9 (15) pc (/32): 0x20000180 (16) xPSR (/32): 0x01000000

SYSTEMS INITIATIVE

(17) msp (/32): 0x20000508

#### Testing results - I2C Testing Sequence

#### Conclusions

- Introduce a methodology for pre-FPGA debugging

- Design the architecture for HW/SW co-verification

- Maximize re-use of debug tools and test-cases

- Leverage software development expertise and resources

#### Questions