MUNICH, GERMANY DECEMBER 6 - 7, 2022

Using Open-Source EDA Tools in an Industrial Design Flow

<u>Daniela Sánchez Lopera</u>, Prajwal Kashyap, Nicolas Gerlin, Sven Wenzek, Wolfgang Ecker

### Outline

- Motivation

- Background Digital design flow

- What is OpenROAD?

- Our design flow

- Use Cases

- Results

- Summary & Conclusion

### Motivation: Open-Source Software for EDA?

#### **Advantages:**

- Extensibility

- Accessibility

- Scalability

#### For **industries** even more:

- Playground for:

- Students, researchers & inhouse trainings

- Suitable for:

- Experiments

- Collecting huge amount of data

- Analysing design and flow

- Enabling:

- Machine Learning (ML) applications

- Innovation

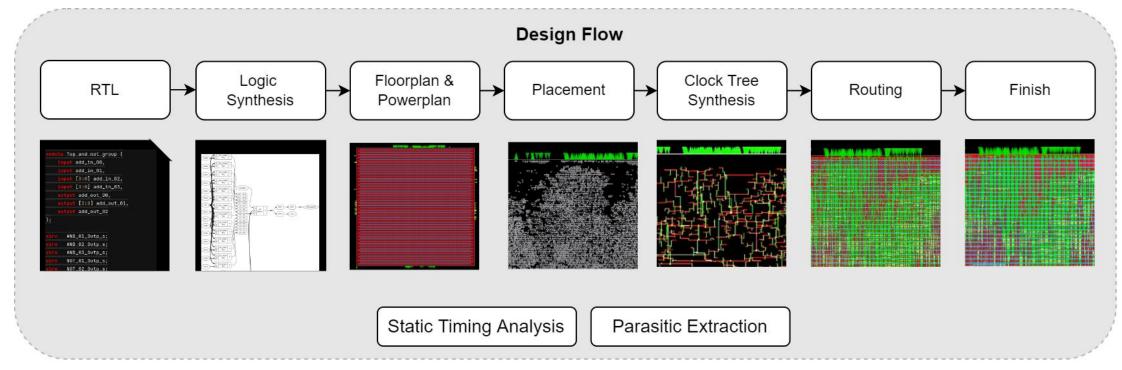

## Background Digital Design Flow

Images generated by OpenROAD using random die configuration and open-source PDK

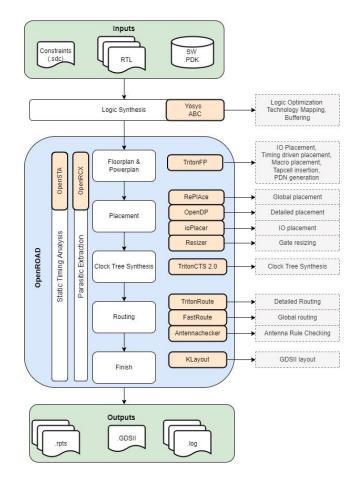

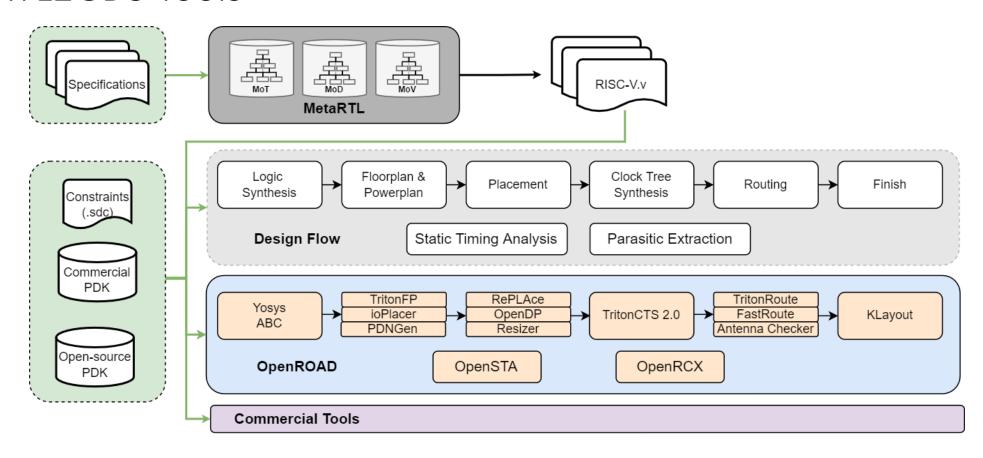

- RTL-to-GDSII framework for design exploration and physical design implementation

- Three existing "flow controllers"

- OpenROAD-flow-scripts1

- OpenLANE<sup>2</sup>

- Robust Design Flow (RDF)-2021<sup>3</sup>

<sup>&</sup>lt;sup>1</sup> https://github.com/The-OpenROAD-Project/OpenROAD-flow-scripts

<sup>&</sup>lt;sup>2</sup> https://github.com/The-OpenROAD-Project/OpenLane

<sup>3</sup> https://github.com/ieee-ceda-datc/datc-rdf

## What is OpenROAD? Related work

#### ML applications optimizing tool configurations:

- LSOracle<sup>4</sup>

- OpenABC-D<sup>5</sup>

- VeriGOOD-ML<sup>6</sup>

#### ML applications learning from OpenROAD outcomes:

- Congestion<sup>7</sup>

- Arrival times and slack<sup>8</sup>

<sup>&</sup>lt;sup>8</sup> Guo, Zizheng, et al. "A Timing Engine Inspired Graph Neural Network Model for Pre-Routing Slack Prediction", DAC 2022.

<sup>&</sup>lt;sup>4</sup>Neto, Walter, et al. "LSOracle: A logic synthesis framework driven by artificial intelligence", ICCAD 2019.

<sup>&</sup>lt;sup>5</sup> Chowdhury, Animesh Basak, et al. "OpenABC-D: A Large-Scale Dataset For Machine Learning Guided Integrated Circuit Synthesis", arXiv preprint:2110.11292 (2021).

<sup>&</sup>lt;sup>6</sup> Esmaeilzadeh, Hadi, et al. "VeriGOOD-ML: An Open-Source Flow for Automated ML Hardware Synthesis", ICCAD 2021.

<sup>&</sup>lt;sup>7</sup>Ghose, Amur, et al. "Generalizable Cross-Graph Embedding for GNN-based Congestion Prediction", ICCAD 2021

#### Challenges

Lück, C., Sánchez Lopera, D., Wenzek, S., & Ecker, W. Industrial Experience with Open-Source EDA Tools. MLCAD 2022

#### Adaptations on source code to cope with:

- Infrastructure restrictions: No super user, no Docker

- Proprietary PDKs

- Parallelization on compute farm

#### Envisioned use-cases

Lück, C., Sánchez Lopera, D., Wenzek, S., & Ecker, W. Industrial Experience with Open-Source EDA Tools. MLCAD 2022

Design Space Exploration

- Data generation for ML models

- Design metric prediction

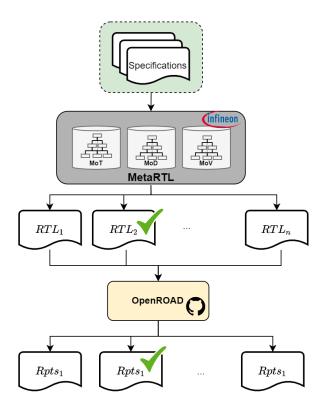

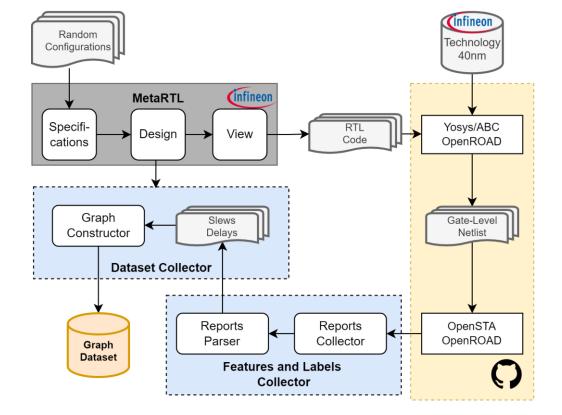

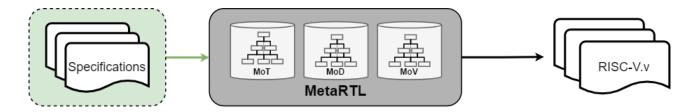

Sánchez Lopera D., Ecker W., Applying GNNs to Timing Estimation at RTL, ICCAD 2022. **MetaRTL**: Ecker, W., and Schreiner, J.. "Introducing Model-of-Things (MoT) and Model-of-Design (MoD) for simpler and more efficient hardware generators. *VLSI-SoC 2016*.

#### Envisioned use-cases

Lück, C., Sánchez Lopera, D., Wenzek, S., & Ecker, W. Industrial Experience with Open-Source EDA Tools. MLCAD 2022

- Design Space Exploration

- Data generation for ML models

- Design metric prediction

Sánchez Lopera D., Ecker W., Applying GNNs to Timing Estimation at RTL, ICCAD 2022. **MetaRTL**: Ecker, W., and Schreiner, J.. "Introducing Model-of-Things (MoT) and Model-of-Design (MoD) for simpler and more efficient hardware generators. *VLSI-SoC 2016*.

#### Envisioned use-cases

Lück, C., Sánchez Lopera, D., Wenzek, S., & Ecker, W. Industrial Experience with Open-Source EDA Tools. MLCAD 2022

Configurations

**Dataset Collector**

Graph

Parser

Design Space Exploration

• D

How good are our ground truth labels coming from open-source tools?

Sánchez Lopera D., Ecker W., Applying GNNs to Timing Estimation at RTL, ICCAD 2022. **MetaRTL**: Ecker, W., and Schreiner, J.. "Introducing Model-of-Things (MoT) and Model-of-Design (MoD) for simpler and more efficient hardware generators. *VLSI-SoC 2016*.

-echnoloa\

sys/ABC

enROAD

OpenSTA

OpenROAD

Reports

Collector

**Features and Labels**

## OpenROAD vs Commercial Tools

| Feature                  | Open-source | Commercial |

|--------------------------|-------------|------------|

| Extensibility            | x           |            |

| Accesibility             | x           |            |

| Scalability              | x           |            |

| Customer<br>Support      |             | X          |

| Reliability              |             | x          |

| Technology & Engineering |             | X          |

| Workforce development    | X           | X          |

A Mixed Open-Source and Proprietary EDA Commons for Education and Prototyping Invited Paper. Andrew B. Kahng. ICCAD 2022

### OpenROAD vs Commercial Tools

| Feature                  | Open-source | Commercial |

|--------------------------|-------------|------------|

| Extensibility            | x           |            |

| Accesibility             | x           |            |

| Scalability              | ×           |            |

| Customer<br>Support      |             | X          |

| Reliability              |             | X          |

| Technology & Engineering |             | X          |

| Workforce<br>development | X           | Х          |

Open and free software

Years of experience and billions of investments

A Mixed Open-Source and Proprietary EDA Commons for Education and Prototyping Invited Paper. Andrew B. Kahng. ICCAD 2022

## OpenROAD vs Commercial Tools

| Feature                  | Open-source | Commercial |                                                               |

|--------------------------|-------------|------------|---------------------------------------------------------------|

| Extensibility            | x           |            |                                                               |

| Accesibility             | Х           |            | Open and free software                                        |

| Q:                       | 1: But hov  | v do they  | compare w.r.t PPA results?                                    |

| Technology & Engineering |             | X          |                                                               |

| Workforce                | X           | Х          | A Mixed Open-Source and Proprietary EDA Commons for Education |

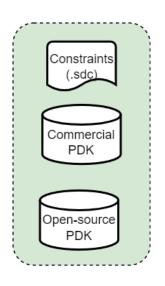

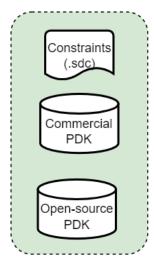

# Our Design Flow (1) Inputs

# Our Design Flow (1) Inputs

| PDK   | Туре        | # Lines Lib. File | # Standard Cells |

|-------|-------------|-------------------|------------------|

| 40nm  | Proprietary | 14678.9 K         | 852              |

| 130nm | Open-source | 333.5 K           | 753              |

\*Open-source: <a href="https://skywater-pdk.readthedocs.io/en/main/">https://skywater-pdk.readthedocs.io/en/main/</a>

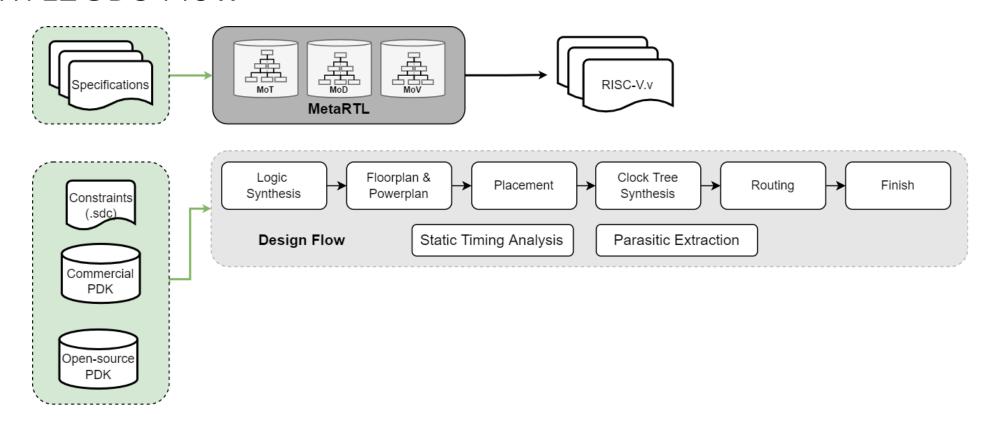

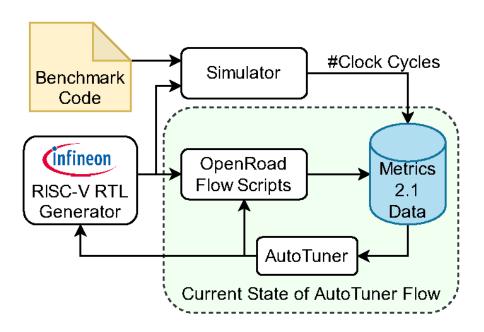

## Our Design Flow (2)

#### RTL Generation

#### Advantages of using MetaRTL on top of OpenROAD:

- Using one programming language for hardware generation, synthesis flow and machine learning<sup>12</sup>

- Generation of properties for formal verification<sup>13</sup>

- <sup>12</sup> K. Devarajegowda, et al., "Python based framework for HDSLs with an underlying formal semantics". ICCAD 2017

- <sup>13</sup> K. Devarajegowda, et al., "How to Keep 4-Eyes Principle in a Design and Property Generation Flow", MBMV 2019

# Our Design Flow (3) RTL2GDS Flow

# Our Design Flow (4) RTL2GDS Tools

### Generated Use-Cases RISC-V - RV32IMCX

| Designs             | Extension<br>Units                       | # Lines of<br>Code | # Components | # Input<br>bits | # Output<br>bits |

|---------------------|------------------------------------------|--------------------|--------------|-----------------|------------------|

| RISC-V <sup>1</sup> | CRC, PFC                                 | 16496              | 810          | 71              | 157              |

| RISC-V <sup>2</sup> | Exception                                | 28377              | 1430         | 170             | 164              |

| RISC-V <sup>3</sup> | MAC                                      | 39487              | 2271         | 171             | 164              |

| RISC-V <sup>4</sup> | Event<br>Counters                        | 16391              | 844          | 70              | 157              |

| RISC-V <sup>5</sup> | CRC, PFC, MAC, Event Counters, Exception | 42121              | 2403         | 170             | 165              |

# Generated Use-Cases RISC-V

| Designs             | Extension<br>Units                                   | # Lines of<br>Code | # Components | # Input<br>bits | # Output<br>bits | Complexity<br>Flag |

|---------------------|------------------------------------------------------|--------------------|--------------|-----------------|------------------|--------------------|

| RISC-V <sup>1</sup> | CRC, PFC                                             | 16496              | 810          | 71              | 157              | +                  |

| RISC-V <sup>2</sup> | Exception                                            | 28377              | 1430         | 170             | 164              | ++                 |

| RISC-V <sup>3</sup> | MAC                                                  | 39487              | 2271         | 171             | 164              | ++                 |

| RISC-V <sup>4</sup> | Event<br>Counters                                    | 16391              | 844          | 70              | 157              | +                  |

| RISC-V <sup>5</sup> | CRC, PFC,<br>MAC,<br>Event<br>Counters,<br>Exception | 42121              | 2403         | 170             | 165              | +++                |

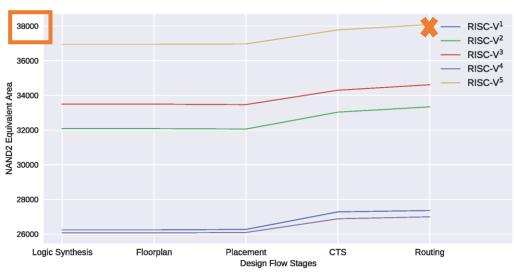

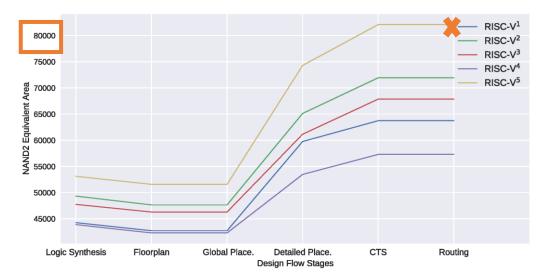

## Post Routing Results

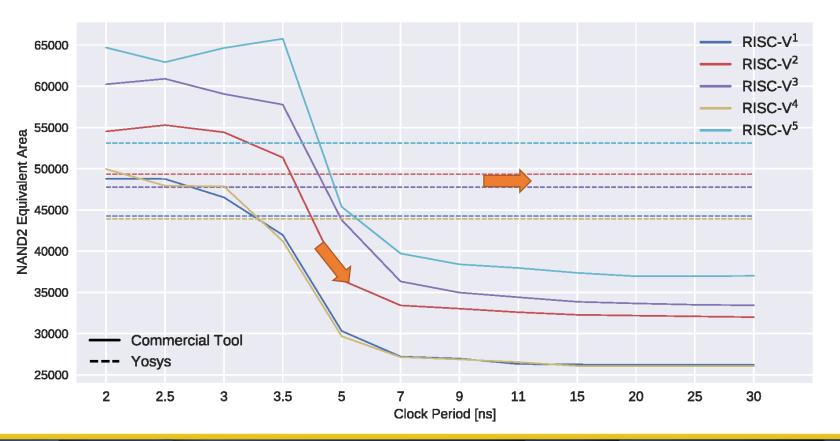

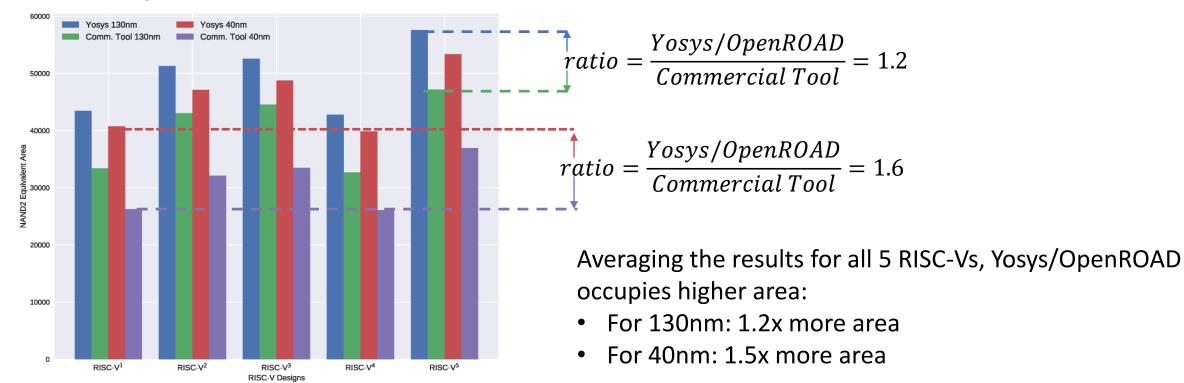

# Results (1) Post Routing – Area

#### **Commercial Tool**

$$Avg.ratio = \frac{1}{5} \sum \frac{Yosys/OpenROAD}{Commercial\ Tool}\ \forall\ RISC-V$$

#### **OpenROAD**

# Results (1) Post Routing – Area

#### **Commercial Tool**

#### **OpenROAD**

Averaging the results for all 5 RISC-Vs, OpenROAD occupies more area:

- NAND2 Eq. Area: 2.1x more area

- # Standard Cells: 2.4x more cells

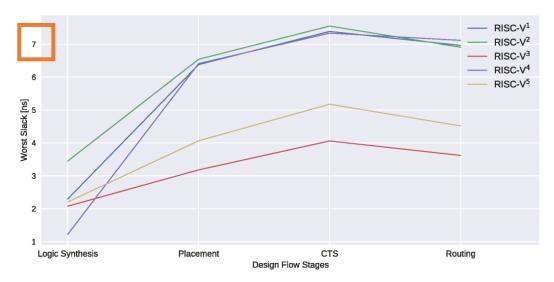

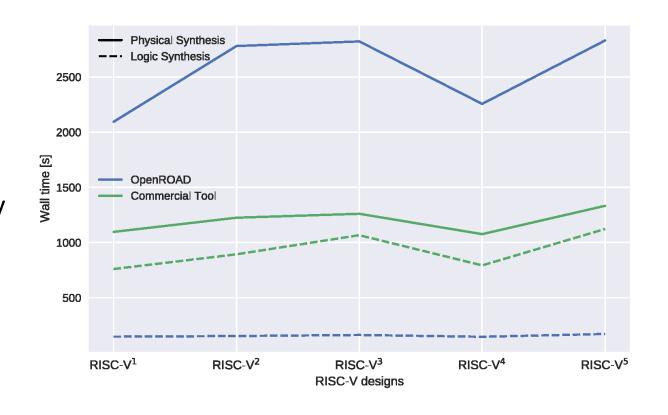

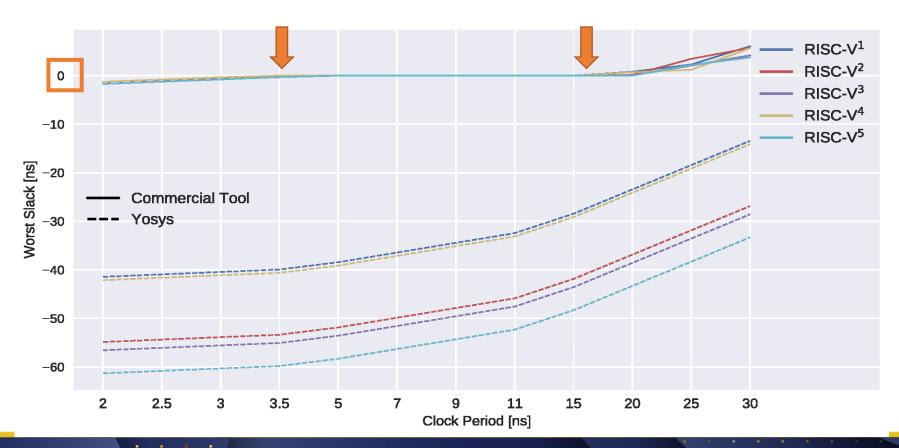

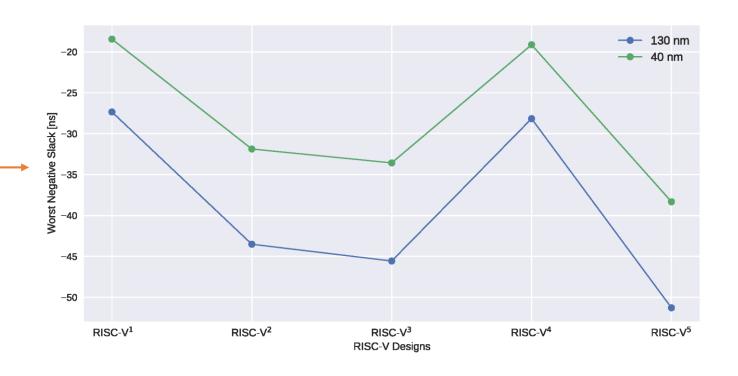

# Results (2) Post Routing – Worst Slack

#### **Commercial Tool**

#### **OpenROAD**

Averaging the results for all 5 RISC-Vs, OpenROAD worst slack after routing is:

• Critical path worst slack: 2.9x higher

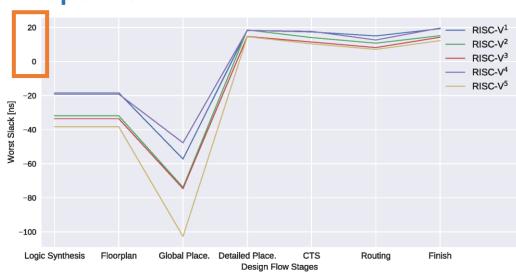

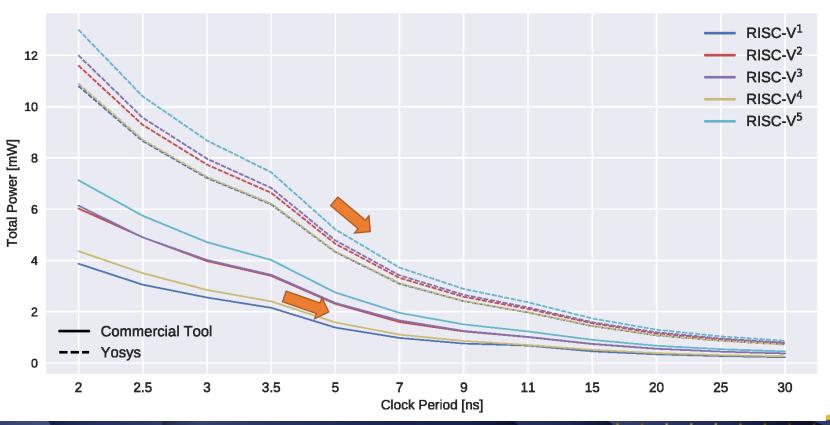

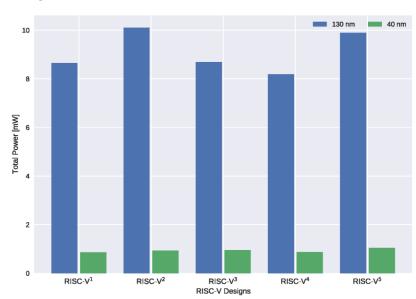

# Results (3) Post Routing – Total Power

#### **Commercial Tool**

#### OpenROAD

Averaging the results for all 5 RISC-Vs, OpenROAD consumes more power:

• Total power: 2.7x more

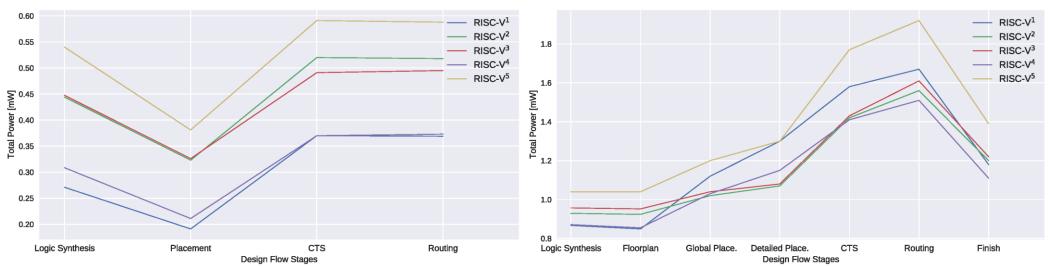

### Runtimes

# Results (4) Wall times – Routing

- Under fair conditions:

- No multi-threading

- Same CPU:

Linux CPU Intel<sup>®</sup> Xeon<sup>®</sup> Gold 6248R at 3.00 GHz and 80 GiB system memory

## Sweeping clock

### Results (5) Sweeping clock - Logic Synthesis - Area

OpenROAD keeps area constant while varying clock period

## Results (6)

#### Sweeping clock - Logic Synthesis - Power

Higher clock, less total power

# Results (7) Sweeping clock - Logic Synthesis - Worst Slack

OpenROAD needs very high clock periods for meeting timing requirements after logic synthesis

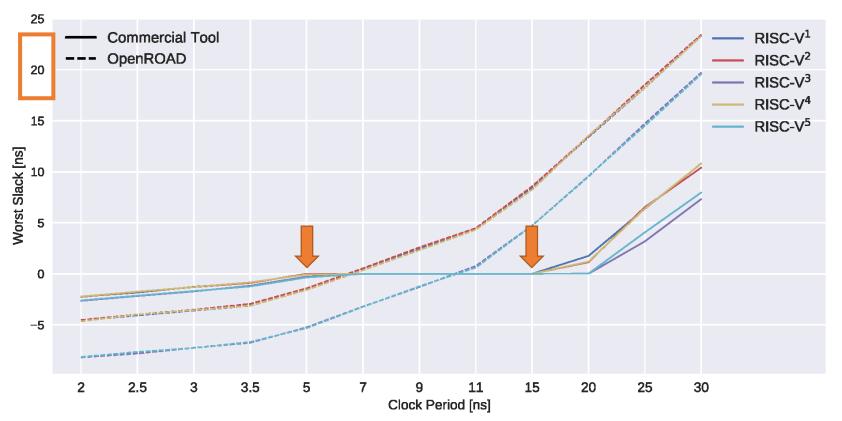

# Results (8) Sweeping clock – Routing - Worst Slack

OpenROAD needs higher clocks for meeting timing requirements after routing

### Summary

Q1: But how do they compare w.r.t PPA results?

## Summary

| Stage                | Ratio [Open-Source Tool/Commercial<br>Tool] |                     |     |                |

|----------------------|---------------------------------------------|---------------------|-----|----------------|

|                      | NAND2<br>Eq. Area                           | # Standard<br>Cells | WS  | Total<br>Power |

| Post logic synthesis | 1.5                                         | 1.8                 | <0  | 2.4            |

| Post routing         | 2.1                                         | 2.4                 | 2.9 | 2.7            |

Avg = 2.5x

<sup>\*</sup> For PDK 40nm

<sup>\*</sup> For flatten synthesis

<sup>\*</sup> For clock 25ns

### Summary

- \* For flatten synthesis

- \* For clock 25ns

#### Conclusion

- We outline our industrial flow from initial specifications to GDS using different RISC-Vs as use cases.

- Averaging the reported post-routing PPA factors for a 25 ns clock period, the commercial tool outperforms OpenROAD by a factor of 2.52x.

- The **commercial tool is faster** without any parallelization, and it **meets timing constraints for lower clock periods** than OpenROAD.

### Conclusion

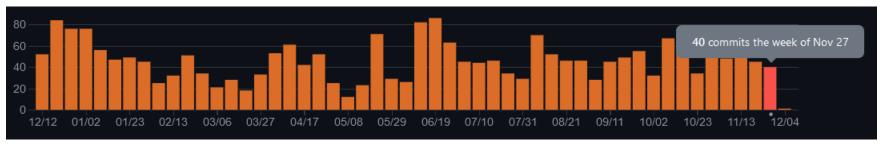

But OpenROAD is evolving fast: more than 1.4K commits in 2022 and 19 active pull requests<sup>14</sup>.

https://github.com/The-OpenROAD-Project/OpenROAD/graphs/commit-activity. Visited on Dec. 05, 2022.

#### **Future:**

- Commercial and open-source EDA working together to enable research and progress on the field

- Analyze generated output of commercial tools using OpenROAD and vice versa

### Questions?

Thank you!

### What is OpenROAD? Related work

### OpenROAD published papers describe some attempts of benchmarking:

- Number of commits, citations, community engagement<sup>9</sup>

- Comparing results of their AutoTuner with two different SkyWater libraries<sup>10</sup>

- Comparing the OpenROAD placer, OpenSTA and OpenRCX w.r.t commercial tools<sup>11</sup>

<sup>&</sup>lt;sup>9</sup> Jung, Jinwook, et al. "METRICS2. 1 and Flow Tuning in the IEEE CEDA Robust Design Flow and OpenROAD ICCAD Special Session Paper", ICCAD 2021. <sup>10</sup> A. B. Kahng, "Looking into the Mirror of Open Source: Invited Paper", *ICCAD 2019*

<sup>&</sup>lt;sup>11</sup> A. B. Kahng and T. Spyrou, "The OpenROAD Project: Unleashing Hardware Innovation", GOMAC 2021

### What is OpenROAD?

Envisioned use-cases

• Design Space Exploration (DSE)

Lück, C., Sánchez Lopera, D., Wenzek, S., & Ecker, W. Industrial Experience with Open-Source EDA Tools. MLCAD 2022

### Post Logic Synthesis Results

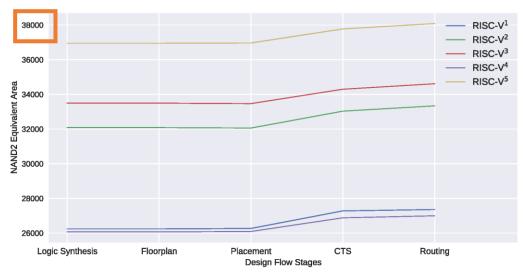

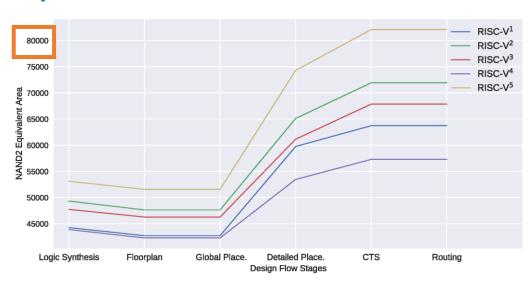

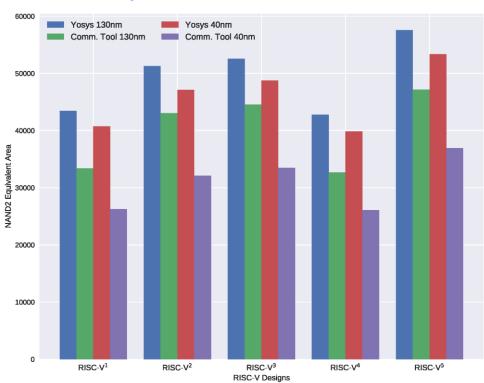

# Results (1) Post Logic Synthesis – Area

#### **NAND2 Equivalent Area**

### Results (1) Post Logic Synthesis – Area

#### **NAND2 Equivalent Area**

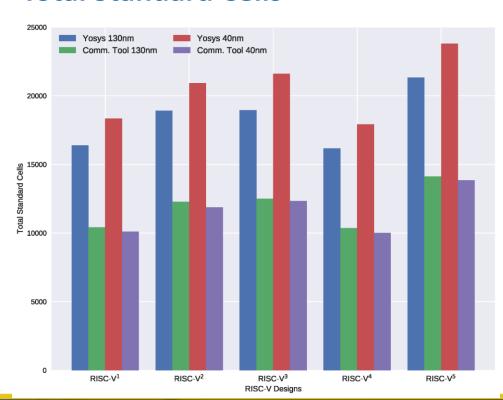

### Results (2) Post Logic Synthesis – Area

#### **Total Standard Cells**

Averaging the results for all 5 RISC-Vs, Yosys/OpenROAD occupies higher area:

For 130nm: 1.5x more cells

For 40nm: 1.8x more cells

# Results (3) Post Logic Synthesis – Worst Negative Slack (WNS)

For both PDKs: 130nm and 40nm

| Synthesis<br>Type          | Commercial<br>Tool | OpenROAD |

|----------------------------|--------------------|----------|

| Flatten                    | 0                  | <0       |

| Non-flatten (hierarchical) | 0                  | 0        |

# Results (3) Post Logic Synthesis – Worst Negative Slack (WNS)

#### For both PDKs: 130nm and 40nm

| Synthesis<br>Type          | Commercial<br>Tool | OpenROAD |

|----------------------------|--------------------|----------|

| Flatten                    | 0                  | <0       |

| Non-flatten (hierarchical) | 0                  | 0        |

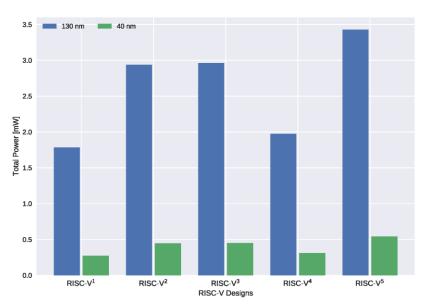

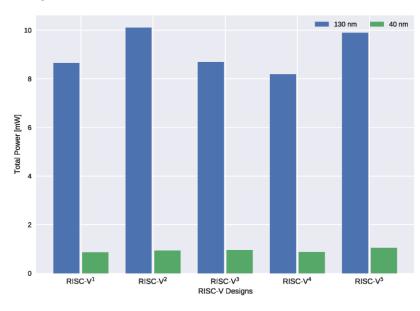

# Results (4) Post Logic Synthesis – Total Power

#### **Commercial Tool**

#### **OpenROAD**

### Results (4) Post Logic Synthesis – Total Power

#### **Commercial Tool**

# 3.5 130 nm 40 nm 3.0 2.5 1.0 0.5 RISC-V<sup>1</sup> RISC-V<sup>2</sup> RISC-V<sup>3</sup> RISC-V<sup>4</sup> RISC-V<sup>5</sup>

#### **OpenROAD**

Averaging the results for all 5 RISC-Vs, Yosys/OpenROAD consumes more power:

- For 130nm: 3.8x more power

- For 40nm: 2.4x more power

### Results (4) Post Logic Synthesis – Total Power

Averaging the results for all 5 RISC-Vs, Yosys/OpenROAD consumes more power:

- For 130nm: 3.8x more power

- For 40nm: 2.4x more power