> MUNICH, GERMANY DECEMBER 6 - 7, 2022

# A NOVEL APPROACH TO HARDWARE CONTROLLED POWER AWARE VERIFICATION WITH OPTIMISED POWER CONSUMPTION TECHNIQUES AT SOC

Eldin Ben Jacob, Harshal Kothari, Sriram Kazhiyur Sounderrajan, Somasunder Kattepura Sreenath

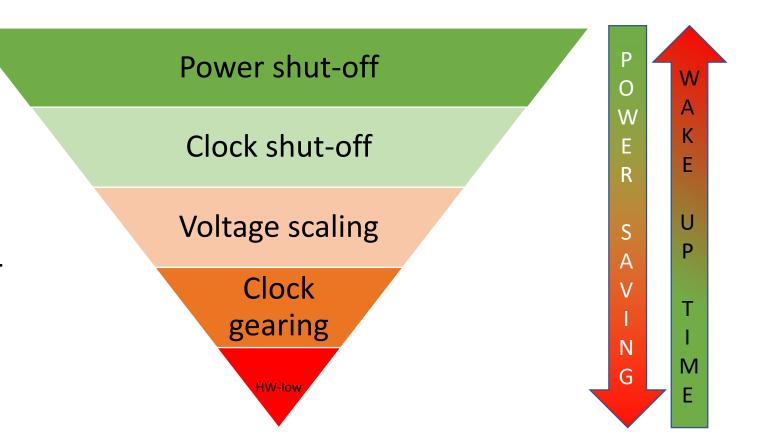

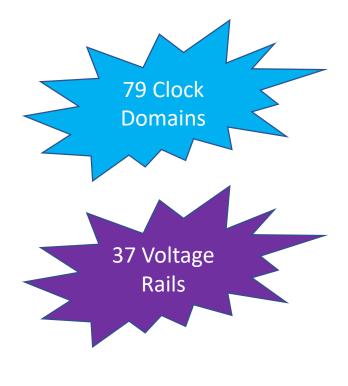

# **Power Saving Techniques**

- Power shut off

- Clock shut off

- Voltage scaling

- Clock gearing

- Additional techniques

- Level shifter

- Retention

- Isolation

### PMIC Model

Lowest

Power

NOC A SI MAKIW MASTER POC\_BLK\_N ROCN PDC 2 1.0.0 -----Slave PDC 1.0 Slave BLK 2 BLK N

SYSTEMS INITIATIVE

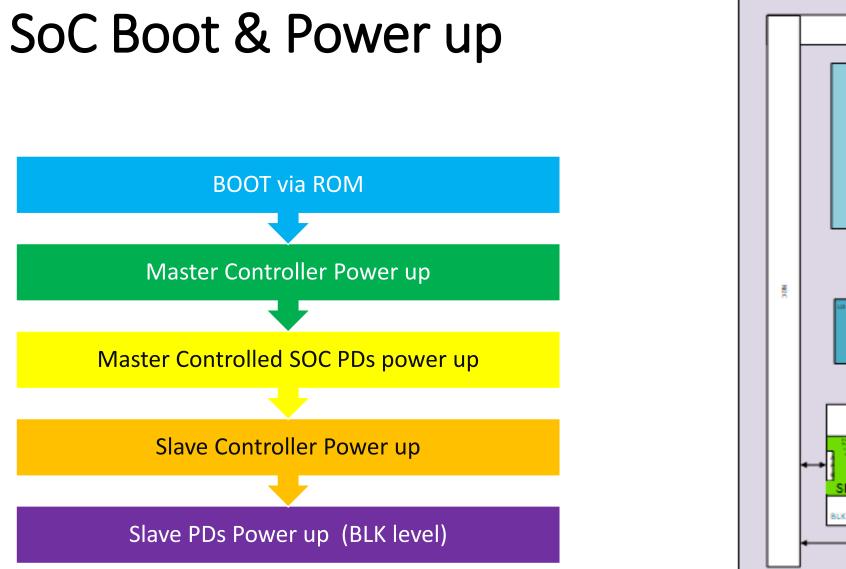

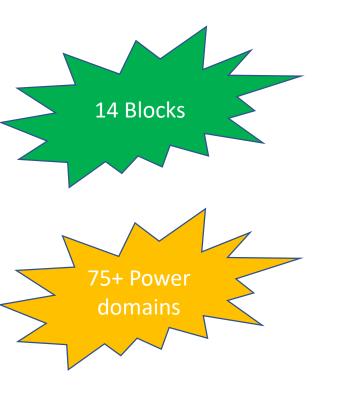

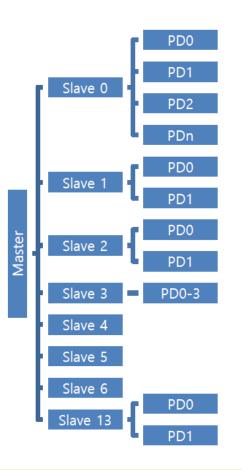

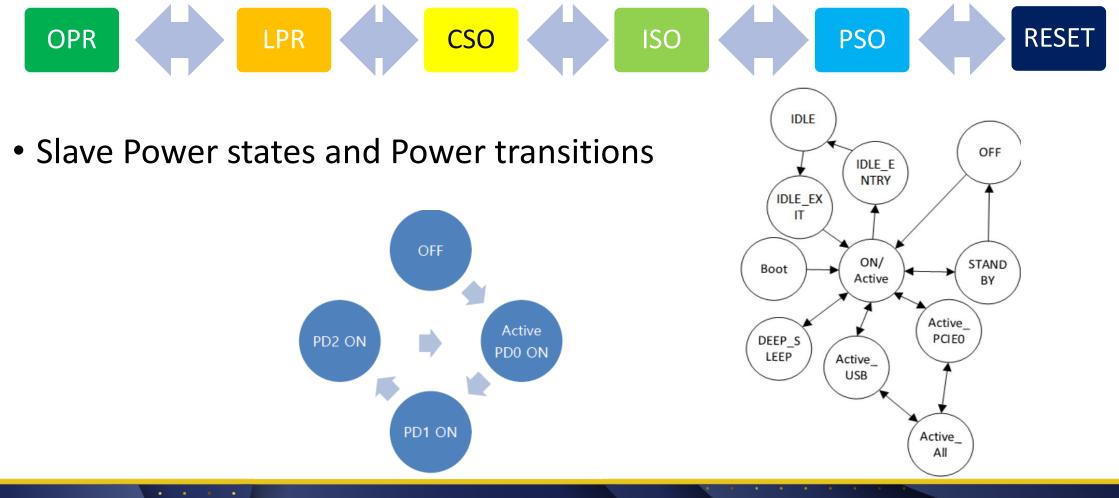

## Master Slave Architecture

SYSTEMS INITIATIVE

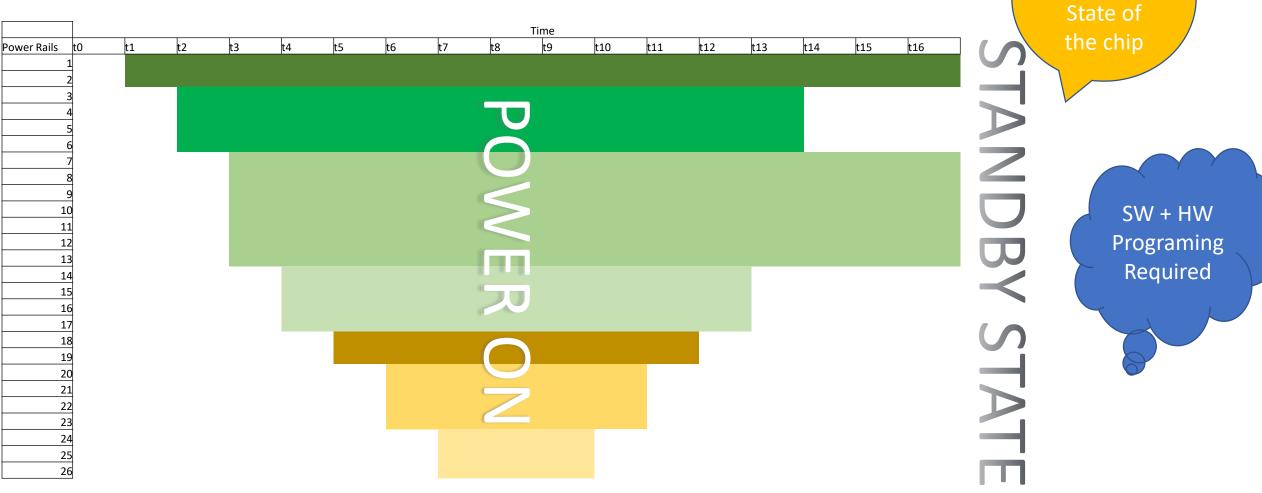

## **Power Transition FSM**

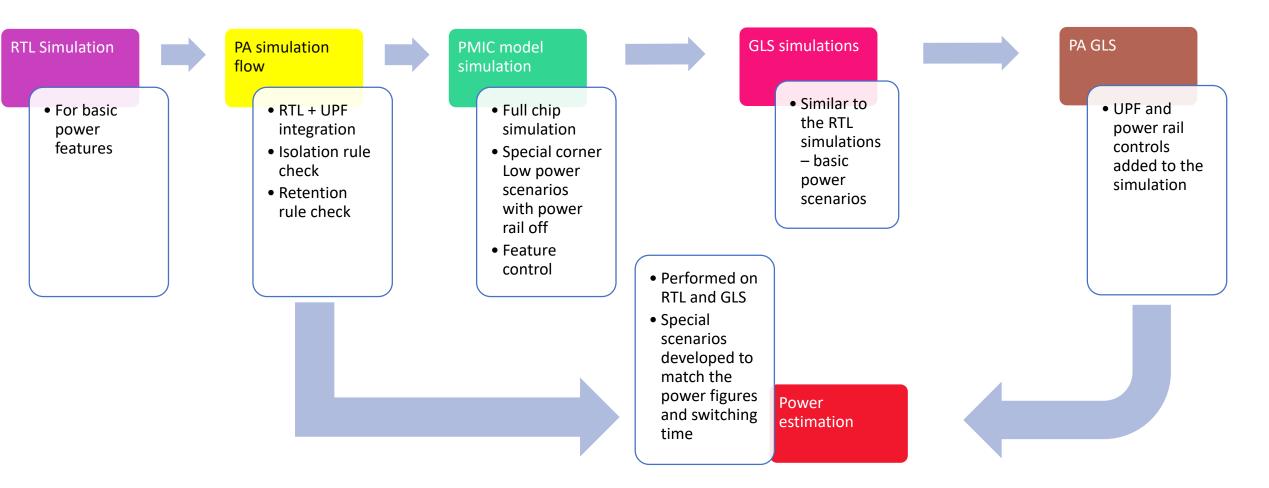

# Verification flow

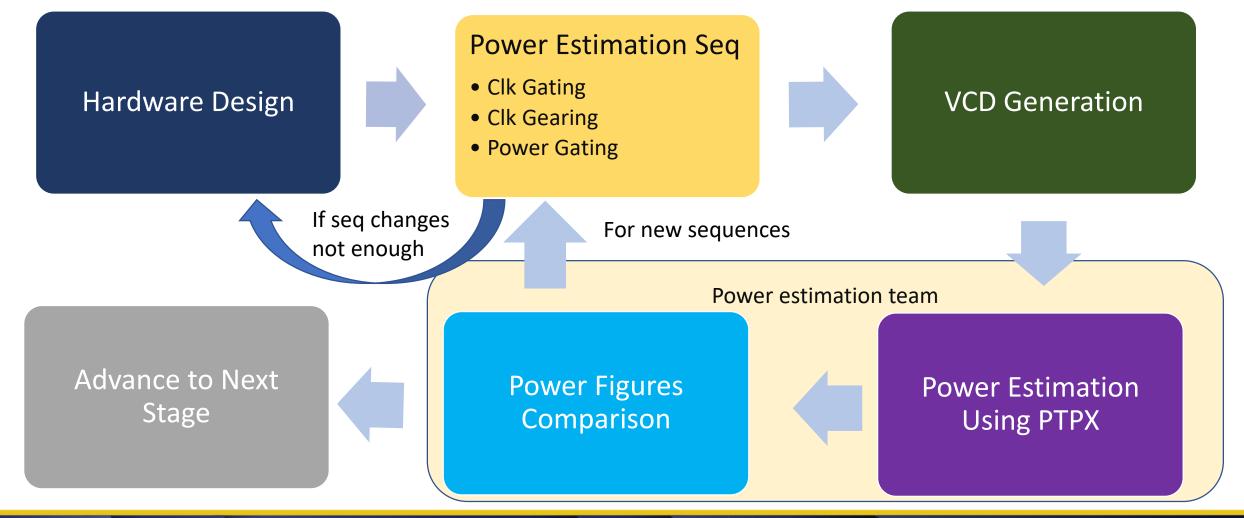

#### Power estimation process

|                   |            |                  |                                   | Chip Level Analysis                          |                                                                                                    |                                                                                                                                      |                                                                                                                                                                                                       |  |

|-------------------|------------|------------------|-----------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Doculto           |            |                  | HW controlled                     | Software Controlled                          |                                                                                                    |                                                                                                                                      |                                                                                                                                                                                                       |  |

| Results           |            |                  |                                   |                                              |                                                                                                    |                                                                                                                                      |                                                                                                                                                                                                       |  |

|                   |            |                  | Master Level Power                | BLK level power                              | Master Level Clock                                                                                 | IP level Clock                                                                                                                       | Power                                                                                                                                                                                                 |  |

|                   |            | Scenario         | gating                            | gating                                       | gating                                                                                             | gating                                                                                                                               | Saving                                                                                                                                                                                                |  |

|                   |            | A                |                                   |                                              |                                                                                                    |                                                                                                                                      | 0%                                                                                                                                                                                                    |  |

|                   |            | В                |                                   |                                              |                                                                                                    | Yes                                                                                                                                  | 42%                                                                                                                                                                                                   |  |

|                   |            | С                |                                   | Yes                                          |                                                                                                    |                                                                                                                                      | <mark>68%</mark>                                                                                                                                                                                      |  |

|                   |            | D                |                                   |                                              | Yes                                                                                                |                                                                                                                                      | 52%                                                                                                                                                                                                   |  |

|                   |            | E                | Yes                               | Yes                                          |                                                                                                    |                                                                                                                                      | 83%                                                                                                                                                                                                   |  |

| <b>IDLE POWER</b> | POWER      |                  |                                   |                                              |                                                                                                    |                                                                                                                                      |                                                                                                                                                                                                       |  |

|                   | IDLE POWER | IDLE POWER POWER | Scenario<br>A<br>B<br>C<br>D<br>E | ScenarioMaster Level Power<br>gatingABCDEYes | HW controlledHW controlledMaster Level PowerBLK level power<br>gatingScenariogatingAIBICIDIEYesYes | HW controlledSoftware ControlledMaster Level PowerBLK level powerMaster Level ClockgatinggatinggatingAAAABGAACSenarioYesDIYesEYesYes | HW controlledSoftware ControlledMaster Level PowerBLK level power<br>gatingMaster Level Clock<br>gatingIP level Clock<br>gatingAAAAAABGanceAAAACSecondYesAAADIndextYesIndextIndextEYesYesIndextIndext |  |

| LEAK POWER | <b>IDLE POWER</b> | POWER      |  |  |

|------------|-------------------|------------|--|--|

|            |                   | GATED IDLE |  |  |

| 40MW       | 5.99 <b>M</b> W   | 0.58MW     |  |  |

|   | Block Level Analysis |                           |                           |                           |                           |                           |                 |

|---|----------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------|

|   | System Register, NOC | МСИ                       | Camera controller         | Image Processor           | Display controller        | DMA                       | Power<br>Saving |

| A | FC, NOP (100Mhz)     | FC,NOP (800Mhz)           | FC,NOP (800 Mhz)          | FC,NOP (800Mhz)           | FC,NOP (800Mhz)           | FC,NOP (800Mhz)           | 0%              |

| В | FC, NOP (100Mhz)     | FC,NOP (800Mhz)           | Clock gearing<br>(100Mhz) | Clock gearing<br>(100Mhz) | Clock gearing<br>(100Mhz) | Clock gearing<br>(100Mhz) | 10%             |

| С | FC, NOP (100Mhz)     | FC,NOP (800Mhz)           | FC,NOP (800Mhz)           | FC,NOP (800Mhz)           | Clock Gating              | FC,NOP (800Mhz)           | 25%             |

| D | FC, NOP (100Mhz)     | FC,NOP (800Mhz)           | Clock Gating              | Clock gating              | Clock Gating              | Clock Gating              | 40%             |

| E |                      | Clock Gearing<br>(100Mhz) | Clock Gating              | Clock gating              | Power Gating              | Clock Gating              | 58%             |

| F | FC, NOP (100Mhz)     | FC,NOP (800Mhz)           | Power Gating              | Power Gating              | Power Gating              | Power Gating              | 68%             |

| G | FC, NOP (100Mhz)     | Clock Gated               | Power Gating              | Power Gating              | Power Gating              | Power Gating              | 79%             |

| Н | Clock Gated          | Power Gated               | Power Gating              | Power Gating              | Power Gating              | Power Gating              | 91%             |

### Conclusion

- HW triggered Power down 40cycles

- SW Triggered Power down 200 cycles

- Aggressive power saving techniques -> time penalty -> selection based on the real time scenario

- Master slave power controller architecture 40% improvement

- The power estimation RTL and GLS meet low power req in real silicon

- DV sequences

- Lowest power state determination

- Programing Sequences

- Faster turn around time

> MUNICH, GERMANY DECEMBER 6 - 7, 2022

QUESTIONS?

1 AL 2 4 - 1 AL 4