DESIGN AND VERIFICATION™ **CONFERENCE AND EXHIBITION**

MUNICH, GERMANY DECEMBER 6 - 7, <u>2022</u>

## Automated Creation of Reusable Generators for Analog IC Design with the Intelligent IP Method

Uwe Eichler, Benjamin Prautsch, Torsten Reich Fraunhofer IIS/EAS

SPONSORED BY THE

IIS

#### Agenda

- Motivation

- What is a generator?

- Layout templates

- Automatic creation of generators

- Generator and Simulation Results

- Summary / Outlook / References

# Motivation (for analog layout automation)

- Digital IC design:

- Circuit and layout synthesis based on an HDL description and standard cells is state of art

- Analog IC design:

- Dominated by manual work, without programmatic entry, soft IP, or layout synthesis

- Reduced efficiency and design safety

- Few automation approaches, not well established

# Analog IC Design Automation Approaches

- Synthesis

- search for feasible / optimal P & R solution in very large parameter space

- requires definition of many constraints due to complexity

- $\rightarrow$  handle complexity

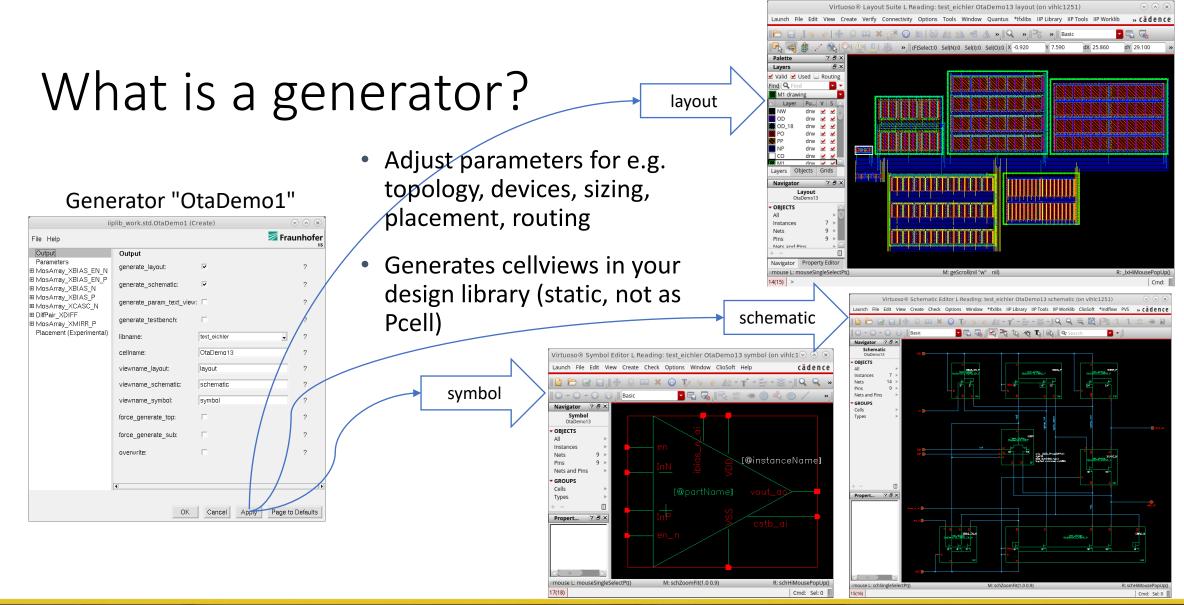

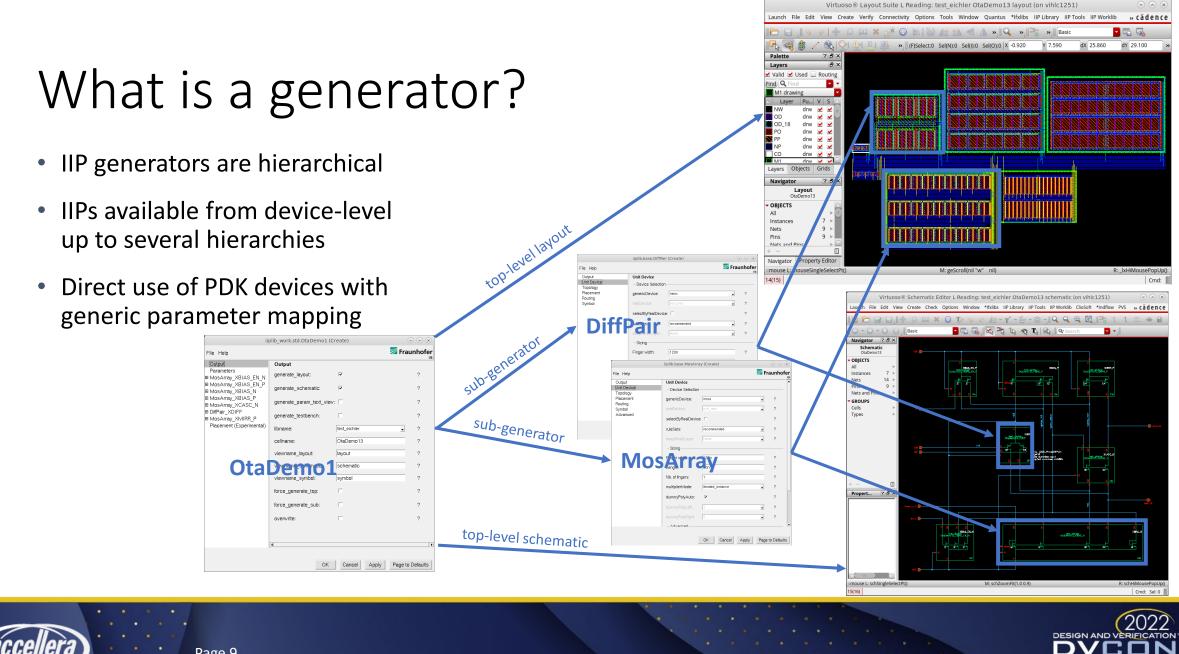

- Generators

- Programmatic circuit description, creates design data

- Parameters to control topology, sizing, placement, routing

- Circuit-class-specific, deterministic, can be organized in libraries

- $\rightarrow$  reduce complexity

## Analog IC Design Automation Approaches

- Generators + Optimization

- Generators for basic building blocks (array arrangements of unit devices, well scalable layouts, easy to implement as generator)

- Need to arrange such blocks in hierarchical designs with optimized area and routing

- $\rightarrow$  use optimization to adjust generator parameters

- $\rightarrow$  enables layout-aware sizing and optimization

## What is a generator?

- "Procedural generators are often proposed for analog IC design automation. They promise to encapsulate designer knowledge and intellectual property (IP) data in a deterministic and reusable way." [this paper]

- Known generator approaches:

- Cadence PCell / Synopsys PyCell [1, 2]

- IPGen 1Stone (not available anymore) [3]

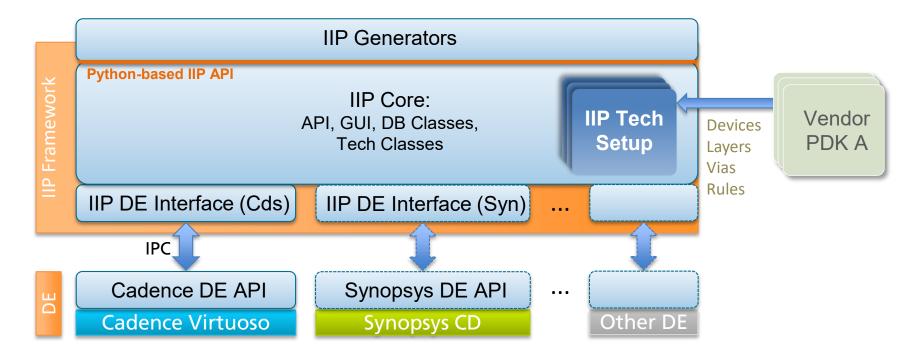

- Fraunhofer IIS/EAS Intelligent IP ("IIP", this publication)

- Berkeley Analog Generator [4]

- Some more, mostly academic approaches

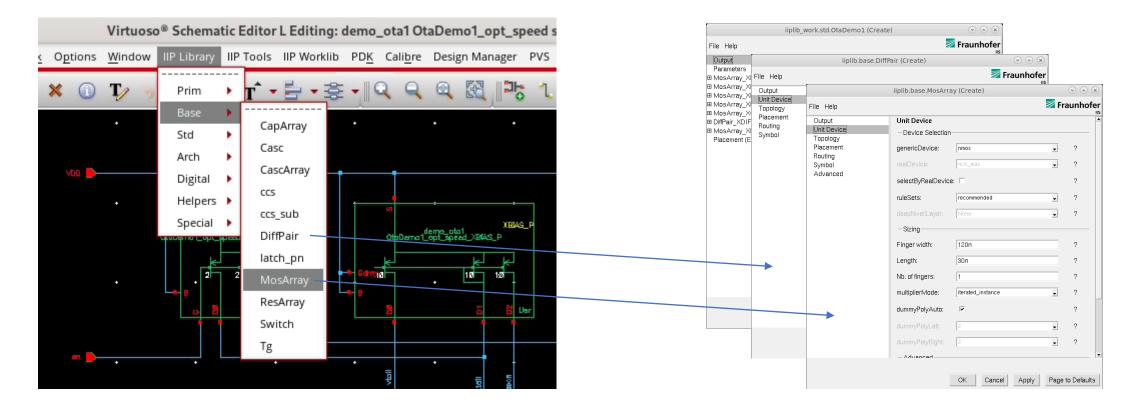

# What is a generator?

Page 7

SYSTEMS INITIATIVE

- specific for a type of circuits

- also called an IIP (a kind of analog soft IP)

- integrates as a library of IIPs in the design environment

SYSTEMS INITIATIVE

SYSTEMS INITIATIVE

#### What is a generator?

• implemented using a generic circuit description language based on Python

# Motivation (for automated generator creation)

- How to create and integrate generators efficiently?

→ Trade-off: implementation effort, reusability and acceptance

- Who should implement and maintain generator IP?

→ Design team / CAD department / IP vendor / EDA vendor?

→ Circuit IP and technology data often confidential

- Which interfaces and standards should be used?

- → Programming language, Tool and PDK interfaces, Interoperability?

#### $\rightarrow$ Automate also the generator implementation

# Generator-based design of hierarchical circuits

- Use generators up to base-level only

- $\rightarrow$  Already improves productivity

- $\rightarrow$  Limited reuse due to manual effort for upper hierarchies

- Custom, circuit-specific generator implementation

- $\rightarrow$  Large implementation effort for flexible, area-efficient layout

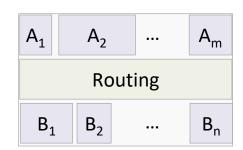

- Generator using abstract layout templates

- ightarrow templates define relative positions of sub-block instances and interconnects

- $\rightarrow$  usually regular arrangements, reusable across hierarchies

- $\rightarrow$  fast generator implementation as P & R code encapsulated by template API

• Page 12

#### Template-based layout generation

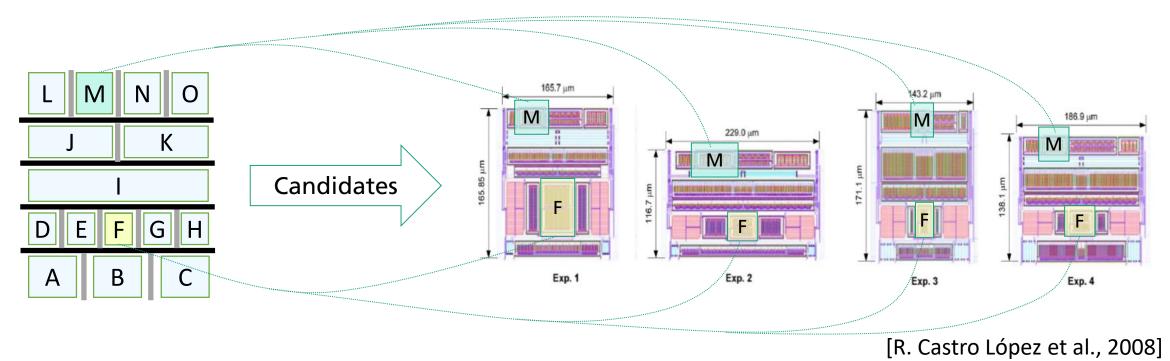

• Not a new approach: [5]

## Template-based layout generation

- Template P&R algorithms were embedded into IIP

- Template properties accessible through user interface

Template "Street"

| ≡<br>File Help                                                                                                                                                                  | iiplib_work.std.Ota[ | Demo1 (Create) | _ □ ×    |          |         |   |              |       |                  |   |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|----------|----------|---------|---|--------------|-------|------------------|---|--|

| Output                                                                                                                                                                          | Placement (Experimen | ntal)          | <u> </u> |          |         |   |              |       |                  |   |  |

| Parameters                                                                                                                                                                      | placeMethod:         | street         | • ?      |          | 2       | 6 | 4            | 7     |                  |   |  |

| MosArray_XBIA5_EN_P     MosArray_XBIA5_EN_P     MosArray_XBIA5_N     MosArray_XBIA5_P     MosArray_XCASC_N     DiffPair_XDIFF     MosArray_XMIRR_P     Placement (Experimental) | nRows:               | 2              | ?        |          |         |   |              |       |                  |   |  |

|                                                                                                                                                                                 | placeStyle:          | p-n            | • ?      |          | Routing |   |              |       |                  |   |  |

|                                                                                                                                                                                 |                      |                | ?        |          |         |   |              |       |                  |   |  |

|                                                                                                                                                                                 | initWidth:           | 10             | ?        |          | 1       | 3 |              | _     |                  |   |  |

|                                                                                                                                                                                 | initHeight:          | 10             | ?        |          |         |   |              | 5     |                  | 3 |  |

|                                                                                                                                                                                 | spcHor:              | 0.1            | ?        |          |         |   |              |       |                  |   |  |

|                                                                                                                                                                                 | spcVer:              | 0.1            | ?        |          |         |   |              | ·     |                  |   |  |

| Generator GUI                                                                                                                                                                   |                      |                |          | Template |         |   | ************ | ••••• | Generated layout |   |  |

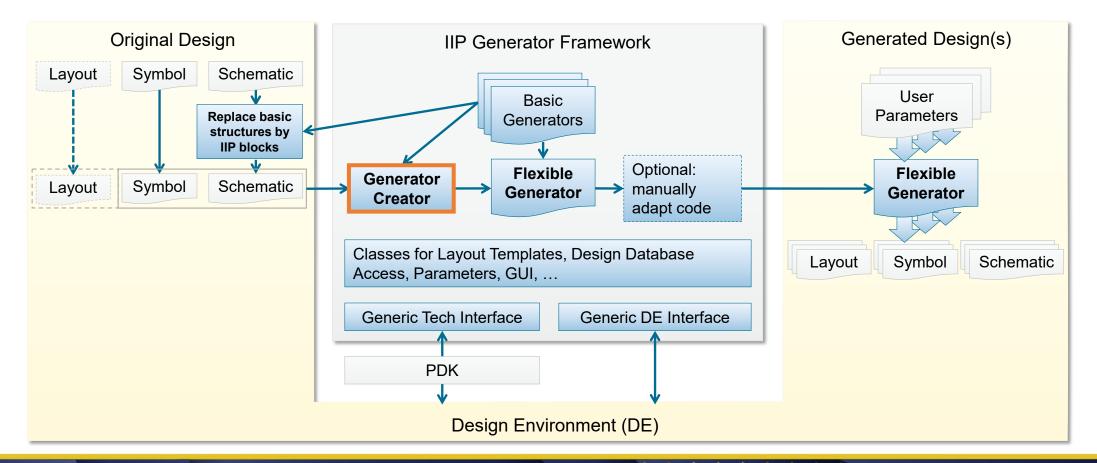

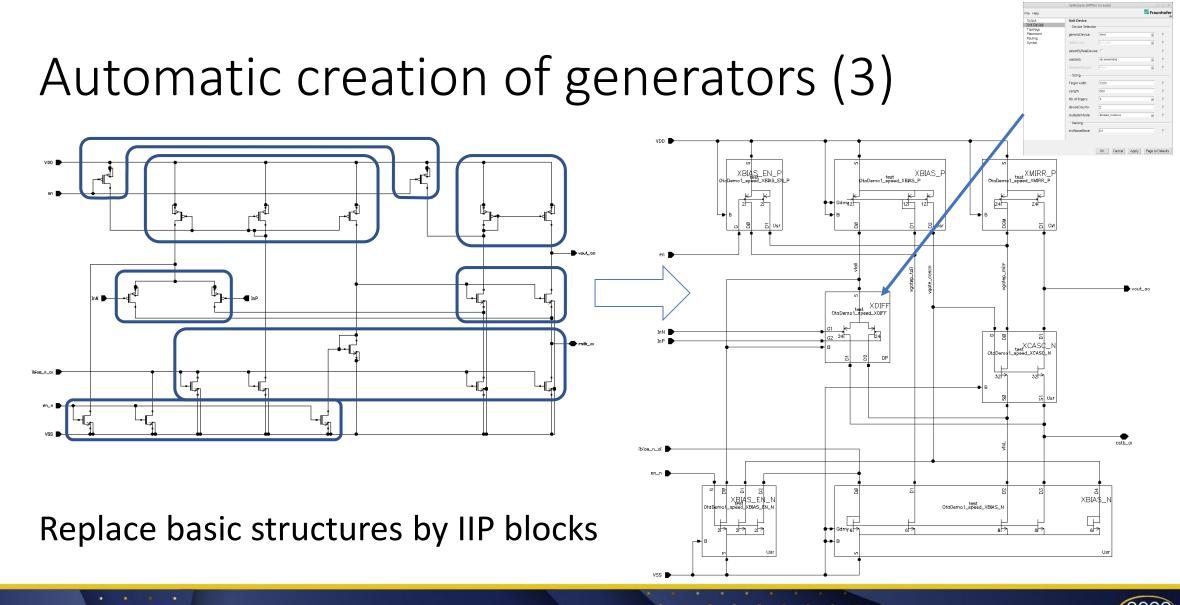

# Automatic creation of generators (1)

#### Automatic creation of generators (2)

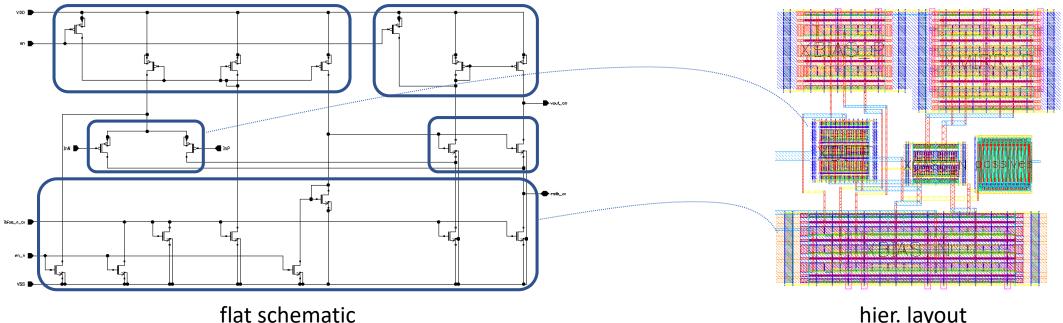

hier. layout (generated by [4])

#### Orig. OTA design example by Infineon [6]

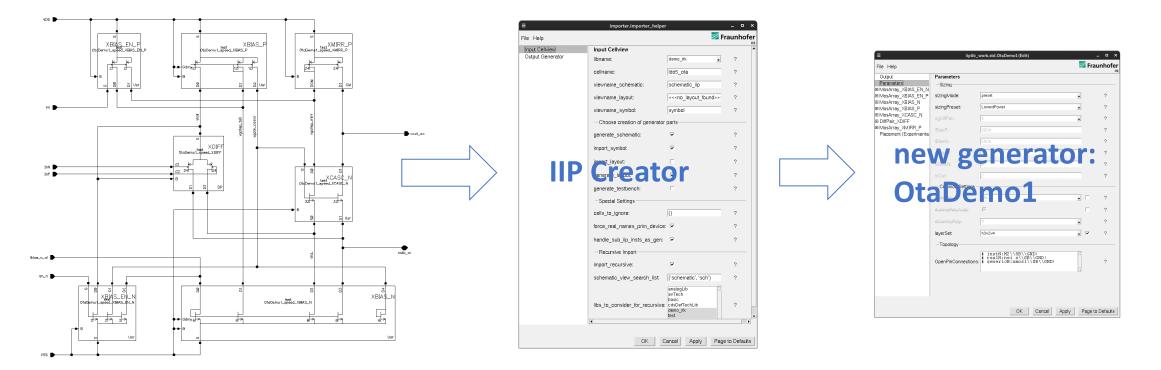

#### Automatic creation of generators (4)

Use IIP Creator to translate available schematic data into a new generator

## Automatic creation of generators (5)

|                                              |                   |                                                                                               |                                             |                                      | File Help                                      | Fraunhofer                                      |                                                                      |   |

|----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------|------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|---|

| E iiplib_wo                                  |                   | _work.std.OtaDemo1 (Edit)                                                                     | _ □ ×                                       | Auto-generated:                      | Output<br>Parameters                           | Placement (Experimental)<br>placeMethod: street |                                                                      | ? |

| Output                                       | Parameters        |                                                                                               | IIS                                         | J                                    | ⊞ MosArray_XBIAS_EN_N<br>⊞ MosArray_XBIAS_EN_P |                                                 | 2                                                                    | ? |

| Parameters<br>MosArray_XBIAS_EN_N            | -Sizing           |                                                                                               |                                             | <ul> <li>inherited</li> </ul>        | ⊞ MosArray_XBIAS_N<br>⊞ MosArray_XBIAS_P       | placeStyle:                                     | user 🗸                                                               | ? |

| MosArray_XBIAS_EN_P     MosArray XBIAS_N     | sizingMode:       | preset                                                                                        | • ?                                         |                                      | ⊞ MosArray_XCASC_N<br>⊞ DiffPair XDIFF         |                                                 | ({{\$,4,7,2}},                                                       |   |

| MosArray_XBIAS_P     MosArray_XCASC_N        | sizingPreset:     | LowestPower                                                                                   | • ?                                         | parameters from                      | MosArray_XMIRR_P<br>Placement (Experimental    | placePattern:                                   |                                                                      | ? |

| DiffPair_XDIFF                               | ngDiffPair:       | 4                                                                                             | • ?                                         | all sub-blocks                       |                                                | initWidth:                                      | 10                                                                   | ? |

| ■ MosArray_XMIRR_P<br>Placement (Experimenta |                   | 900n                                                                                          | ?                                           |                                      |                                                | initHeight:                                     | 10                                                                   | ? |

|                                              | IBiasN:           | 500n                                                                                          | ?                                           | A Tamplata DQD                       |                                                | spcHor:                                         | 0.1                                                                  | ? |

|                                              |                   | 3                                                                                             |                                             | <ul> <li>Template P&amp;R</li> </ul> |                                                | spcVer:                                         | 0.1                                                                  | ? |

|                                              | mBiasN:           | 6                                                                                             | ?                                           | parameters                           |                                                | include_routing                                 | j: 🗖                                                                 | ? |

|                                              | mOut:             | 2                                                                                             | ?                                           |                                      |                                                | routeWidth:                                     | 0.05                                                                 | ? |

|                                              | - Common Settings |                                                                                               |                                             |                                      |                                                | routeSpc:                                       | 0.07                                                                 | ? |

|                                              | ruleSets:         | dfm                                                                                           | •                                           |                                      |                                                | wire_names:                                     | ('ibias_n_ai', 'vgate_cascn', 'VSS', 'en_n', 'vtail', 'vgatep_mirr'  | ? |

|                                              | dummyPoly∆uto:    |                                                                                               | ?                                           |                                      |                                                | exclude_layers                                  | x 🗖                                                                  | ? |

|                                              | nDummyPoly:       |                                                                                               | <ul> <li>✓</li> <li>✓</li> <li>?</li> </ul> | Manually added                       |                                                | -Pattern-to-instance map-                       |                                                                      |   |

|                                              | layerSet:         | h3v2v4                                                                                        |                                             |                                      |                                                | placeDevices:                                   | ((1, 'XBIAS_EN_N'), (2, 'XBIAS_EN_P'), (3, 'XBIAS_N'), (4, 'X        | ? |

|                                              | —Topology———      | # instN:M2\\SB\\GND!                                                                          |                                             | (optional):                          |                                                |                                                 | (( XDIFF, XBIAS P, XMIRR P, XBIAS EN P) XDIAS N, XCASC N, XBIAS EN N | 2 |

|                                              | OpenPinConnection | <pre># instN:M2\\SB\\GND!<br/># realN:nei a\\SB\\GND!<br/>s: # genericN:nmosi\\SB\\GND!</pre> | ?                                           |                                      |                                                |                                                 |                                                                      |   |

|                                              |                   |                                                                                               |                                             | Predefined                           | 4                                              |                                                 |                                                                      |   |

|                                              |                   |                                                                                               |                                             |                                      | OK Cancel Apply Page to Defaults               |                                                 |                                                                      |   |

|                                              |                   |                                                                                               |                                             | parameter sets                       |                                                |                                                 |                                                                      |   |

|                                              |                   | OK Cancel Apply                                                                               | Page to Defaults                            | for usability                        |                                                |                                                 |                                                                      |   |

iiplib\_work.std.OtaDemo1 (Edit

\_ ¤ ×

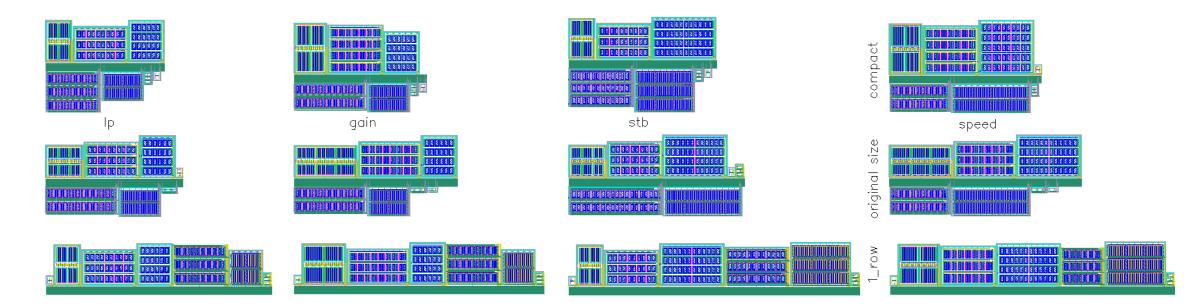

#### Generated layouts

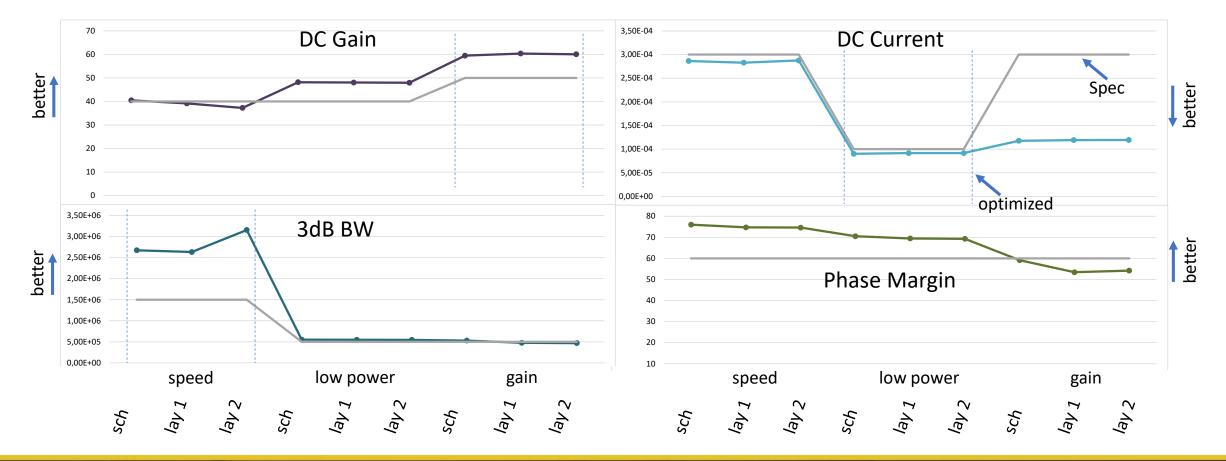

• Original paper: 4 sizing variants, 3 layout variants

#### Generated layouts

• New: updated testbench, 3 sizing variants, 2 layout variants

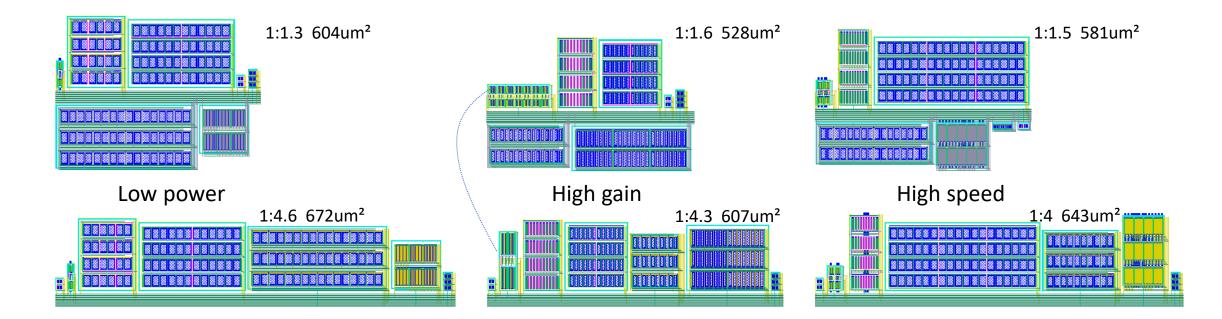

#### Selected performance results

- Generator runtime: ≈ 30 sec (dep. on PDK)

- DRC, LVS clean

- Aspect ratio: 1:1.3 .. 1:4.6, influence on bbox area: max. 15 %

- max. parasitic influence across all 6 layout variants:

- 3dB BW: -11 .. +18 %

- DC gain: -8 .. +2 %

- DC current: -1 .. +2 %

- Phase Margin: -10%

#### Selected performance results

Page 23

SYSTEMS INITIATIVE

#### Summary

- Template-based layouts are feasible for this (and more) types of circuits

- automatic creation of template-based generators may close the gap between generators for basic building blocks and designer-driven layout reuse and synthesis for more complex circuits

- IIP Creator approach allows fast transfer of existing design IP into a much more generic and reusable format

#### Outlook

- Parameter abstraction for aspect ratio, place pattern, routing, sizing

→ early investigation of layout effects, even before simulation

→ layout-aware sizing/optimization

- Better integration into simulation / optimization tool flows

- In progress: [7] [8]

- Parameter interfaces to Cadence ADE, MunEDA WiCkeD, Intento ID-Xplore, ...

- Standardization of a common generator description language

→ interoperability across generator suppliers

- further development driven by public funded projects: AnastASICA, InnoStar, HoLoDEC

# References

Thanks to Husni Habal et al. from Infineon Technologies for providing the original design and many discussions!

This work was funded by the German Federal Ministry of Education and Research BMBF within project InnoStar.

[1] Cadence PCell Designer: https://www.cadence.com

[2] Synopsys PyCell Studio: https://www.synopsys.com

[3] IPGen 1Stone: A. Graupner, R. Jancke und R. Wittmann, "Generator Based Approach for Analog Circuit and Layout Design and Optimization," DATE 2011

[4] Berkeley Analog Generator: E. Chang et al., "BAG2: A Process-portable Framework for Generator-based AMS Circuit Design," CICC 2018

[5] R. Castro-López et al., "An Integrated Layout-Synthesis Approach for Analog ICs," IEEE TCAD, 2008

[6] F. Passerini et al., "ANAGEN: A Methodology for ANAlog Circuit GENeration", ESSCIRC/ESSDERC, 2021

[7] B. Prautsch, R. Iskander et al., "Automatic Generation of Multiple GF-22FDX OpAmp Variants and Layouts in the Virtuoso<sup>®</sup> Suite by Incorporating ID-Xplore<sup>™</sup> of Intento Design with IIP of Fraunhofer IIS/EAS", CadenceLIVE, 2022

[8] B. Prautsch et al., "A Multi-level Analog IC Design Flow for Fast Performance Estimation Using Template-based Layout Generators and Structural Models," SMACD 2022

## Thank you

#### Questions?