MUNICH, GERMANY DECEMBER 6 - 7, 2022

How creativity kills reuse — A modern take on UVM/SV TB architectures

Andrei Vintila, Sergiu Duda

AMIQ Consulting

#### Contents

- Introduction

- Motivation, Scope and Concept

- Runtime controls and Examples

- Plusargs and their usage, Environment setup, Sequence control and text inputs vs compiled tests

- Automation

- Human-readable format, self-improving TBs

- Conclusions

- Development mentality, Usage and advantages

#### Motivation

Why change it if it works?

Complexity vs Functionality

Backend vs Frontend TB development

Divide and conquer

#### Scope

Architecture and Guidelines

Founding blocks

Proof of concept and building a TB

Automation and future work

#### Concept and Rules

- Environment should be organized in such a way that all and any component and object can exist without a dependency on the other (Type agnostic / Allows runtime scaling up/down)

- All sequences should be organized as stand-alone entities, that can dynamically form a testcase based on their order and constraints

- All control variables, as well as stimuli relevant variables, should be registered as plusargs

- Creating a testcase means picking an environment and a collection of sequences

### Plusargs and text inputs

Bare plusargs vs UVM set config var

Scalability and speed

Text file control

Control from outside the sim

```

+env_cfg_0_vip0_is_active=1

+env_cfg_0_vip0_has_checks=1

+env_cfg_0_vip0_has_has_coverage=0

+env_cfg_0_vip3_is_active=1

+env_cfg_0_vip3_has_checks=1

+env_cfg_0_vip3_has_has_coverage=0

+env_cfg_0_vip5_is_active=0

+env_cfg_0_vip5_has_checks=1

+env_cfg_0_vip5_has_coverage=1

```

### Environment setup (1)

```

uvm component components[$];

string component types[$];

string component names[$];

function void create components();

uvm_factory factory; // Handle to the UVM factory that allows the creation of any object via string

// Variable used for creating multiple components of the same type

int cnt:

// Retrieve the factory

factory = uvm factory::get();

// Creating all of the available components

foreach(component types[i]) begin

uvm component local component; // Handle to the current uvm component that is going to be created this 'foreach' iteration

// Create component

local component = factory.create component by name(component types[i], this.get full name(), component names[i], this);

components.push back(local component);

endfunction

function void push all comps();

int index;

string comp type;

string comp name;

string comp name with index;

int comp number;

forever begin

// Retrieve the components passed as plusargs

comp_type = retrieve_comp_type(index);

// If no component name is retrieved, we break the loop

if(comp type == "") break;

// Retrieve the number of agents for the current comp type

// and add them to the queue

comp number = retrieve comp number(index);

// Add the component types to the queue according to the "number of" set

component types.push back(comp type);

// Retrieve the name of the agent

comp name = retrieve comp name(index);

```

```

// If the component name is not defined, set it to the type name, otherwise use the component name given

// If there are multiple instances defined on this comp index, then create all of them incrementally

// adding incremental " *index*" at the end

if(comp name == "")

for(int i=0; i<comp number;i++)</pre>

component names.push back(unique name check(comp type, i, (comp number==1)));

else

for(int i=0; i<comp number;i++)</pre>

component names.push back(unique name check(comp name, i, (comp number==1)));

// Go to the next index

index++;

endfunction

function string retrieve comp type(int index);

string name comp index = $sformatf("%0s comp%0d", get name(), index);

`uvm info(get name(), $sformatf("Looking for comp %s", name comp index), UVM NONE)

if(!$value$plusargs({name comp index, "=%0s"}, retrieve comp type)) retrieve comp type = "";

endfunction

function int retrieve comp number(int index):

string name comp index no = $sformatf("%0s comp%0d no", get name(), index);

`uvm info(get name(), $sformatf("Looking for no %s", name_comp_index_no), UVM_NONE)

if(!$value$plusarqs({name comp index no, "=%0d"}, retrieve comp number)) retrieve comp number = 1;

endfunction

function string retrieve_comp_name(int index);

string name comp index name = $sformatf("%0s comp%0d name", qet name(), index);

`uvm info(get name(), $sformatf("Looking for name %s", name comp index name), UVM NONE)

if(!$value$plusargs({name comp index name, "=%0s"}, retrieve comp name)) retrieve comp name = "";

endfunction

```

# Environment setup (2)

```

class amiq dvcon_environment extends uvm_env;

'uvm component utils(amiq dvcon environment)

function new(string name = "amiq dvcon environment", uvm component parent);

super.new(name, parent);

endfunction : new

virtual function void build phase(uvm phase phase);

super.build phase(phase);

pre create objects();

push all objs();

create objects();

post create objects();

pre create components();

push all comps();

create components();

post create components();

endfunction : build phase

virtual function void pre create objects();

endfunction

virtual function void post create objects();

endfunction

virtual function void pre create components();

virtual function void post create components();

endfunction

`include "amig dvcon comp create functions.svh"

`include "amiq dvcon obj create functions.svh"

`include "amig dvcon reg functions.svh"

```

```

+amiq_dvcon_tb_env_comp0=amiq_dvcon_tb_vip_red_agent

+amiq_dvcon_tb_env_comp0_name=red_agent

+amiq_dvcon_tb_env_comp0_no=2

+amiq_dvcon_tb_env_comp1=amiq_dvcon_tb_vip_blue_agent

+amiq_dvcon_tb_env_comp1_name=blue_agent

+amiq_dvcon_tb_env_comp1_no=1

+amiq_dvcon_tb_env_comp2=amiq_dvcon_tb_vip_purple_agent

+amiq_dvcon_tb_env_comp2_name=purple_agent

+amiq_dvcon_tb_env_comp2_no=3

```

endclass : amiq dvcon environment

#### Environment Setup (3)

```

class amiq_dvcon_object extends uvm_object;

`uvm_object_utils(amiq_dvcon_object)

function new(string name="");

super.new(name);

register_all_vars();

endfunction

`include "amiq_dvcon_reg_functions.svh"

endclass

```

```

+amiq_dvcon_tb_env_obj0=amiq_dvcon_tb_env_cfg

+amiq_dvcon_tb_env_obj0_name=env_cfg_0

+env_cfg_0_vip0_is_active=1

+env_cfg_0_vip0_has_checks=1

+env_cfg_0_vip0_has_has_coverage=0

+env_cfg_0_vip3_is_active=1

+env_cfg_0_vip3_has_checks=1

+env_cfg_0_vip3_has_has_coverage=0

+env_cfg_0_vip5_is_active=0

+env_cfg_0_vip5_has_checks=1

+env_cfg_0_vip5_has_has_coverage=1

```

# Environment Setup (4)

```

class amig dvcon tb env cfg extends amig dvcon object;

// Active/passive for all vips

uvm active passive enum vip0 is active = UVM ACTIVE;

uvm active passive enum vipl is active = UVM ACTIVE;

uvm active passive enum vip2 is active = UVM ACTIVE;

uvm active passive enum vip3 is active = UVM ACTIVE;

uvm active passive enum vip4 is active = UVM ACTIVE;

uvm active passive enum vip5 is active = UVM ACTIVE;

// Enable/disable checks for all vips

bit vip0 has checks;

bit vip0 has coverage:

// Enable/disable coverage for all vips

bit vip1 has checks;

bit vip1 has coverage;

// Enable/disable coverage for all vips

bit vip2 has checks:

bit vip2 has coverage;

// Enable/disable coverage for all vips

bit vip3 has checks:

bit vip3 has coverage;

// Enable/disable coverage for all vips

bit vip4 has checks;

bit vip4 has coverage;

// Enable/disable coverage for all vips

bit vip5 has checks;

bit vip5 has coverage;

'uvm object utils(amiq dvcon tb env cfg)

```

```

function new (string name = "amiq_dvcon_tb_env_cfg");

super.new(name);

endfunction : new

virtual function void register_all_vars();

vip0_is_active = uvm_active_passive_enum'(bit_reg("vip0_is_active"));

vip1_is_active = uvm_active_passive_enum'(bit_reg("vip1_is_active"));

vip0_has_checks = bit_reg("vip0_has_checks");

vip0_has_coverage = bit_reg("vip0_has_coverage");

vip1_has_checks = bit_reg("vip1_has_checks");

vip1_has_coverage = bit_reg("vip1_has_coverage");

vip2_has_checks = bit_reg("vip2_has_checks");

vip2_has_coverage = bit_reg("vip2_has_coverage");

endfunction

```

# Sequence control (1)

```

virtual function void register all vars();

endfunction

function int int reg(string my var name, int default value=0);

uvm info(get name(), $sformatf("Registering field"), UVM NONE)

my var name = {get name(), " ", my var name};

uvm info(get name(), $sformatf("Looking for var:%s", my var name),UVM NONE)

if(!$value$plusargs({my var name, "=%0d"}, int req)) begin

uvm info(get name(), $sformatf("Didn't find the plusarg"),UVM NONE)

int reg = default value;

end else begin

uvm info(get name(), $sformatf("Found the plusarg"),UVM NONE)

endfunction

function bit bit reg(string my var name, bit default value=0);

uvm info(get name(), $sformatf("Registering field"), UVM NONE)

my_var_name = {get_name(), "_", my_var_name};

uvm info(get name(), $sformatf("Looking for var:%s", my_var_name),UVM_NONE)

if(!$value$plusargs({my var name, "=%0b"}, bit req)) begin

uvm info(get name(), $sformatf("Didn't find the plusarg"),UVM NONE)

bit req = default value;

end else begin

'uvm info(get name(), $sformatf("Found the plusarg"),UVM NONE)

endfunction

function string string reg(string my var name, string default value="");

uvm info(get name(), $sformatf("Registering field"), UVM NONE)

my_var_name = {get_name(), "_", my_var_name};

'uvm info(get name(), $sformatf("Looking for var:%s", my var name),UVM NONE)

if(!$value$plusargs({my var name, "=%0s"}, string reg)) begin

uvm info(get name(), $sformatf("Didn't find the plusarg"),UVM NONE)

string reg = default value;

end else begin

'uvm info(get name(), $sformatf("Found the plusarg"),UVM NONE)

endfunction

```

```

class amiq_dvcon_sequence extends uvm_sequence;

`uvm_object_utils(amiq_dvcon_sequence)

// new - constructor

function new(string name = "amiq_dvcon_sequence");

super.new(name);

endfunction : new

virtual task pre_body();

super.pre_body();

register_all_vars();

endtask : pre_body

`include "amiq_dvcon_reg_functions.svh"

endclass : amiq_dvcon_sequence

`endif // _amiq_dvcon_sequence

```

# Sequence control (2)

```

function void retrieve all seq type();

string seq type;

string seg name;

bit seq parallel;

int index;

forever begin

// Retrieve the sequences passed as plusargs

seq type = retrieve seq type(index);

// If no sequence name is retrieved, we break the loop

if(seq type == "") break;

// If the sequence exists, retrieve its name, if that is defined

seq name = retrieve seq name(index);

// If the name is not defined, create it based on the type and the index

if(seq name=="") seq name = $sformatf("%0s %0d", seq type, index);

// If the parallelism status is defined, retrieve it, otherwise it is serial

seq parallel = retrieve seq if parallel(index);

// Push the type, name and parallelism status

sequence types.push back(seq type);

sequence names.push back(seq name);

sequence parallel.push back(seq parallel);

index++:

```

endfunction

### Text inputs vs tests (1)

```

class amiq dvcon test extends uvm test;

// Sequence types

string sequence types[$];

// Sequence names

string sequence names[$];

// Sequence serial/parallel

bit sequence parallel[$];

// Virtual sequencer

uvm sequencer virtual sequencer;

// Used to create components

// Needs to be retrieved so it is instantiated globally to reduce performance hit

uvm factory factory;

'uvm component utils(amiq dvcon test)

function new(string name = "amiq dvcon test", uvm component parent=null);

super.new(name,parent);

endfunction : new

virtual function void build phase(uvm phase phase);

super.build phase(phase);

endfunction : build phase

task run phase(uvm phase phase);

super.run phase(phase);

if(virtual sequencer==null) `uvm fatal(get name(), $sformatf("A virtual sequence has to be set in the test on which all defined virtual sequences will be started."))

// Retrieve the factory globally so it is available in all functions without having to "get" it multiple times

factory = uvm_factory::get();

// Read the plusargs for all the defined sequences and save their type together with the name and parallelism status, if defined

retrieve all seq type();

// Based on the previous returned types, names and parallelism status create and start all sequences

for(int i=0; i<sequence types.size(); i++) begin</pre>

schedule sequence(i);

wait threads(i):

endtask : run phase

```

```

+seq0=amiq dvcon tb seq

+seq0 name=amig dvcon tb seq0 0

+amig dvcon tb seg0 0 red field0 start 0=0

+amig dvcon tb seq0 0 red field0 end 0=1024

+amig dvcon tb seg0 0 red field0 weight 0=100

+amig dvcon tb seg0 0 blue pkt nr=0

+amig dvcon tb seg0 0 purple pkt nr=0

+seq1=amiq dvcon tb seq

+seq1 name=amig dvcon tb seq0 1

+seal p=1

+amig dvcon tb seg0 1 red pkt nr=0

+amig dvcon tb seg0 1 blue pkt nr=3000

+amig dvcon tb seg0 1 blue agent id=2

+amig dvcon tb seg0 1 purple pkt nr=0

+seq2=amiq dvcon tb seq

+seq2 name=amig dvcon tb seq0 2

+seq2 p=1

+amig dvcon tb seg0 2 red pkt nr=0

+amig dvcon tb seg0 2 blue pkt nr=0

+amig dvcon tb seg0 2 purple pkt nr=1500

+amig dvcon tb seg0 2 purple field0 start 0=0

+amig dvcon tb seg0 2 purple field0 end 0=127

+amig dvcon tb seg0 2 purple field0 weight 0=50

+amig dvcon tb seg0 2 purple field0 start 1=128

+amig dvcon tb seg0 2 purple field0 end 1=512

+amig dvcon tb seg0 2 purple field0 weight 1=50

```

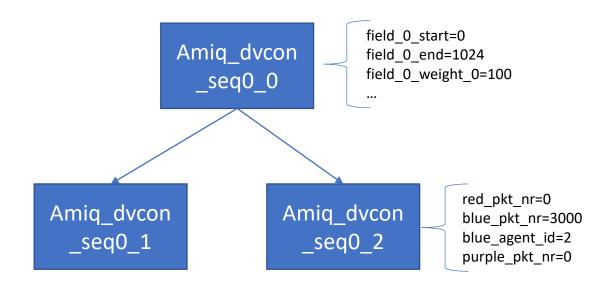

#### Text inputs vs tests (2)

```

+seq0=amig dvcon tb seq

+seq0 name=amig dvcon tb seq0 0

+amig dvcon tb seg0 0 red field0 start 0=0

+amig dvcon tb seg0 0 red field0 end 0=1024

+amig dvcon tb seg0 0 red field0 weight 0=100

+amig dvcon tb seg0 0 blue pkt nr=0

+amig dvcon tb seg0 0 purple pkt nr=0

+seq1=amig dvcon tb seq

+seq1 name=amiq dvcon tb seq0 1

+seq1 p=1

+amig dvcon tb seg0 1 red pkt nr=0

+amiq dvcon tb seq0 1 blue pkt nr=3000

+amig dvcon tb seg0 1 blue agent id=2

+amiq dvcon tb seq0 1 purple pkt nr=0

+seq2=amiq dvcon tb seq

+seq2 name=amig dvcon tb seq0 2

+seq2 p=1

+amiq dvcon tb seq0 2 red pkt nr=0

+amig dvcon tb seg0 2 blue pkt nr=0

+amiq dvcon tb seq0 2 purple pkt nr=1500

+amig dvcon tb seg0 2 purple field0 start 0=0

+amig dvcon tb seg0 2 purple field0 end 0=127

+amiq dvcon tb seq0 2 purple field0 weight 0=50

+amiq dvcon tb seq0 2 purple field0 start 1=128

+amiq dvcon tb seq0 2 purple field0 end 1=512

+amig dvcon tb seg0 2 purple field0 weight 1=50

```

# Automation (1)

| Parent name       | Component Type                 | Component Name | Number of components |

|-------------------|--------------------------------|----------------|----------------------|

| amiq_dvcon_tb_env | amiq_dvcon_tb_vip_red_agent    | red_agent      | 2                    |

| amiq_dvcon_tb_env | amiq_dvcon_tb_vip_blue_agent   | blue_agent     | 1                    |

| amiq_dvcon_tb_env | amiq_dvcon_tb_vip_purple_agent | purple_agent   | 3                    |

| Parent name       | Object Type           | Object Name | Field                 | Value |

|-------------------|-----------------------|-------------|-----------------------|-------|

| amiq_dvcon_tb_env | amiq_dvcon_tb_env_cfg | env_cfg_0   | vip0_is_active        | 1     |

|                   |                       |             | vip0_has_checks       | 1     |

|                   |                       |             | vip0_has_has_coverage | 0     |

|                   |                       |             | vip3_is_active        | 1     |

|                   |                       |             | vip3_has_checks       | 1     |

|                   |                       |             | vip3_has_has_coverage | 0     |

|                   |                       |             | vip5_is_active        | 0     |

|                   |                       |             | vip5_has_checks       | 1     |

|                   |                       |             | vip5_has_has_coverage | 1     |

#### Automation (2)

| Sequence type     | Sequence name        | Field                  | Value | Run in parallel (YES/NO |

|-------------------|----------------------|------------------------|-------|-------------------------|

| amiq_dvcon_tb_seq | amiq_dvcon_tb_seq0_0 | red_field0_start_0     | 0     | NO                      |

|                   |                      | red_field0_end_0       | 1024  |                         |

|                   |                      | red_field0_weight_0    | 100   |                         |

|                   |                      | blue_pkt_nr            | 0     |                         |

|                   |                      | purple_pkt_nr          | 0     |                         |

| amiq_dvcon_tb_seq | amiq_dvcon_tb_seq0_1 | red_pkt_nr             | 0     | YES                     |

|                   |                      | blue_pkt_nr            | 3000  |                         |

|                   |                      | blue_agent_id          | 2     |                         |

|                   |                      | purple_pkt_nr          | 0     |                         |

| amiq_dvcon_tb_seq | amiq_dvcon_tb_seq0_2 | red_pkt_nr             | 0     | YES                     |

|                   |                      | blue_pkt_nr            | 0     |                         |

|                   |                      | purple_pkt_nr          | 1500  |                         |

|                   |                      | purple_field0_start_0  | 0     |                         |

|                   |                      | purple_field0_end_0    | 127   |                         |

|                   |                      | purple_field0_weight_0 | 50    |                         |

|                   |                      | purple_field0_start_1  | 128   |                         |

|                   |                      | purple_field0_end_1    | 512   |                         |

|                   |                      | purple field0 weight 1 | 50    |                         |

```

+seq0=amig dvcon tb seq

+seq0 name=amig dvcon tb seq0 0

+amig dvcon tb seg0 0 red field0 start 0=0

+amig dvcon tb seg0 0 red field0 end 0=1024

+amig dvcon tb seg0 0 red field0 weight 0=100

+amig dvcon tb seg0 0 blue pkt nr=0

+amig dvcon tb seg0 0 purple pkt nr=0

+seq1=amig dvcon tb seq

+seq1 name=amiq dvcon tb seq0 1

+seq1 p=1

+amig dvcon tb seg0 1 red pkt nr=0

+amig dvcon tb seg0 1 blue pkt nr=3000

+amig dvcon tb seg0 1 blue agent id=2

+amig dvcon tb seg0 1 purple pkt nr=0

+seg2=amig dvcon tb seg

+seq2 name=amiq dvcon tb seq0 2

+seq2 p=1

+amiq dvcon tb seq0 2 red pkt nr=0

+amig dvcon tb seg0 2 blue pkt nr=0

+amiq dvcon tb seq0 2 purple pkt nr=1500

+amiq dvcon tb seq0 2 purple field0 start 0=0

+amiq dvcon tb seq0 2 purple field0 end 0=127

+amiq dvcon tb seq0 2 purple field0 weight 0=50

+amiq dvcon tb seq0 2 purple field0 start 1=128

+amiq dvcon tb seq0 2 purple field0 end 1=512

+amig dvcon tb seq0 2 purple field0 weight 1=50

```

#### Conclusions

Simplicity is key to scalability

Drawing outside the lines can be an inconvenient in engineering

Verification is a puzzle, not a painting

Past a certain threshold of scale, maintenance effort supersedes debug

# What are we working on

Further automation on TB creation

Debug helper

Ranking based on runtime events

Feedback loop (DVCon US 2023)

#### Questions