MUNICH, GERMANY DECEMBER 6 - 7, 2022

# Automate Interrupt Checking with UVM Macros and Python

Aleksandra Dimanic & Nemanja Stevanovic, Vtool Ltd Yoav Furman & Itay Henigsberg, Chain Reaction Ltd

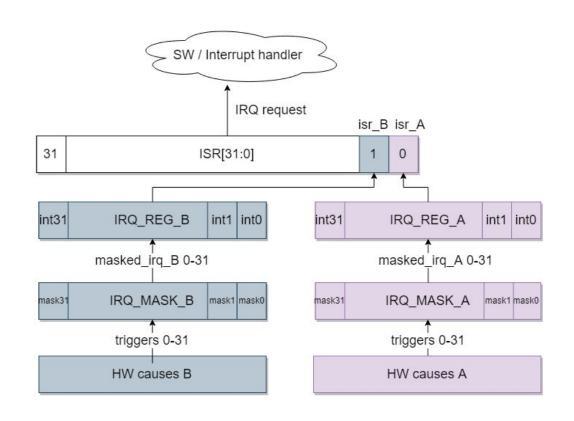

#### Interrupt overview

- Essential part of every design

- Common ground for IRQ handling:

- Usually grouped in blocks in design and share common paths and behavior

- IRQ trigger is coming from design

- Reflected in status registers with masking/unmasking/set/reset mechanism

- By taking those common parts the checking can be accelerated and partially automated

# Explaining the concept

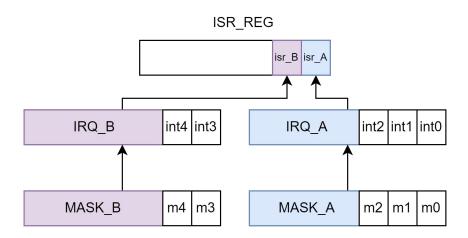

- Each IRQ has its corresponding register or a field in the register

- Groups or IRQs are mapped in ISR (Interrupt Status Register)

- Registers always have to reflect the correct values of the IRQs

#### Explaining the concept

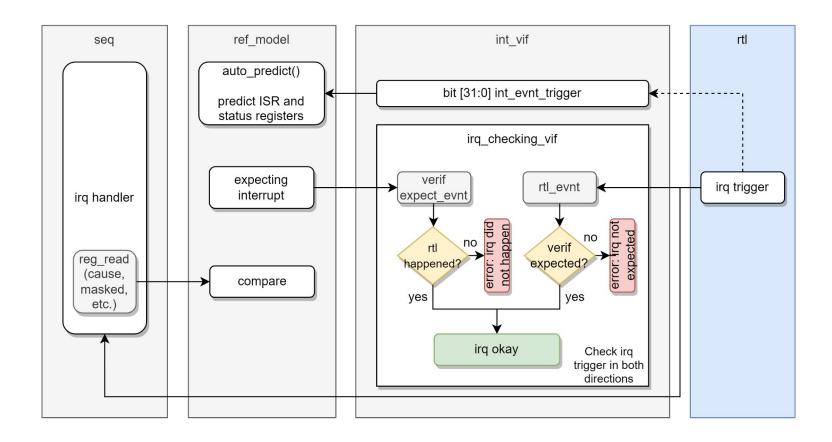

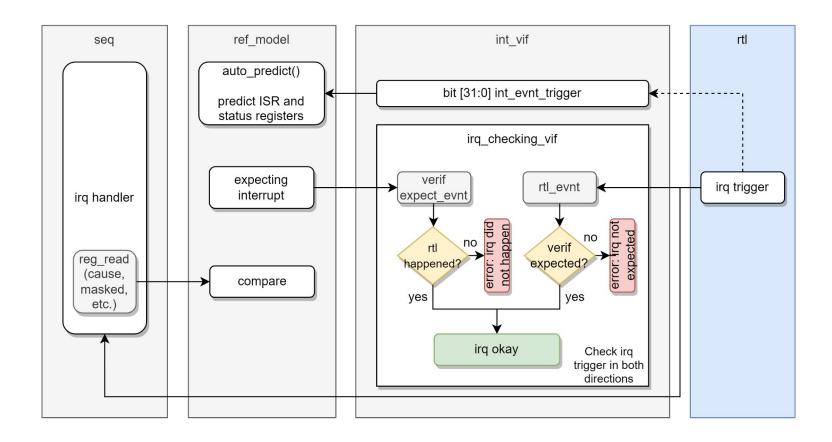

- Problem #1:

- Verification often isn't in sync with the RTL

- Solution #1:

- Separate verification checkers from the register prediction

- Create general task for automatic prediction

- Prediction is based on the trigger coming from the design

- Goal: Check the aggregation of the interrupt

#### Explaining the concept

- Problem #2:

- Verifying the interrupt trigger

- Checking must be done in both directions

- Solution #2:

- Create interrupt checking interface

- Interface is configurable and applicable to both edge and level triggered IRQs

- Goal: Verify the interrupt trigger

# Flow of checking

#### Handling status and control registers

Prediction using macros

```

`define IRQ_AUTO_PREDICT(isr_reg_name, isr_field, irq_reg_name, irq_field,

reg_mask_name, reg_mask) \

forever begin \

int position = reg_model.IRQ_BLOCK.irq_reg_name.irq_event.get_lsb_pos(); \

@(posedge int_vif.int_event_trigger position]); \

if(!reg_model.IRQ_BLOCK.reg_mask_name.reg_mask.get_mirrored_value()) begin \

`uvm_info(get_full_name(), $sformatf("Predicting ISR reg due to %s",

reg_model.IRQ_BLOCK.irq_reg_name.irq_event.get_name()), UVM_HIGH) \

assert(reg_model.IRQ_BLOCK isr_reg_name.isr_field.predict(.value(1))); \

end \

end \

end \

```

#### Handling status and control registers

auto\_predict()

```

task auto_predict();

fork

//IRQ_REG_A

`IRQ_AUTO_PREDICT(ISR, isr_A, IRQ_REG_A, int0, IRQ_MASK_A, mask0)

. .

`IRQ_AUTO_PREDICT(ISR, isr_A, IRQ_REG_A, int31, IRQ_MASK_A, mask31)

//IRQ_REG_B

`IRQ_AUTO_PREDICT(ISR, isr_B, IRQ_REG_B, int0, IRQ_MASK_B, mask0)

. .

`IRQ_AUTO_PREDICT(ISR, isr_B, IRQ_REG_B, int31, IRQ_MASK_B, mask31)

join_none

endtask

```

# Flow of checking

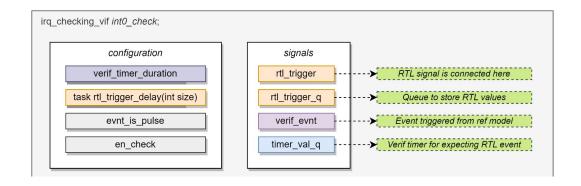

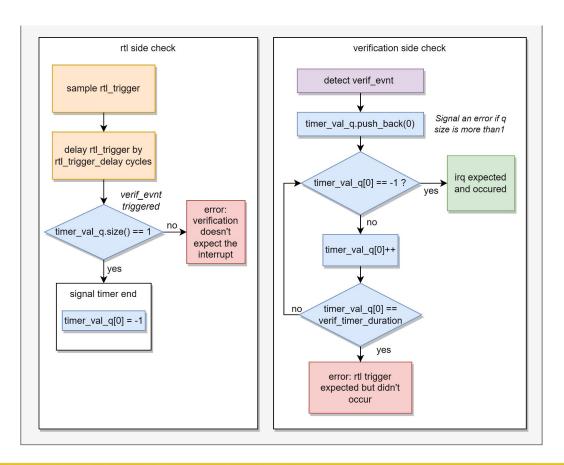

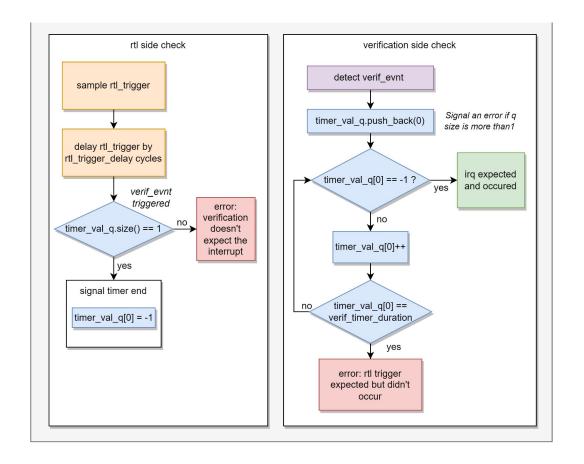

# How does irq\_checking\_vif work?

- Verification must be triggered first

- Two scenarios:

- RTL trigger happens before verification

- Verification happens before RTL

rtl\_trigger\_delay(int size)

```

task rtl_trigger_delay(int size);

if (size == 0) `uvm_error("%m", "Size cannot be zero")

repeat(size) rtl_trigger_q.push_back(0);

endtask

```

Sampling and delaying is done in an always block

```

always @(posedge clk) begin

void'(rtl_trigger_q.pop_front());

void'(rtl_trigger_q.push_back(rtl_trigger));

end

```

- Wait for rtl\_trigger\_q[0] to change from 0 to 1

- Call a task to check the occurrence of verif\_evnt

- Check the status of queue timer\_val\_q

- If *verif\_evnt* was not triggered:

- ERROR: Verification doesn't expect the interrupt

- If the *verif\_evnt* was already expected:

- timer\_val\_q[0] will be set to -1

```

always @(posedge clk) //for pulses |**|

if (evnt is pulse && rtl trigger q[0])

check if evnt expected();

always @(posedge rtl_trigger_q[0] iff !evnt is pulse ) //for level | *****

check if evnt expected();

function void check if evnt expected();

`uvm info($sformatf("%m"), "rtl event triggered", UVM HIGH)

if (en check)

if (timer val q.size == 1) timer val q[0] = -1;

else `uvm error($sformatf("%m"), "RTL event occurred without it being expected.")

endfunction

```

### Checking verification event

- Initialize the timer\_val\_q value

- Start the timer

- verif\_timer\_duration sets the time window for RTL event

#### Checking verification event

```

always @ (verif evnt)

if (en check && (evnt is pulse || rtl trigger q[0] === 0)) begin

if(!timer_val_q.size()) timer_val_q.push_back(0);

else `uvm error($sformatf("%m"), "verif event expected more than once")

`uvm info($sformatf("%m"), "verif event triggered", UVM HIGH)

if (timer_val_q.size == 1)

fork

check expected ev happens(); //check if rtl signal happens

join none

end

```

#### Checking verification event

```

task check expected ev happens();

while (timer_val_q.size > 0) begin

@(posedge clk);

if (timer val q[0] == -1) begin

void'(timer_val_q.pop_front());

`uvm info($sformatf("%m"), "RTL event expected and occured.", UVM HIGH)

end

if (timer val q[0] == verif timer duration) begin

void'(timer val q.pop front());

`uvm error($sformatf("%m"), "RTL event didn't occur although expected in

verification.")

end else

timer val q[0] += 1;

end // while

endtask // check expect happens

```

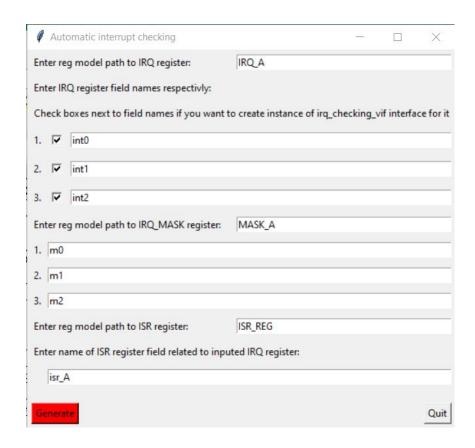

- Take advantage of repeating IRQ behavior and standard verification procedure

- Create script based on main building blocks of code

| Automatic interrupt checking                    |                             | _        |             | $\times$  |

|-------------------------------------------------|-----------------------------|----------|-------------|-----------|

| Enter reg model path to IRQ register:           | IRQ_B                       |          |             |           |

| Enter IRQ register field names respectivly:     |                             |          |             |           |

| Check boxes next to field names if you want     | to create instance of irq_c | hecking_ | vif interfa | ce for it |

| 1. 🔽 int3                                       |                             |          |             |           |

| 2. 🔽 int4                                       |                             |          |             | -         |

| Enter reg model path to IRQ_MASK register:      | MASK_B                      |          |             |           |

| 1. m3                                           |                             |          |             |           |

| 2. m4                                           |                             |          |             |           |

| Enter reg model path to ISR register:           | ISR_REG                     |          |             |           |

| Enter name of ISR register field related to inp | uted IRQ register:          |          |             |           |

| isr_B                                           |                             |          |             |           |

| Generate                                        |                             |          |             | Quit      |

| Generate                                        |                             |          |             | Quit      |

```

fork

`IRQ AUTO PREDICT(ISR REG, isr A, IRQ A, int0, MASK A, m0) //IRQ A

`IRQ AUTO PREDICT(ISR REG, isr A, IRQ A, int1, MASK_A, m1) //IRQ A

`IRQ AUTO PREDICT(ISR REG, isr A, IRQ A, int2, MASK A, m2) //IRQ A

`IRQ AUTO PREDICT(ISR REG, isr B, IRQ B, int3, MASK B, m3) //IRQ B

`IRQ AUTO PREDICT(ISR REG, isr B, IRQ B, int4, MASK B, m4) //IRQ B

join none

irq checking vif trigger check IRQ A int0;

irq checking vif trigger check IRQ A int1;

irq checking vif trigger check IRQ A int2;

irq checking vif trigger check IRQ B int3;

irq checking vif trigger check IRQ B int4;

```

- Upgrading the script:

- Remove gui

- Generate everything based on Excel Spreadsheet

- Add additional building blocks of code for your specific project

# Conclusion – Why use auto prediction?

- Checking is centralized in one location

- An independent standardized mechanism is created

- Debug and implementation process easier and faster

# Conclusion – Why use irq\_checking\_vif?

- Checking in both directions

- Precise checking because the detection window can be narrow

- Configurable and applicable to all interrupts (pulses and levels)

#### Results

- Increased code reusability

- Partially automated checking

- Decreased the time needed in order to fully verify the interrupts

- Reusable on the same project, but also on company level

# Questions?

# Thank you!

aleksandrad@thevtool.com nemanjas@thevtool.com yoavf@chain-reaction.io itayh@chain-reaction.io