MUNICH, GERMANY DECEMBER 6 - 7, 2022

### Building Confidence in System Level CPU Cache Coherency Verification for Complex SoCs through a Configurable Flexible and Portable Test Bench

S Shrinidhi Rao, Ruchi Misra, Alok Kumar, Garima Srivastava, YoungSik Kim, Seonil Brian Choi

SAMSUNG

SYSTEMS INITIATIVE

### Agenda

- Motivation

- A Typical Multi-Core System Architecture

- Scope of PSS in CPU Verification

- PSS : An Accelera Standard

- Methodology

- TestBench Modification

- Solution Generation

- Tool View

- Results

- Conclusion

- Future Scope

### Motivation

- Coherence protocols trigger complex interactions between heterogeneous mixes of caches • and other system masters

- Our regular SoC scenarios are less aggressive on cache functionalities as compared to IP level testbench.

- Traditional approaches can sometimes miss bugs that arise only in a complex system level traffic.

- Writing large numbers of effective tests is difficult, time consuming, and error prone.

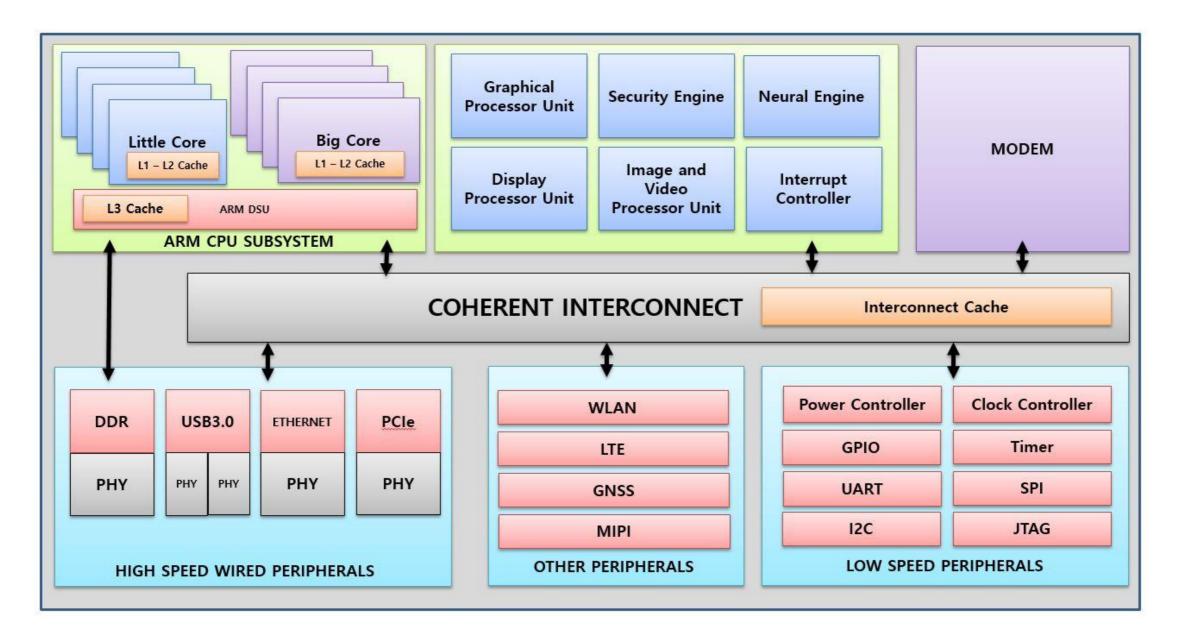

### A Typical Multi-Core System Architecture

# Scope of PSS in CPU Verification

- Portability of reusable test cases has long been a goal for semiconductor verification and validation teams. No one wants to 'reinvent the wheel' by having to rewrite similar tests again and again.

- Verification of the CPU design in our multiple complex mobile/automotive or wearable SoCs is mainly done through C tests.

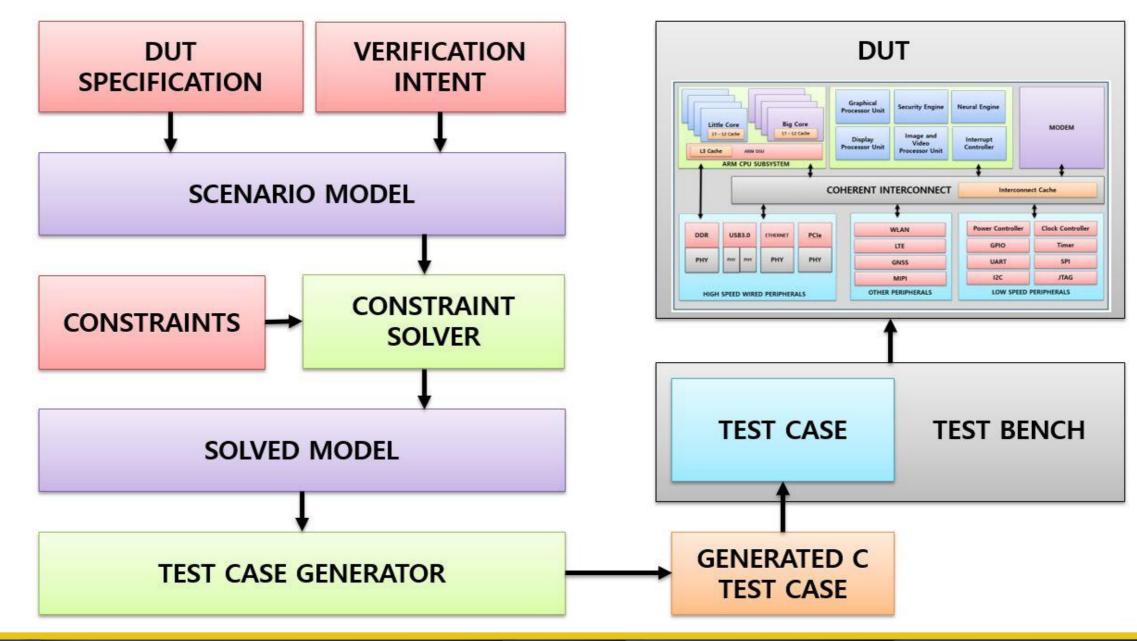

- This configurable testbench takes the specific configurations of the SoC as user-defined inputs, generates generic C code for some standard operations, and combines them to generate final C scenarios that run on embedded CPUs and exercises the system through diverse relevant solutions.

- The code generated for the simulation platform can then be re-used by the other 3 dependent environments, allowing reuse across various verification platforms.

### Portable Test And Stimulus: An Accelera Standard

- PSS has been tried and tested in the industry

- Well established Vertical and Horizontal Reuse strategies

- Proven to enhance performance and verification efficiency

## Methodology

- C based existing test bench

- Input to Solver

- Design specification

- Test and Design constraints

- Pre-built action/function modules

- Verification intent

- Output of Solver

- Solution for verification intent

- C code based on solutions generated

- Coverage report

- Plug and Play

| void main(voi         | id);                          |

|-----------------------|-------------------------------|

| {<br>//variable initi | alization                     |

|                       |                               |

| //boot sequer         | ice and system initialization |

| generated_c_o         | code();                       |

| //other generi        | c test sequences              |

### **GENERATED C CODE**

void generated\_c\_code(void)

//generated test case functionality

//error check

### **Test Bench Modification**

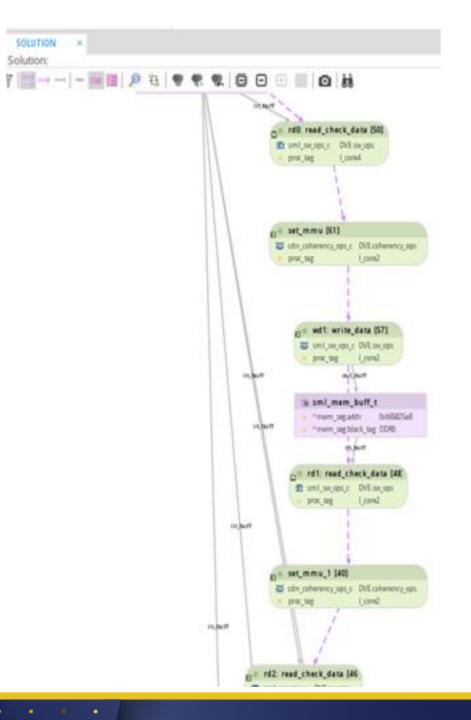

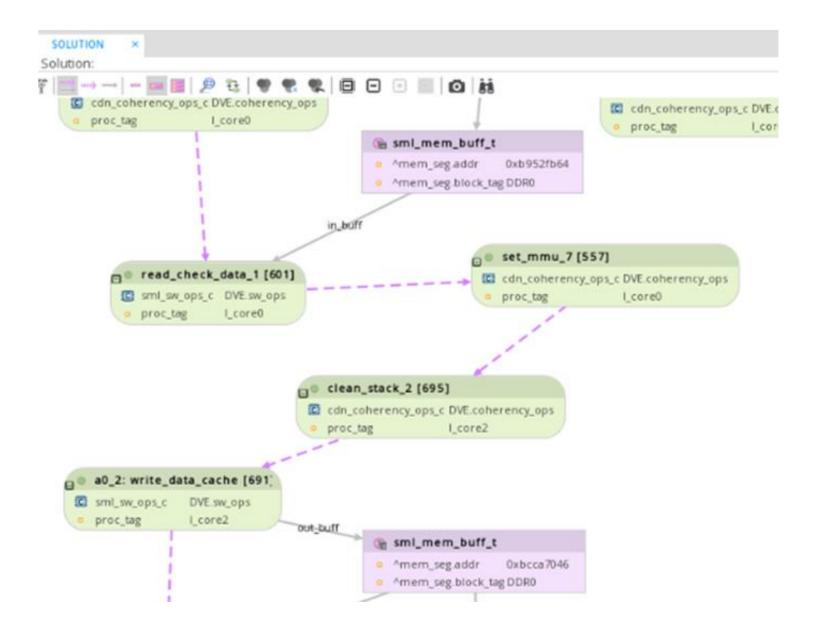

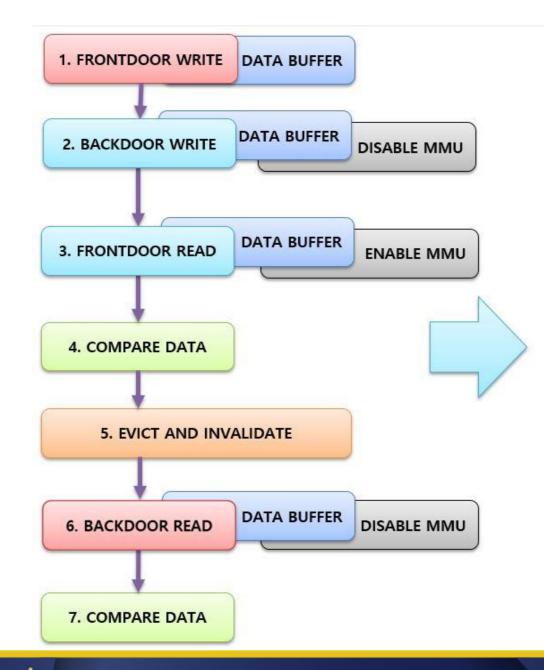

### **Solution Generation**

SOLUTION

Solution:

### Solution to Test Case

```

void read hit miss check(void)

unsigned int write data frontdoor, write data backdoor, read data;

unsigned int * write address = (unsigned int *) 0x1000;

unsigned int * read address = (unsigned int *) 0x1000;

write data frontdoor = Oxaaaa

write data backdoor = 0x5555;

*write address++ = write data frontdoor;

*write address++ = write data frontdoor;

*write address++ = write data frontdoor;

*write address++ = write data frontdoor;

write address = read address;

BACKDOOR WRITE(write address, 4, write data backdoor);

for (i=0;i<4 ;i++){</pre>

read data = *(read address++);

if (read data != write data frontdoor)

printf("ERROR : READ MISS : Data read is fetched from Memory");

else

printf("INFO : READ HIT : Data read is fetched from Cache");

invalidate and evict cache ();

for (i=0;i<4 ;i++){</pre>

BACKDOOR READ(read address, read data);

if (read data != write data frontdoor)

printf("ERROR : Cache Eviction failed");

else

printf("INFO : Cache Eviction Success");

```

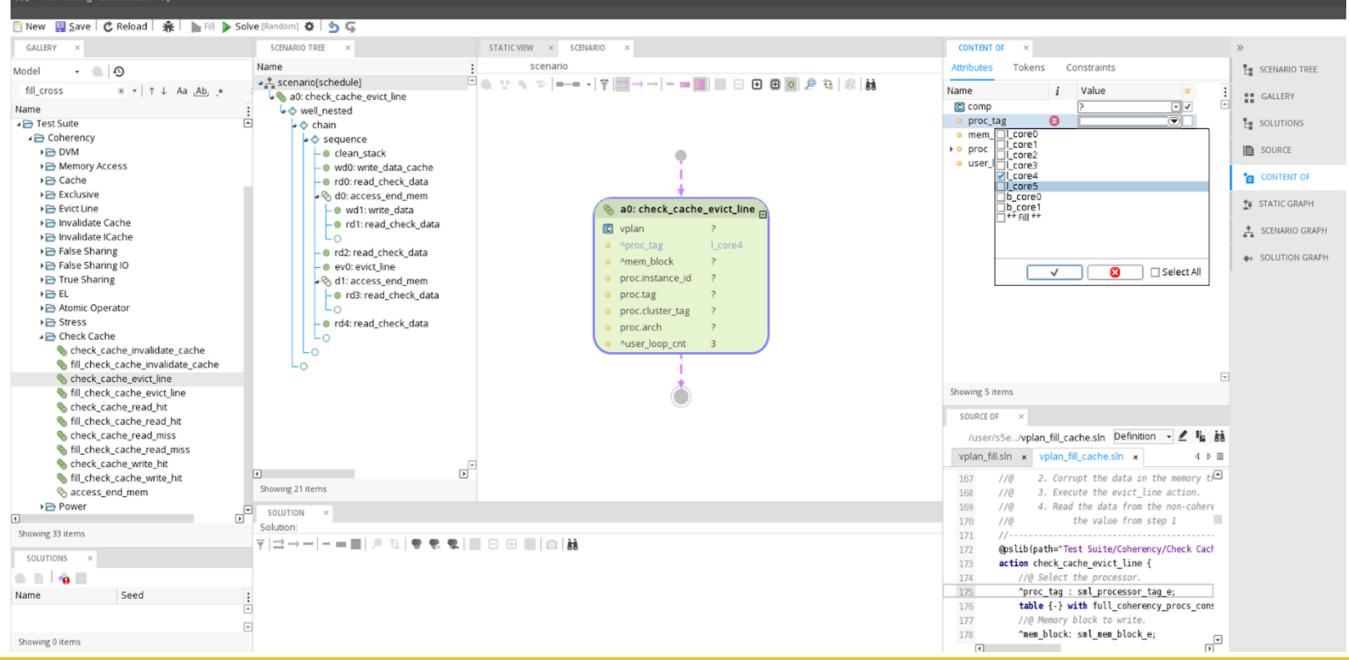

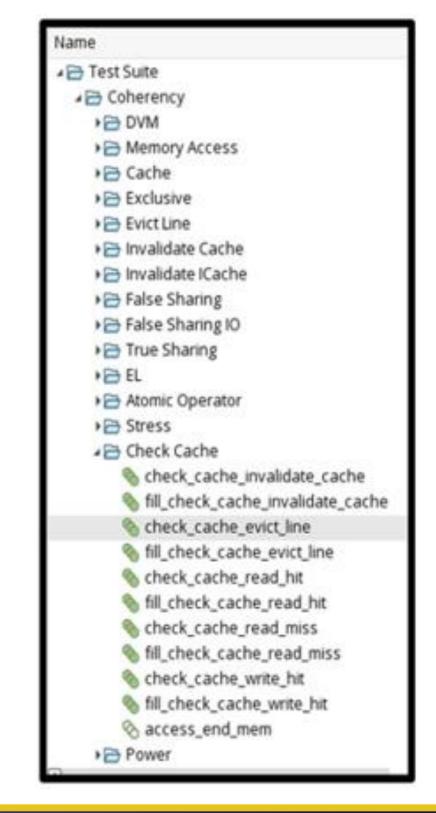

### Tool View

File View Config Commands Help

# Some Example Scenarios

- Fill Cache Boundaries: A stand-alone Allocate to Cache task allocates a memory block to cache.

- Cache State Transitions: Using the different variety of opcodes supported, this complex test covers various cache state transitions with the help of an in-built checker.

- Data Sharing Scenarios: True Sharing and False sharing of data between cores in a coherent setup can significantly degrade cache performance, in systems when smallest data size accessed is smaller than cache line size

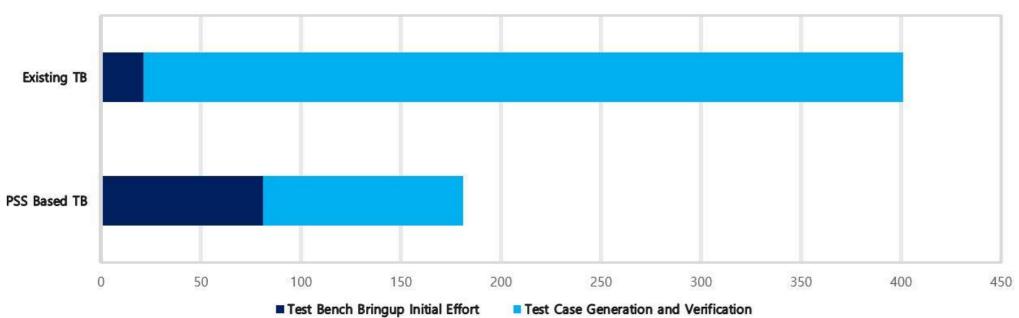

### Results

- Case study run on Exynos Mobile SoC environment

- Initial setup needed multiple iterations to fix compatibility issues

- 2 months to clean the setup and 3 months to run the complete set of tests

- Target Cache verification vectors

- Verify Cache information such as size, allocation, overflow

- Cache State Transitions : evict, invalidate, cache hit/miss

• Cache performance : True Sharing and False Sharing

### Conclusion

- Though initial effort was high, effort required for future projects is minimal

- Generate coverage reports at each step of test case generation

- Help identify verification loopholes

- Better coverage

- Ease of portability across multiple projects

- Portable, re-usable and scenarios can be easily reproduced

- Confidence in verification due to constrained random scenario generation

- Flexibility to modify test at each step

- Ease of portability across projects

- Number of test cases that can be generated is high compared to manual development

### Future Scope

- Recommended to be implemented in subsequent projects

- Opportunity to stress cache operations at SoC context

- Extend suite to Last Level Caches and I/O Coherency

- Enhance libraries to include newer ARM architectures

- Target power and clock control for power scenarios

- Combine power and Cache operations to stress design

### Acknowledgement

The authors would like to thank Samsung Semiconductors India Research for enabling the work mentioned in this paper. We would also like to thank DVCon Europe team for giving us the opportunity to participate in the conference and present our work.