## SoC.one

XploR, a Platform to Accelerate Silicon Transformation

# Challenges for the system designers undergoing silicon transformation

- Vertically integrated products (AI / edge, automotive, wireless) are highly specialized

- Products are more complex and multidimensional (e.g., domain customization, software, hardware system design, semiconductor integration)

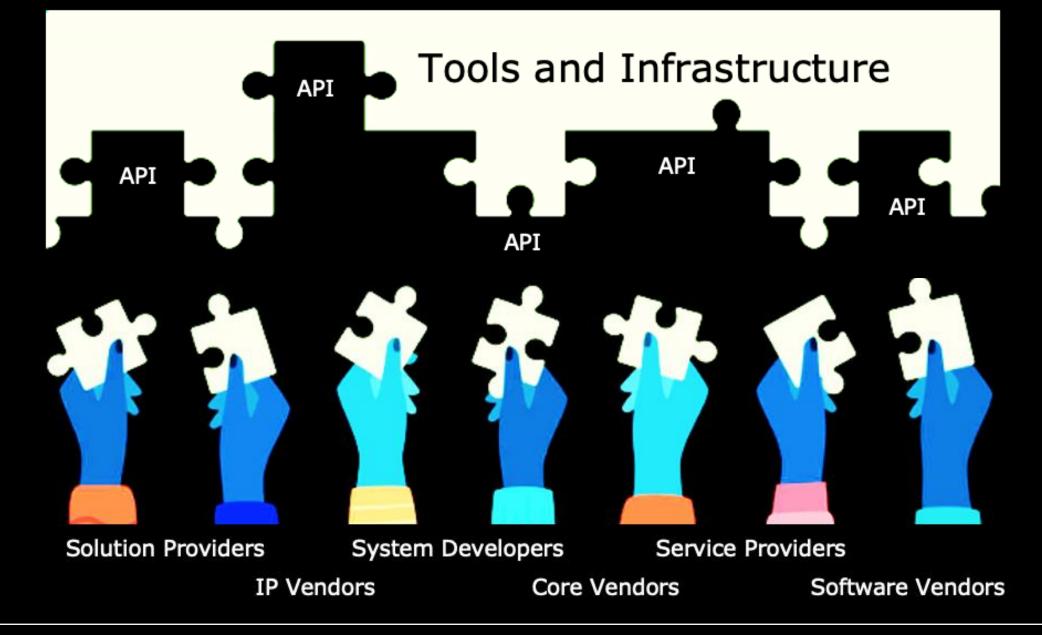

- Design industry evolved into different pockets

of excellence. Within these, system designers

are forced to choose and work with solutions

from best of breeds.

- System companies engage in human intensive tasks of building teams and developing expertise to find, integrate, and support solutions from different vendors.

## Typical development flow System companies as solution integrators

System companies use products / solutions from different vendors for different needs

Even different solutions from the same vendor are not fully integrated

Solution and product vendors operate in silos

System companies forced to

## Consequences of solution silos

- Higher costs, more risks, and longer development life cycle for system companies.

- Difficulty to scale ambidextrous work force capable of transitioning to and supporting different solutions at different stages of development.

- Less opportunities for solution vendors to show-case value-add, and for emerging, smaller vendors to gain market exposure.

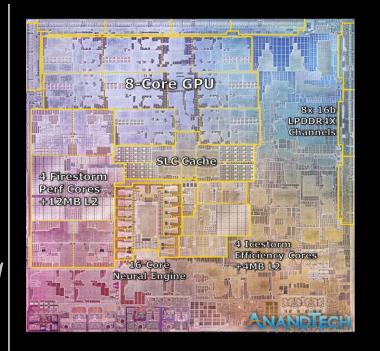

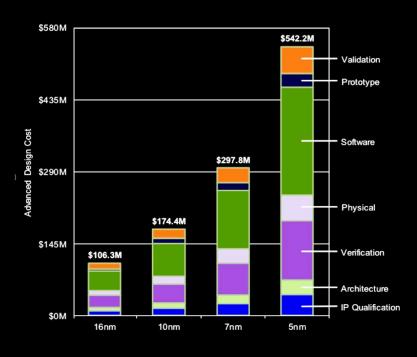

Complex Designs

+

**Higher Costs**

= Smaller window to "get it right"

# Introducing XploR

A platform to democratize system designs and accelerate silicon transformation

XploR brings EDA providers, tools, and infrastructure together

## Platform-driven development flow

Platform is pre-integrated

- XploR is an integrated ecosystem of products and solutions

- EDA providers to proactively integrate products and solutions

- EDA solution providers and product vendors to collaborate on XploR

- Customers and system companies to onboard at the highest level of integration

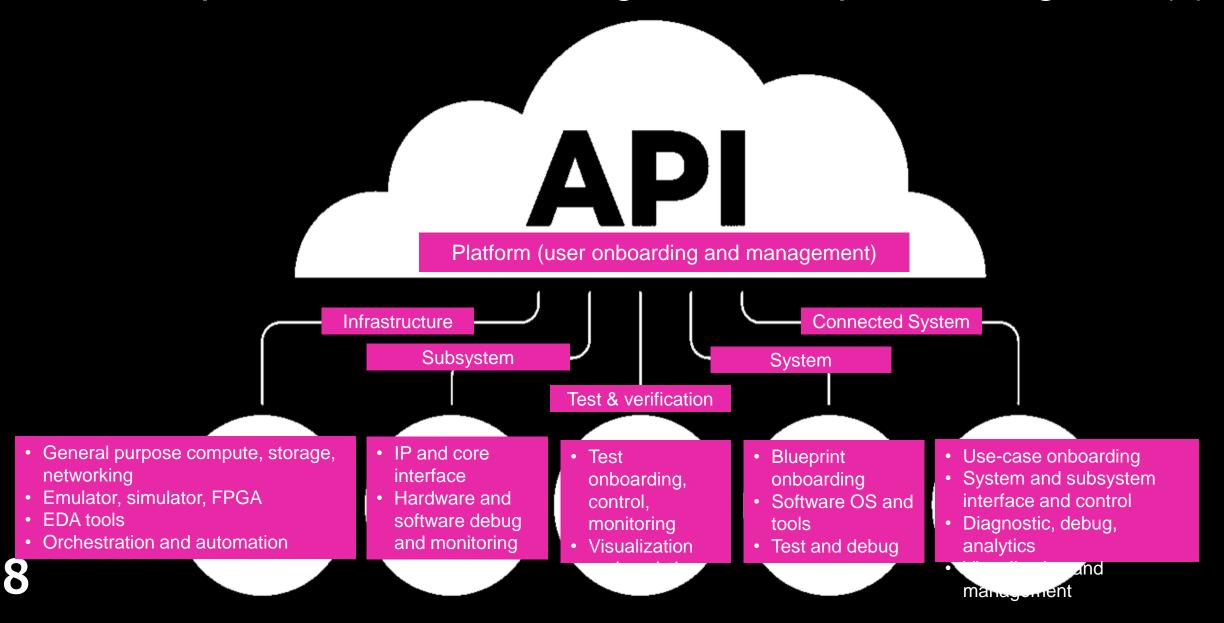

## Participants access and integrate with XploR through API(s)

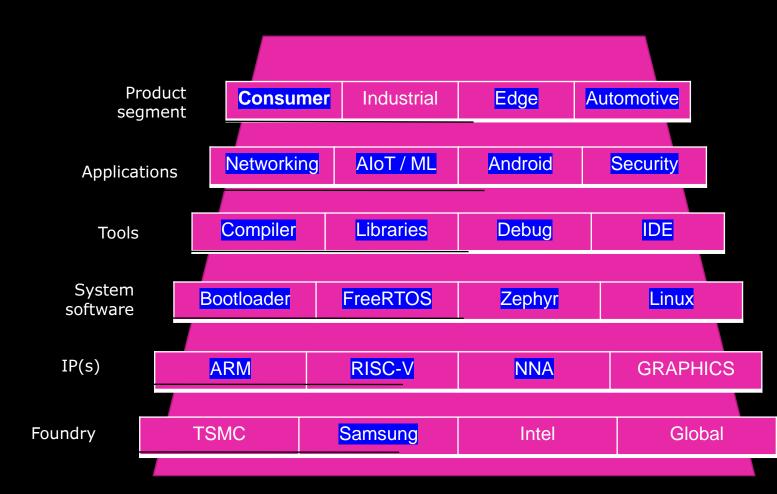

#### Feature: Availability of tools, IP(s) and designs at different level of

#### abstraction

Modular building blocks from EDA infrastructure to application-centric reference designs

Connected systems, digital twins

App-centric blueprints (5G, automotive, cybersecurity / networking)

Toolchain, SDK, runtime environment (Linux, Zephyr, FreeRTOS)

Core / peripheral IPs and subsystems

Simulator, emulator, FPGA, tools, test & verification solutions

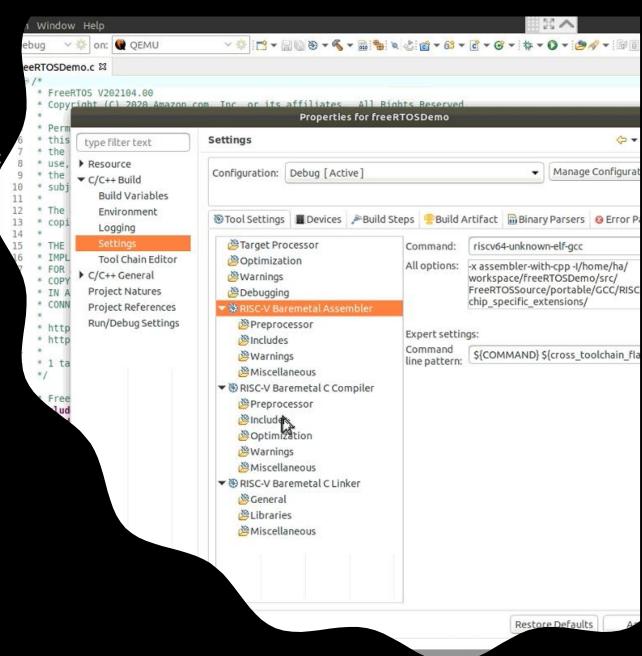

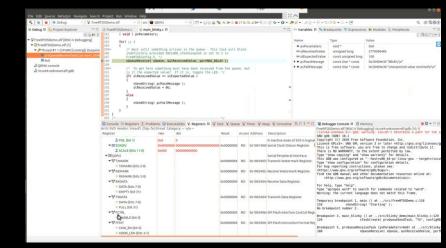

# Feature: Toolchain & IDE (XploR.studio)

Out-of-box development tools for heterogeneous SoC

system

Software toolchain & runtime environment

- GCC / LLVM

- Standalone C/C++ libraries

- Optimized and secure embedded Linux

#### Integrated development environment

- Eclipse (now) and Visual Code (coming) based

- Advanced debugging with support for:

- RTOS awareness (FreeRTOS, Zephyr, Embedded Linux)

- Trace, complex breakpoint

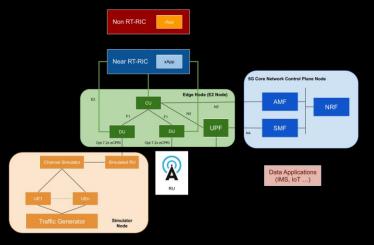

#### **Feature: Integration with Siemens EDA**

#### tools

**Graduate design through different stages** of development

**Applications** (Automotive, 5G, edge, IoT)

SW stack (toolchain, OS, debugger)

Core IPs (RISC-V, ARM)

Peripheral IPs

Higher order blueprints for growth verticals incorporating different architecture and IP:

- 5G ORAN 7.2x ODU

- Cybersecurity and high-speed networking

- AI / Edge inferencing

**Simulators** (Hycon)

**Emulation** (Strato)

Prototyping (proFPGA, Primo)

**ASIC**

simulators (Hycon, QEMU, Spike), and RTL simulators

RISC-V as well as heterogeneous ASIC with ARM and RISC-V

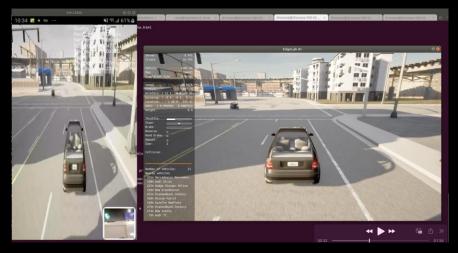

#### Feature: Integration with Siemens Automotive Digital Twin

Enable functional verification of software development for complex automotive designs

- Automotive digital twins for functional verification and software development at different stages of development.

- High-fidelity in-the-loop integration of compute and peripheral IP(s) (ADAS, sensors, AI / ML).

- Mixed-reality deployment of virtual models,

FPGA, and emulator execution engines.

#### **Available Variations:**

- Vehicle(s) to vehicle(s) communication with base station

- Vehicle(s) to phone communication over LTE infrastructure

- Infrastructure (streetlight) to vehicle(s) communication

#### Feature: Seamless migrate from individual to cloud to on-prem

Cloud-elastic, flexible environment for development and collaboration

#### Cloud

- + Verification / validation / digital twin

- Simulator QEMU, QuestaSim

- Prototyping Siemens Primo

- Emulator Siemens Veloce

- Digital Twin Siemens Pave360

#### On Prem

- + Private hosted

- Simulator QEMU, QuestaSim

- Prototyping Siemens Primo

- Emulator Siemens Veloce

- Digital Twin Siemens Pave360

#### Developers

IP qualification / prototyping / software dev

- Simulator QEMU, Spike

- AMD FPGA UltraScale

/ UltraScale+

- Intel FPGA Cyclone, Stratix, Agilex

AMD / Intel FPGA

#### Benefit: reduce and manage complexity of designs

Ready-made domain-specific design enables system companies to focus on their specific needs

IC-XploR lets developers onboard and execute blueprints (pre-packaged, pre-built core and IP(s), operating systems, apps, and dev) on hardware-assisted verification, and prototyping platforms.

XploR has customized and integrated these layers and packaged them in blueprints to help organizations:

- Reduce complexity with consistent tools and processes, and

- Manage complexity with encapsulation and abstraction

#### **Benefit: accelerate software development**

Shift left development and re-use tools and methodology horizontally

- Domain-driven designs and integration with Siemens EDA Automotive Digital Twin Platform to help contain and abstract complex subsystems.

- Consistent system software and tools to reduce DevOps variation at different stages of development.

- Access long-term impact in compatibility and performance of different cores and IPs to avoid surprises.

Simulation

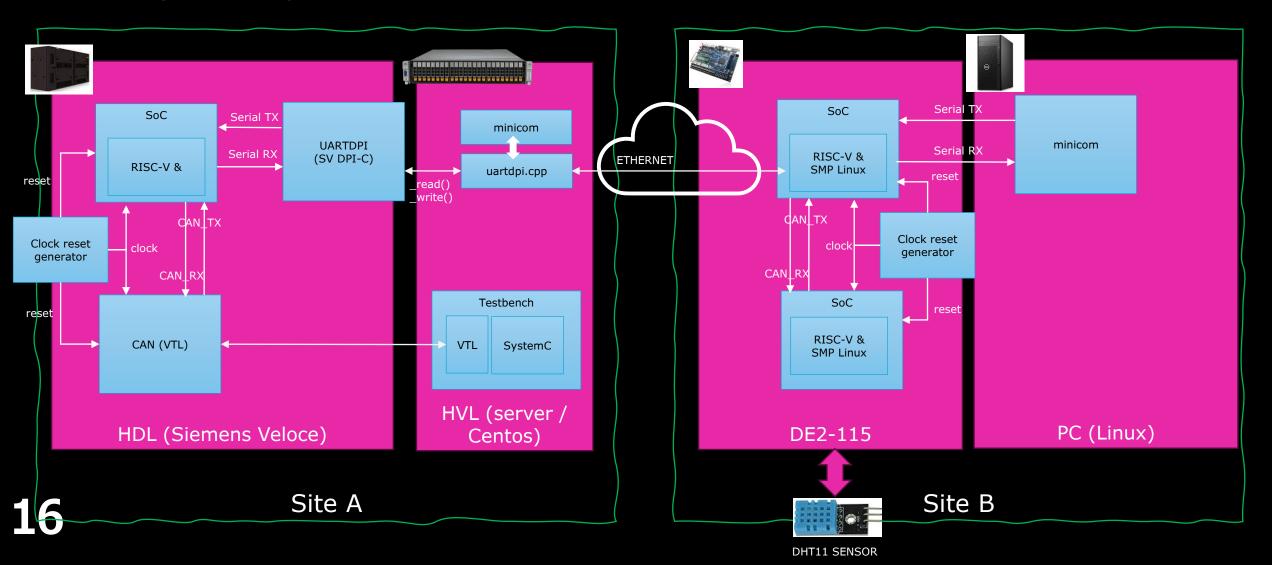

#### Example: multi-site, mix-mode collaborate development

A design consisting of different IPs, tools, and software environment from different development sites

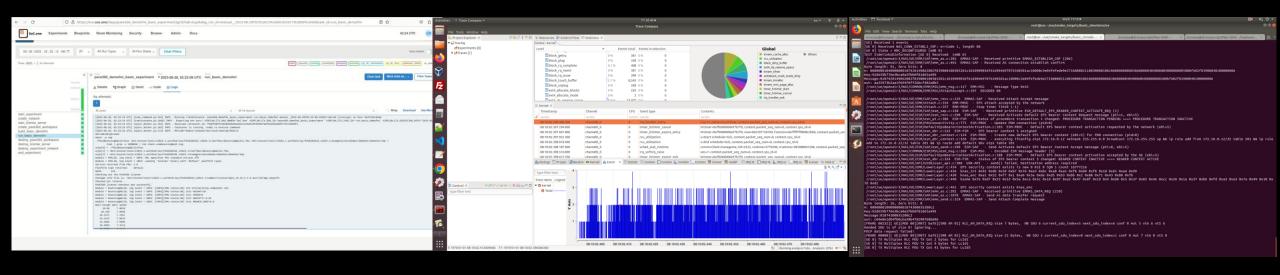

#### **Example: IP and Software enablement**

Heterogeneous SDK, toolchain, OS, profiles, blueprints, and reference designs

Our mission is to help transform ways organizations design and build vertically integrated digital products to deliver competitive advantage through development excellence.

Q & A

## About Us

- Global team of embedded and system developers over three continents since 1996.

- Among one of the pioneering companies to commercialize Linux for embedded

- Long history of enabling customer success in verticals ranging from communication, consumer devices, digital transformation, 5G / networking, defense, and medical

- SoC.one spin-off in 2019 to focus on RISC-V / heterogenous SoC design

### A legacy of our customers and partners from SoC.one

NORTHROP GRUMMAN

**THALES**

Industrial Technology Research Institute

Magnum

Lockheed

Raytheon

SONY

intel

CIRRUS

**⊗** Abo€om

BOEING

ANDLES (A)

**ZYXEL**

MICROCHIP