#### **UNITED STATES**

SAN JOSE, CA, USA FEBRUARY 27-MARCH 2, 2023

# Verification 2.0 – Multi-Engine, Multi-Run Al Driven Verification

Matt Graham – Verisium Product Engineering

cadence®

# Agenda

- EDA 2.0 and Verification 2.0

- What is AI?

- Al Opportunities in Verification

- Multi-Engine, Multi-Run Al-Driven Verification Solutions

- Real World Impact of Al-Driven Verification Solutions

# EDA 2.0 and Verification 2.0

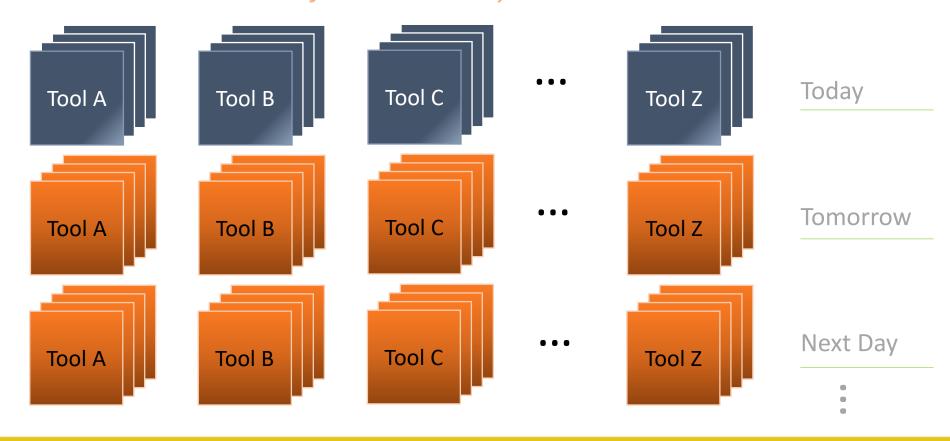

## A Generation of EDA 1.0

QoR QoR QoR QoR Capacity Capacity Capacity Capacity Runtime Runtime Runtime Runtime Tool C Tool A Tool B Tool Z e.g., P&R e.g., digital sim e.g., analog sim

# User's Perspective

# User's Perspective

Meet PPA Goals,

Meet Verification Quality Goals

# User's Perspective

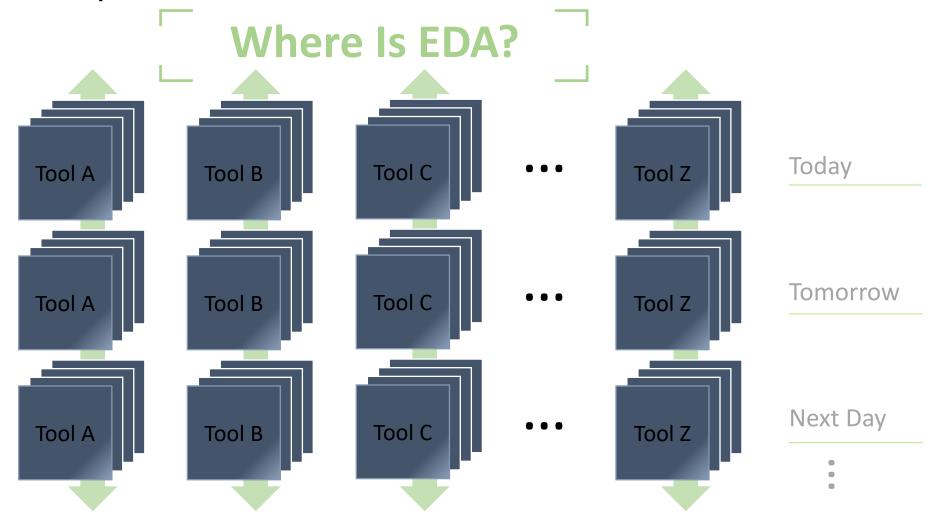

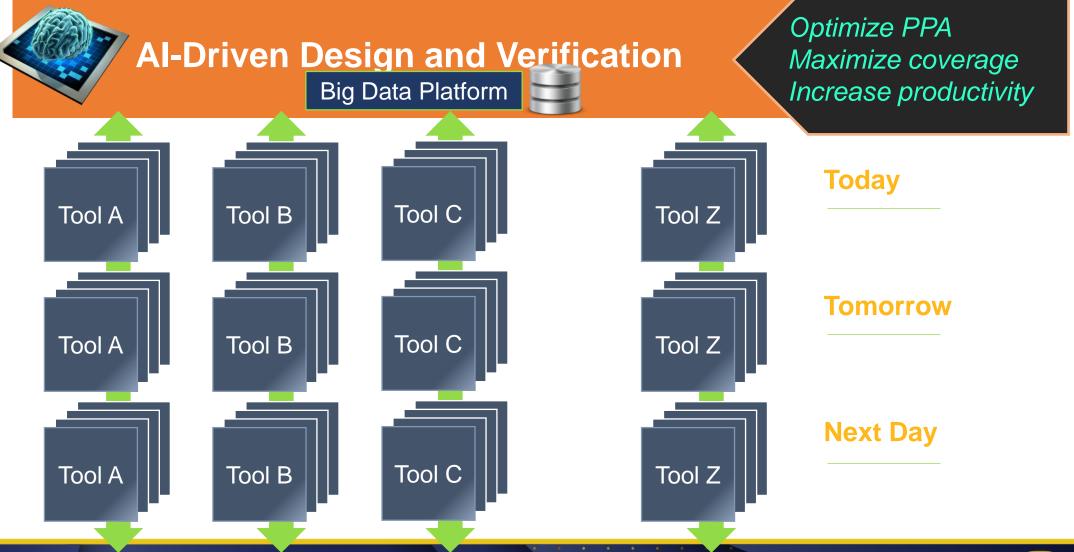

An Opportunity Exists - EDA 2.0

# What is Al?

Artificial Intelligence, Machine Learning and Big Data

# Artificial Intelligence

Intelligence demonstrated by machines, as opposed to natural intelligence, displayed by animals including humans

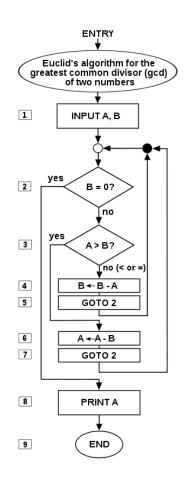

# Algorithm

A finite sequence of well-defined instructions, typically used to solve a class of specific problems or to perform a computation

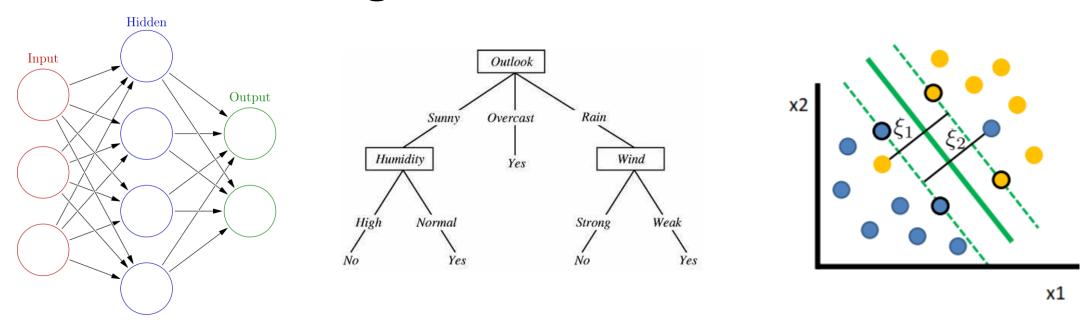

# Machine Learning

Machine learning (ML) is the study of **computer algorithms** that can **improve automatically** through **experience** and by **use of data**. It is seen as a part of artificial intelligence.

Artificial Neural Networks, Decision Trees, Support-Vector Machines, Genetic Algorithms

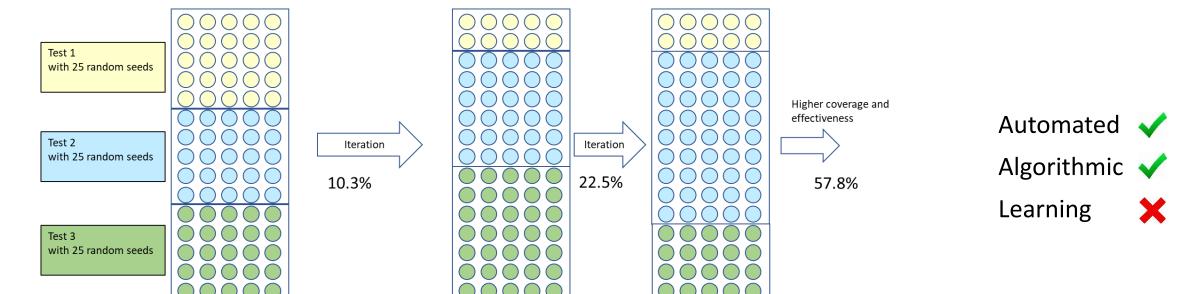

# Machine Learning or Automation?

Verisium<sup>™</sup> Manager Verification Management Test Weight Optimization

75 runs

75 runs

75 runs

# Practical AI in Engineering

• Improve the tool results.

Replace all the engineers.

• Make the engineers more efficient.

# Al Opportunities in Verification

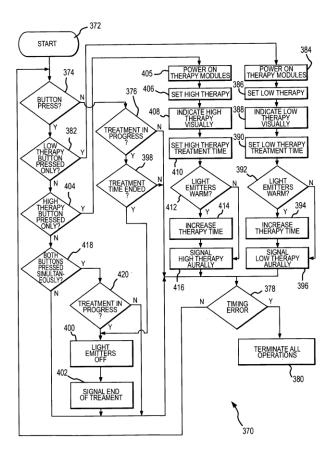

# Automation = Throughput

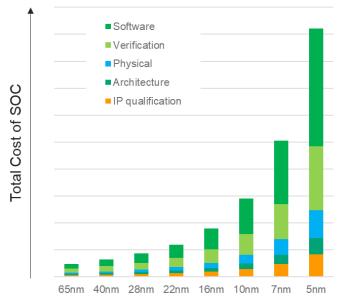

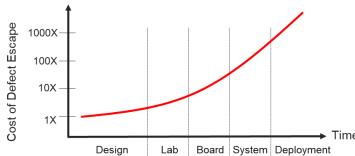

#### **Exponential Challenge**

ROI Mindset: Bug closure per \$ per day

**VERIFICATION THROUGHPUT**

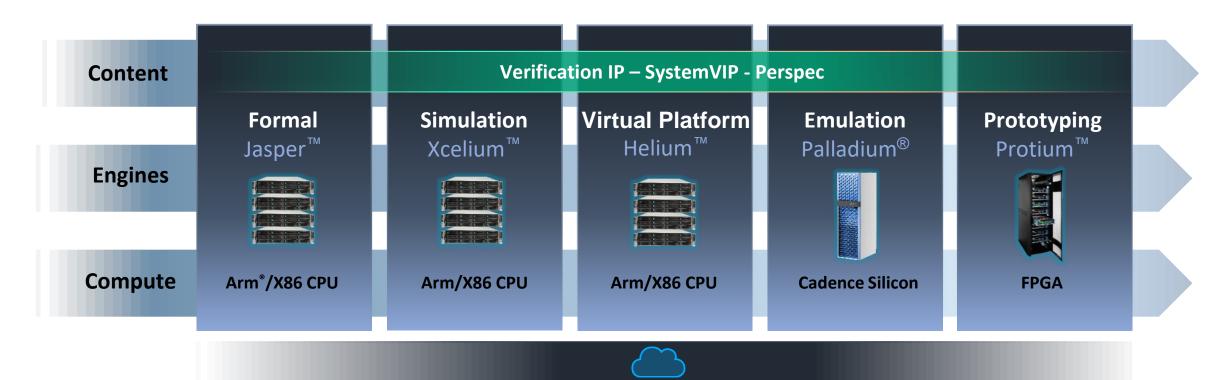

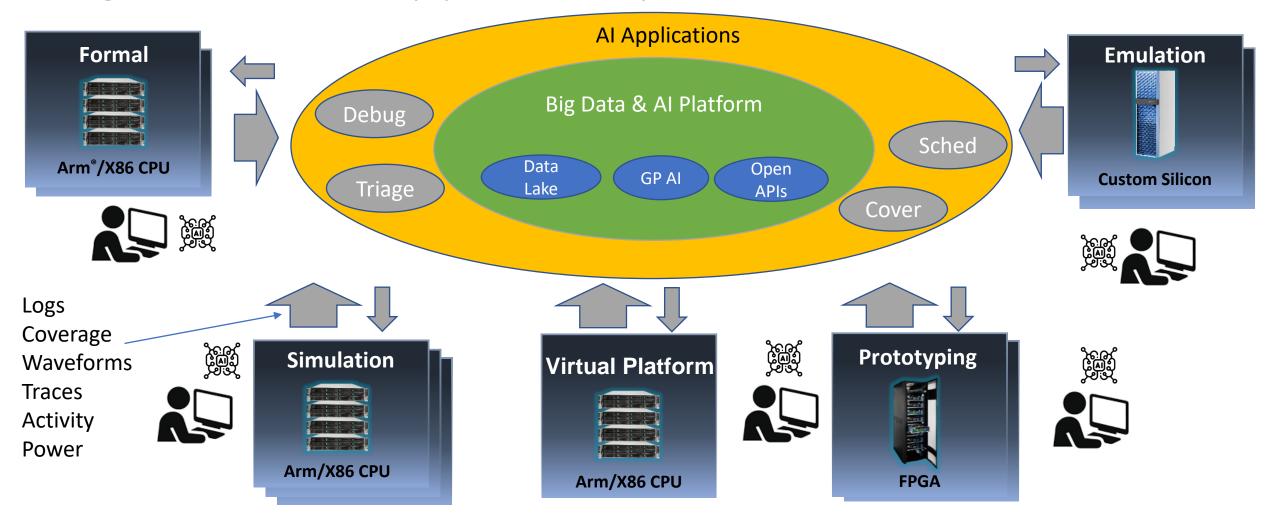

# Verification Work Horses

**Cloud Enabled**

# Verification Team Perspective

Meet Verification Quality Goals Find bugs - Close coverage

# Many Experts, Many Domains, Massive Data.

# Big Data & Al Opportunity

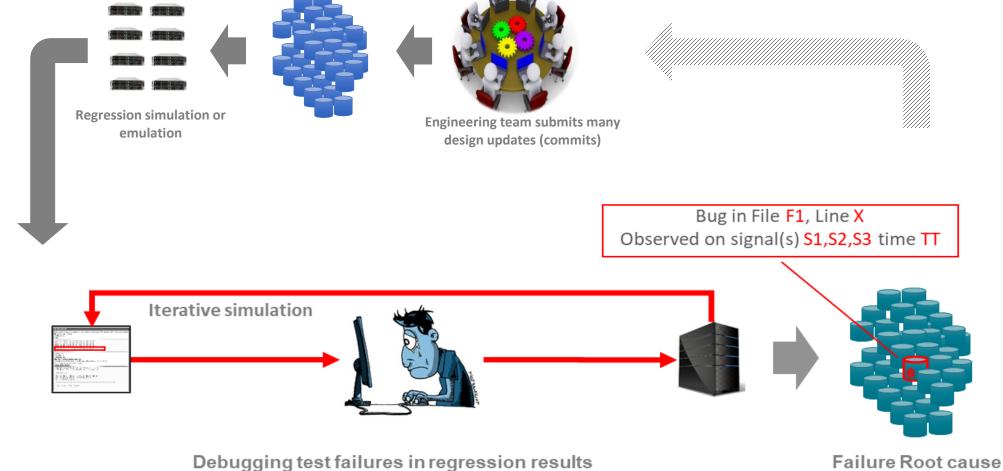

# Verification Challenge – SoC Debug

Where and how can AI be applied to problems like this?

Which failures are most critical?

Where is the bug?

What is the root cause?

**Bug Fix**

- SoCs integrate of hundreds of IP

- Each of the IP is constantly changing, evolving, improving

- Week to week, SoC-level testing results in a number of test failures

- Determining the root cause of the failure requires dozens of engineers and multiple weeks

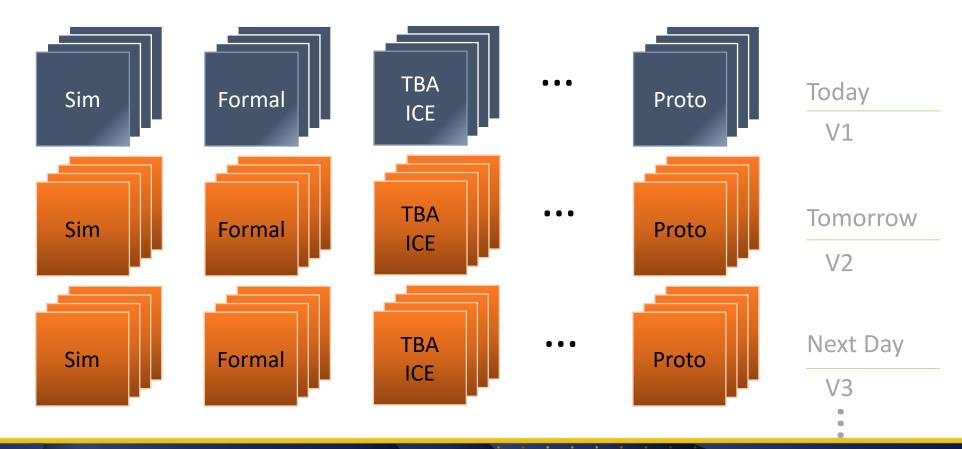

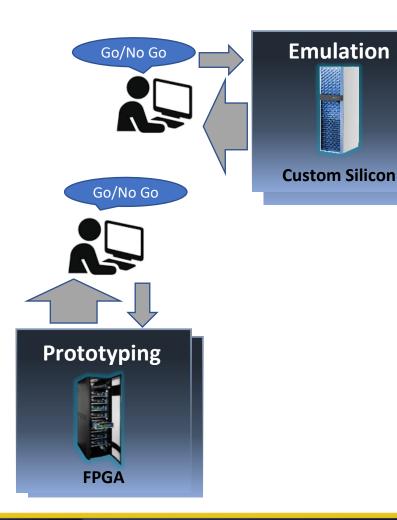

# Multi-Engine, Multi-Run Al Driven Verification Solutions

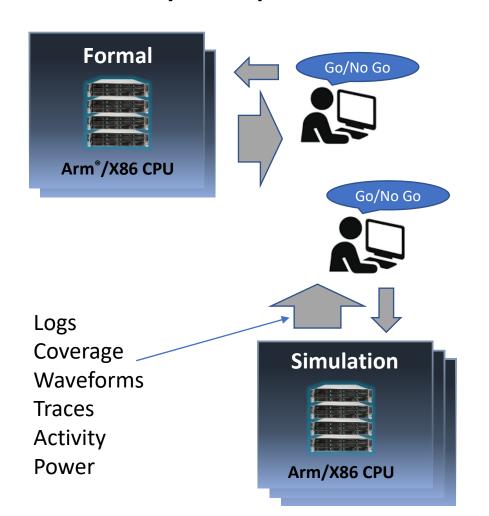

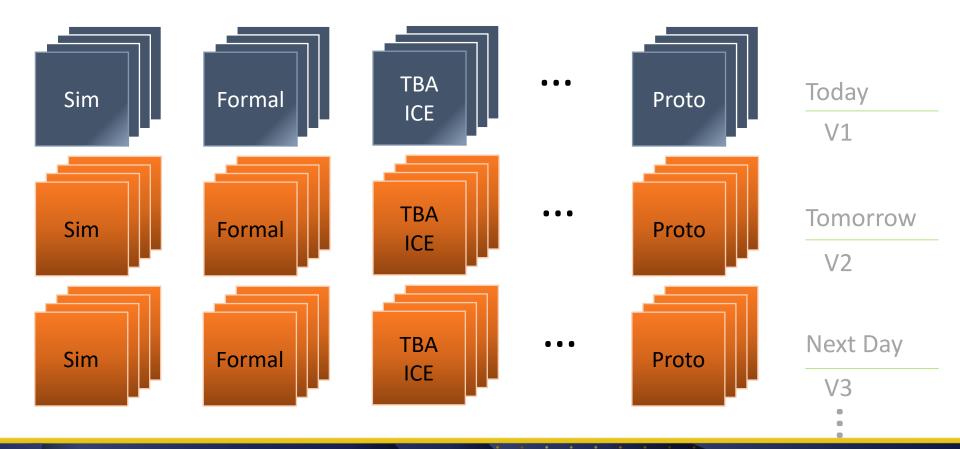

# Multi-Engine, Multi-Run Verification

Meet Verification Quality Goals Find bugs - Close coverage

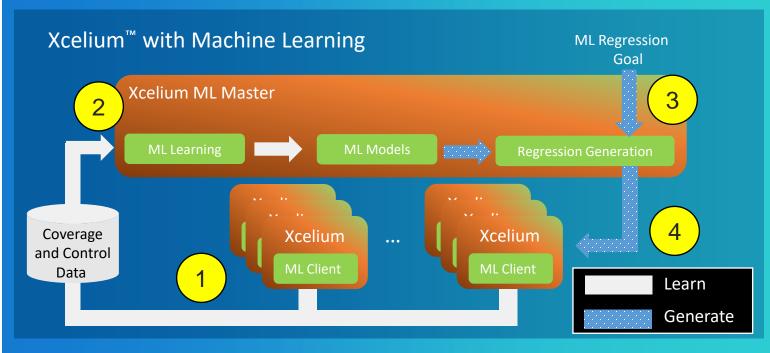

# Opportunities for ML in Simulation

#### **Regression Compression**

| Bins Covered | CPU Time   |

|--------------|------------|

| 393226       | 10052 cpuH |

| Bins Covered | CPU Time  | Regain | Compression |

|--------------|-----------|--------|-------------|

| 390528       | 1950 cpuH | 99.3%  | 5.1x        |

**ML** Regression

**Original Regression**

#### **Targeted Regression**

#### **Bug Hunting** / Coverage Closure

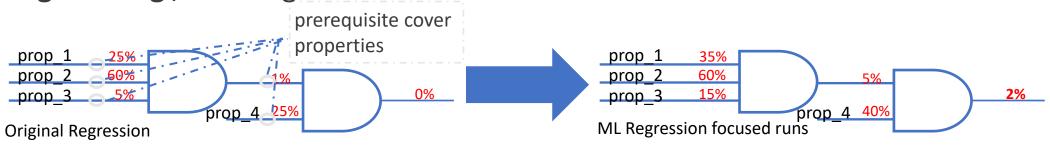

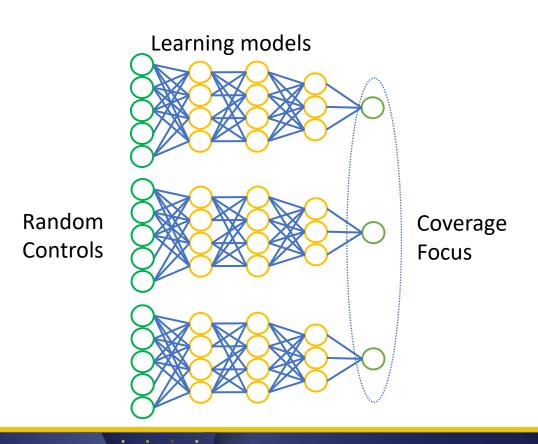

# ML for Coverage Closure

Synthesize tests to more efficiently hit coverage

Input Layer: random

control variables

**Hidden Layers**

Output Layer: coverage bin

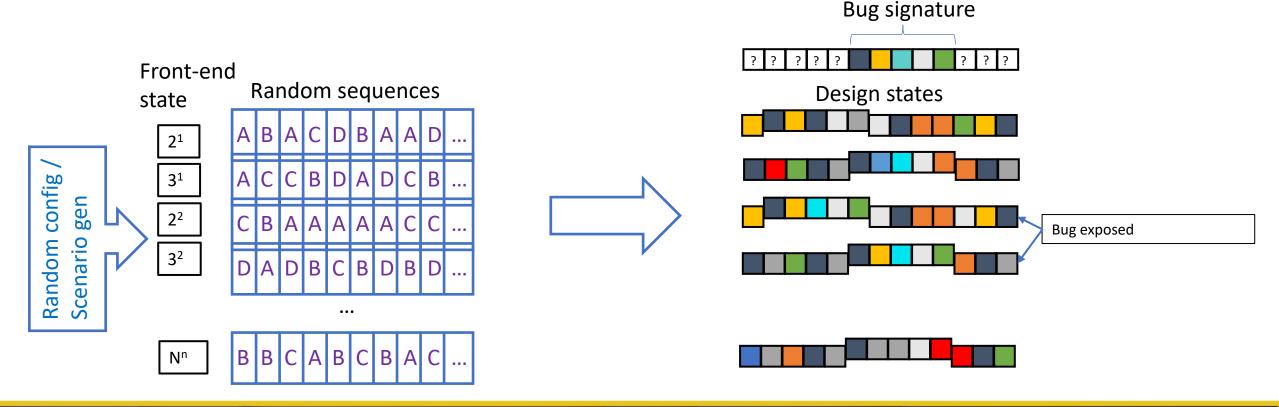

# Machine Learning for Bug Hunting

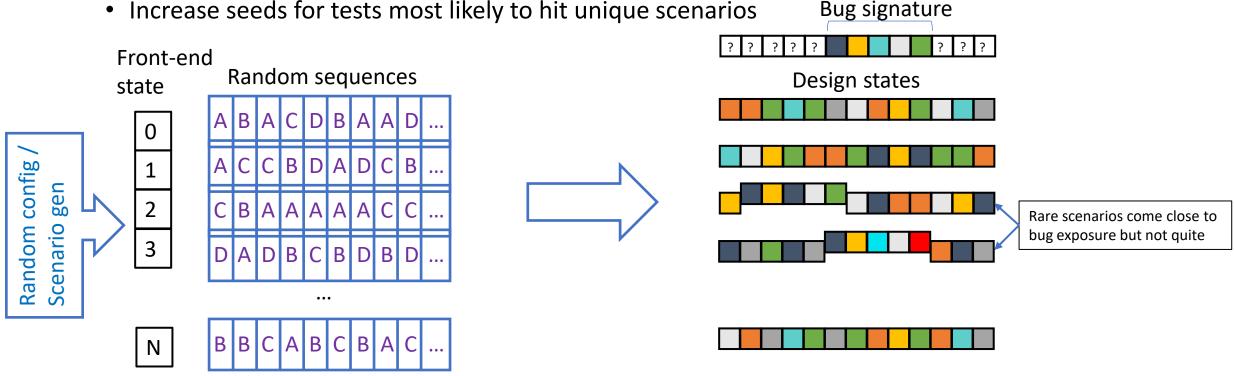

- Typical bug-hunting using randomized testbenches

- Once bug rate reaches some low threshold

- Fill CPU resources with random runs

- Increase seeds for tests most likely to hit unique scenarios

# Machine Learning for Bug Hunting (con't)

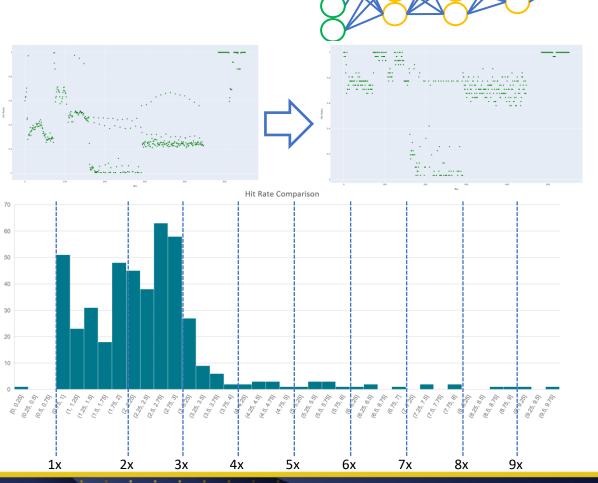

- Machine Learning bug hunting using randomized testbenches

- Focus on front-end states that magnify more rare conditions

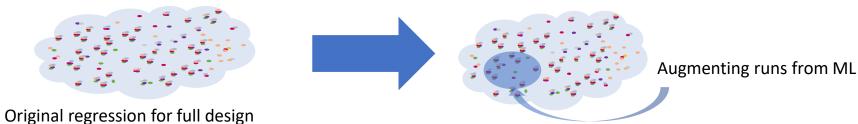

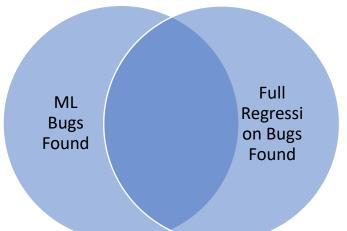

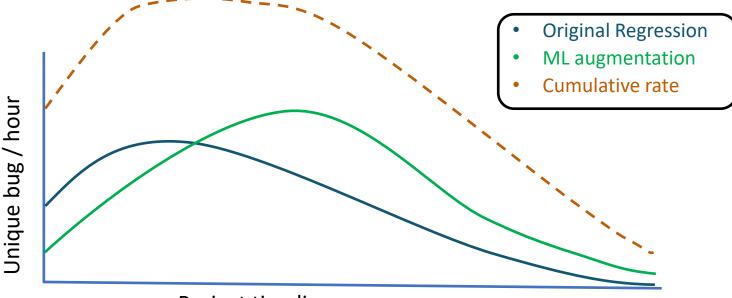

# Machine Learning for Bug Hunting (con't)

- Augment full regression with ML-generated runs

- The ML-generated regression will create higher percentage of more rare scenarios

- The bug rate of the ML runs (unique signature / cpuH) will typically be higher than the full regression

• Use in conjunction with the full regression until the full regression no longer finds

new bug signatures

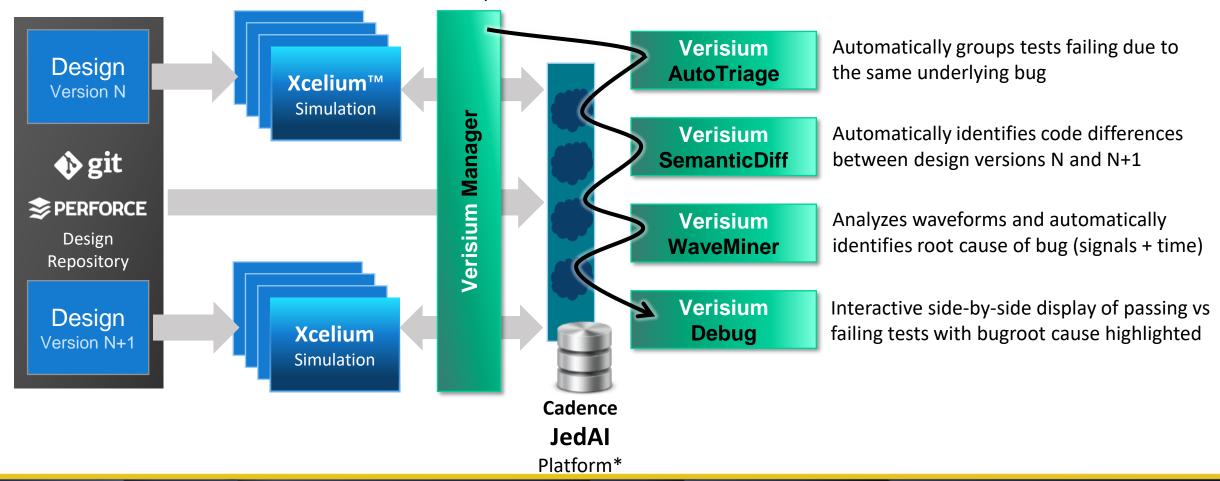

# Al Opportunity for Regression Debug

found

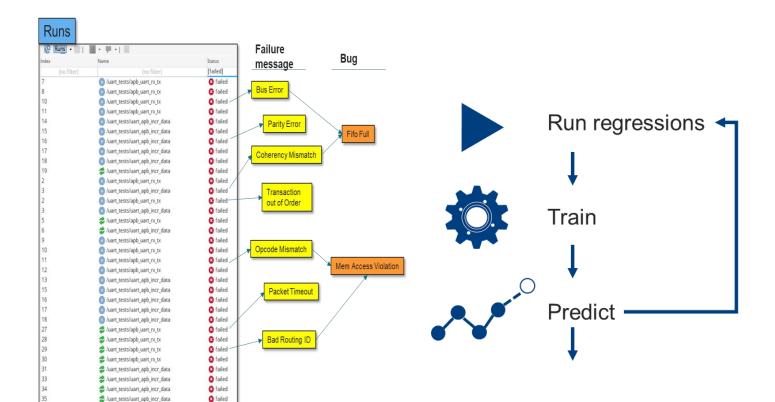

## Automated ML Bucketing of Regression Failures

- Problem Statement

- Manual failure analysis of regression is very costly and inefficient

- Solution

- Automate the failure analysis/classification

#### Bug: FIFO Full

Test3: Bus error

Test27: Parity Error

Test51: Mismatch

#### **Bug: Mem Access Violation**

Test16: Wrong Opcode

Test27: Packet Timeout

Test51: Bad Routing ID

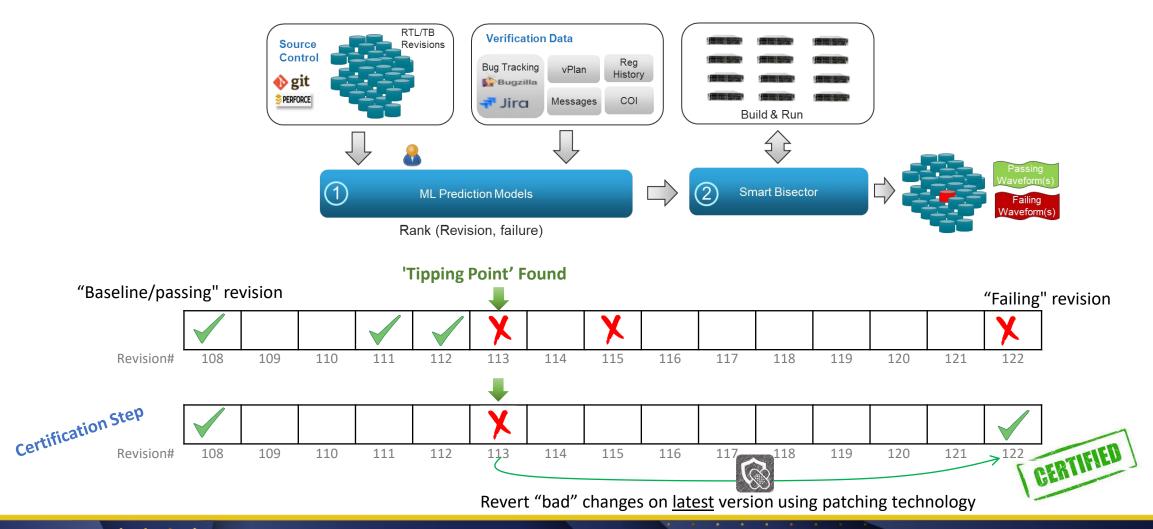

# Automatically Identify the Bad Change Set

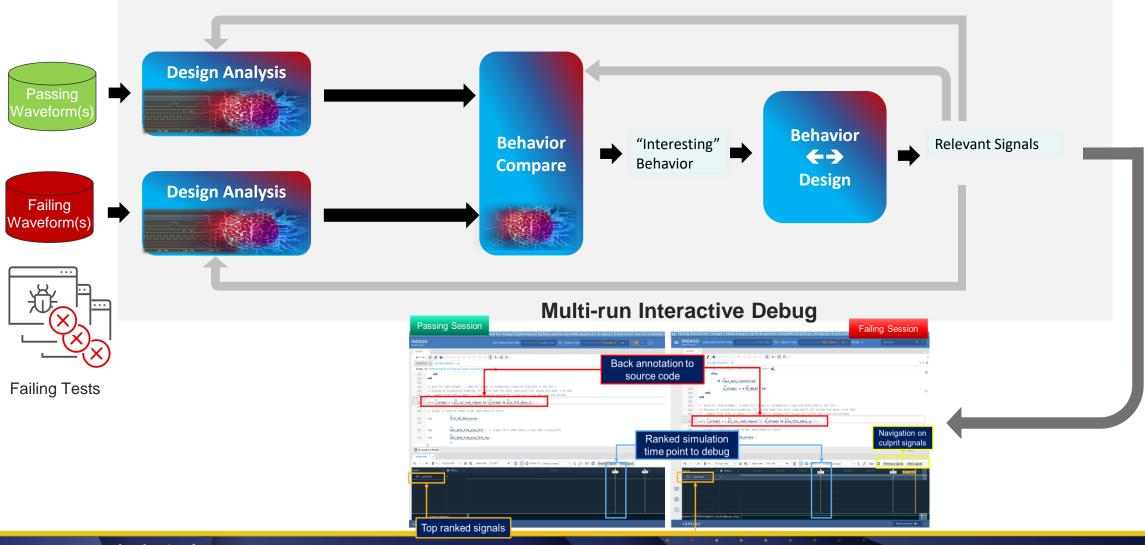

# Automated Deep Waveform Analysis

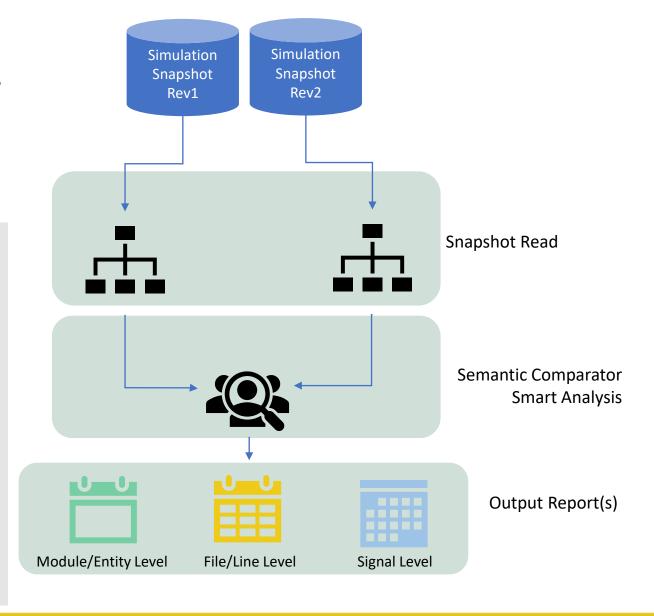

### Al Design Analysis

Identify and rank semantic changes between two RTL versions

Ignore harmless changes

Rank "complexity" of genuine logic changes

```

module cg (d, clk);

module cg (d, clk);

input d, clk;

input d, clk;

reg orig, clone, g_latch;

reg orig;

reg clone;

// Comments ..

reg g_latch;

wire w = orig ^ d;

wire w = orig ^ d;

wire gclk = clk & g latch;

wire gclk = clk & g latch;

always @(clk or w)

always @(clk or w)

if (clk) g_latch <= w;

if (~clk) g latch <= w;

always @(posedge gclk)

always @(posedge gclk) clone <= d;

clone <= d;

always @(posedge clone) orig <= d;

always @(posedge clone)

fd: assert property (

orig <= d;

@(posedge clk) orig == clone

fd: assert property (

@(posedge clk) orig == clone

Endmodule

endmodule

```

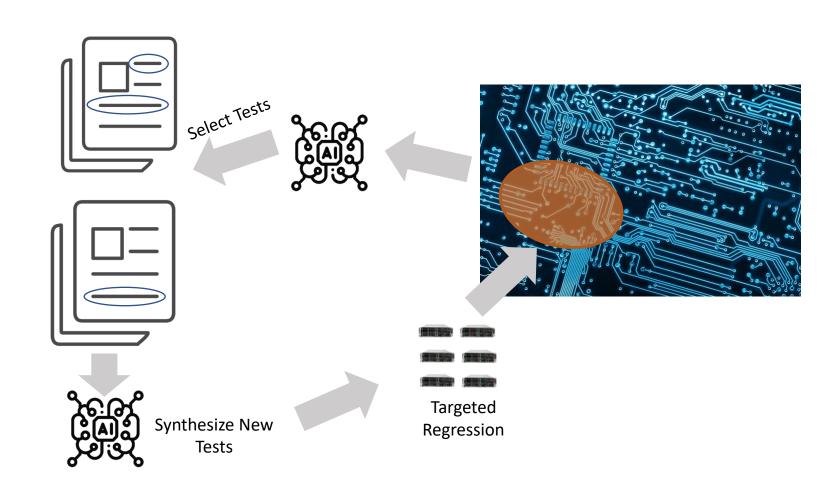

# Al Opportunity for Workload Optimization

- Automatically identify target features

- Disruptive changes

- Low coverage

- High bug potential

- Select or synthesize stress tests

- Optimize regression time and resource.

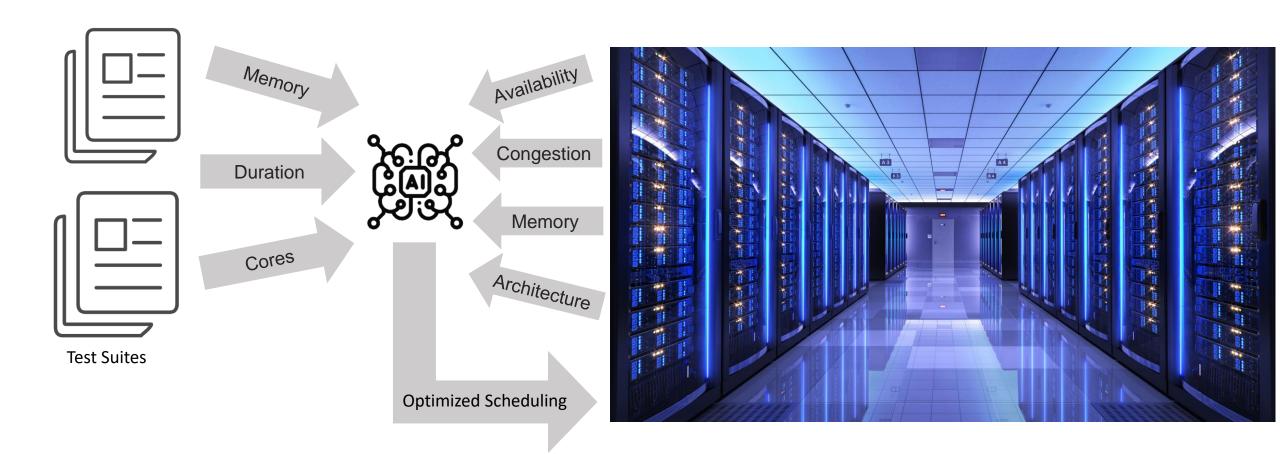

# Al Opportunity for Resource Optimization

# Real World Impact of Al Driven Verification Solutions

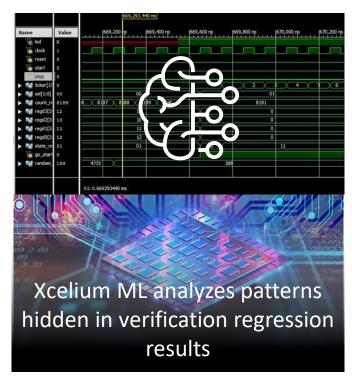

## Xcelium-ML

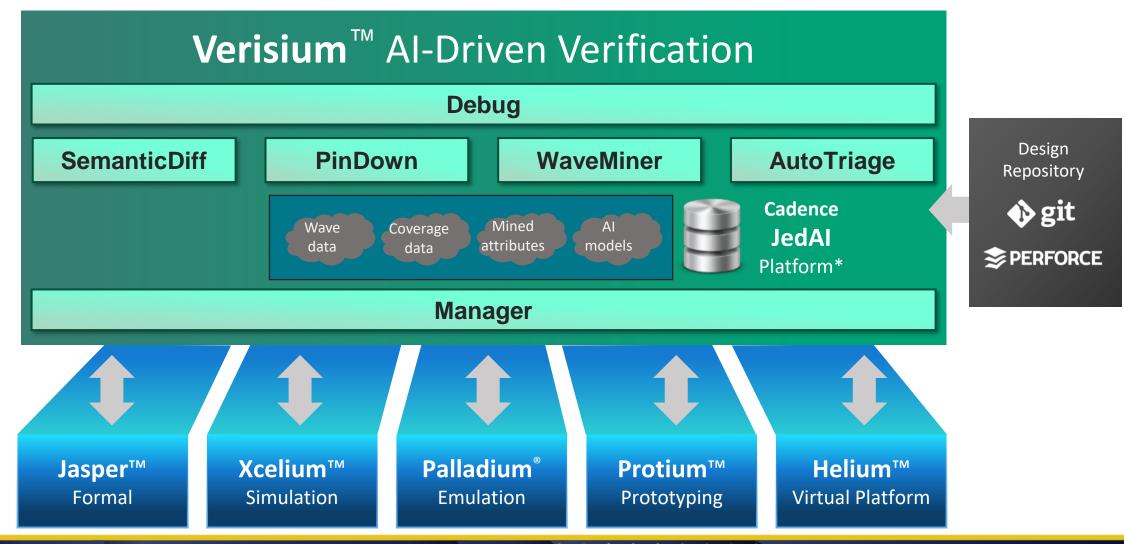

### Verisium Platform

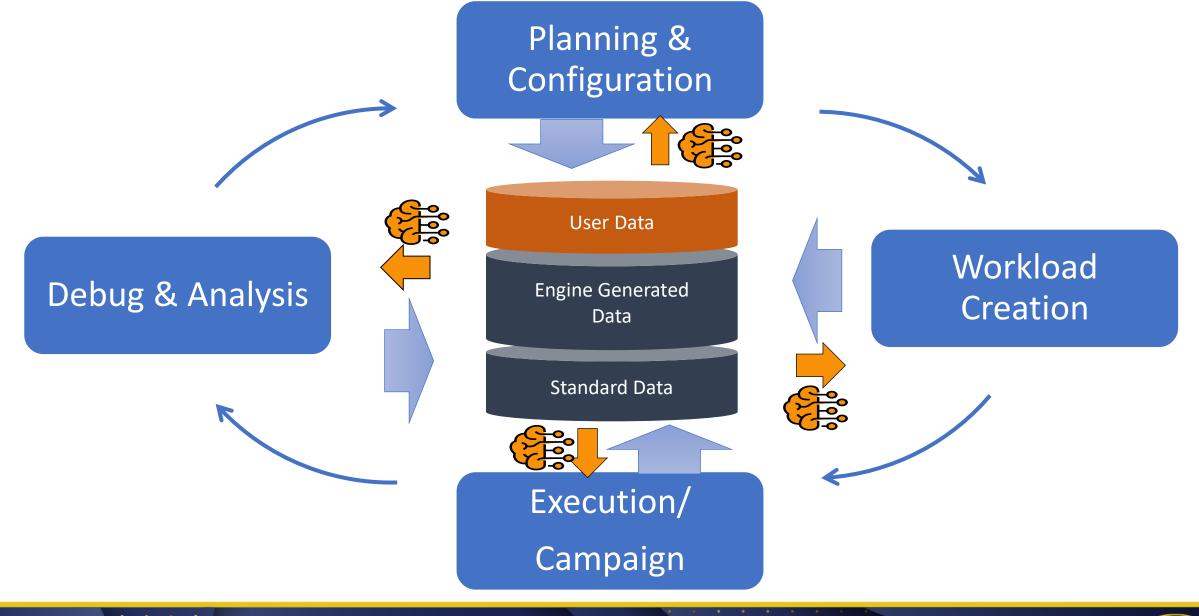

# Verisium Platform in Action

Al-driven submission of tests to compute farm

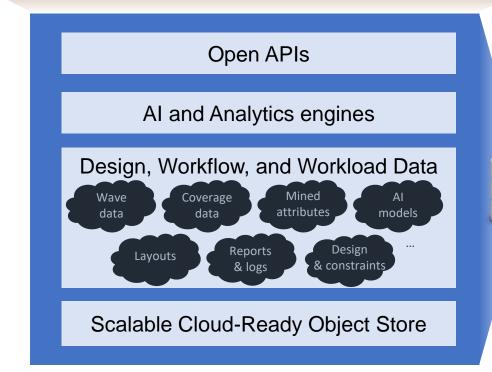

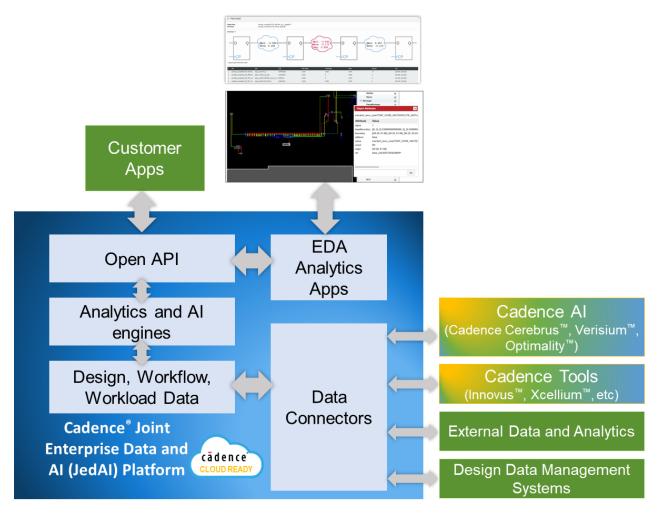

# Cadence Joint Enterprise Data and AI (JedAI) Platform

Al-driven Verification Al-driven Implementation

• • •

Al-driven System Analysis

## Cadence<sup>©</sup> JedAl Platform

- Cross-domain big data EDA platform to facilitate Al and analytics deployment delivering productivity multiplier

- Highly scalable, distributed, secure infrastructure

- Open industry-standard user interface and scripting environment optimized for Cadence tools

# SoC Debug with Verisium Platform

Manual Flow

Verisium<sup>™</sup> Al-Driven Flow

Potential for massive improvement in debug productivity

# Questions

- Thanks for joining!

- Feedback and offline questions:

- magraham@cadence.com