2023 DESIGN AND VERIFICATION TH DVCCONFERENCE AND EXHIBITION

#### UNITED STATES

SAN JOSE, CA, USA FEBRUARY 27-MARCH 2, 2023

### **Pushbutton Complete IP Generation**

Freddy Nunez

© Acceller a Systems Initiative

SYSTEMS INITIATIVE

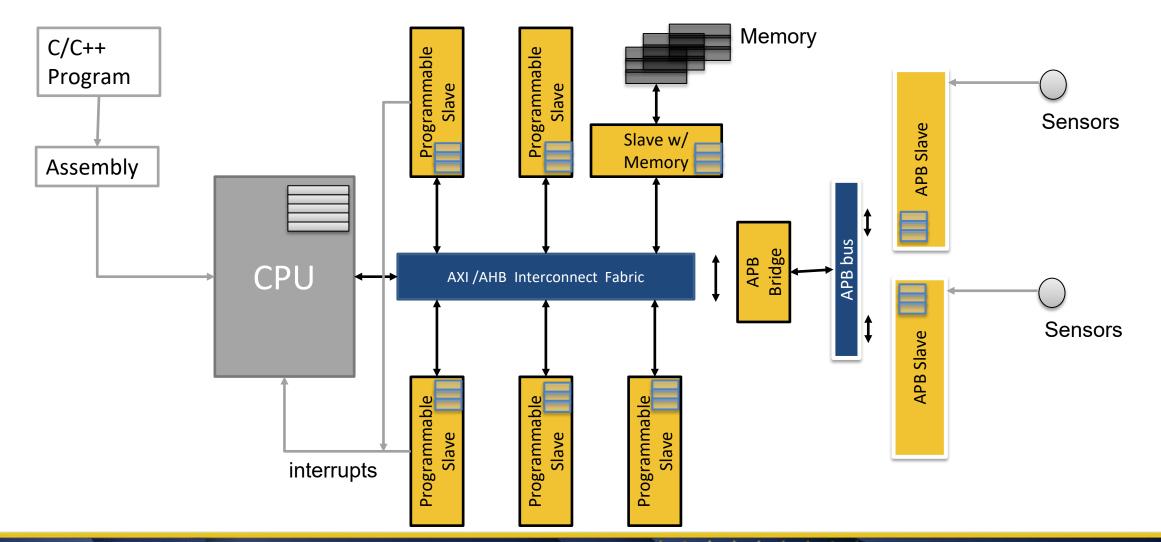

# Typical Chip Design

- Hardware of the SoC is designed by HW team

- But used by

- Verification/Emulation team

- Firmware team

- Validation team

- Software team

- How does the software interact with the IPs?

- Through the Hardware Software Interface (HSI)

- Hardware is at the core and software API is around it

- Device drivers (part of the HSI) are tedious to create

- They are written in C and Assembly

## Introduction to a Typical SoC

# **Challenges Faced**

- Design challenges

- Too much data

- Even small changes in data causes havoc

- Significant source of bugs

- Reusing IP

- Verification/Validation challenges

- Duplication of work across teams

- Rise in complexity of designs

- Inability to create same debug environment for multiple platforms

- Mismatch in specification and implementation

# Challenges Faced - Cont'd

- SOC design companies

- Increasing demands of design complexity and design performance

- Combining automation with flexibility to accommodate changes in sub-systems across applications

- Driving down the cost of design for a better ROI

- Shrinking market windows

- Boosting productivity of design teams to meet shorter market windows

# An Ideal Solution

- Ease of generation

- Generated code should not be encrypted

- Should provide appropriate error messages

- Ability to reuse IPs

- Customizing the designs

- Configuring the designs

- Easy mechanism for generating IP blocks

- Ability to handle different bus protocols

- Handling metastability of multi clock domain designs

- Design must be functionally safe and secure

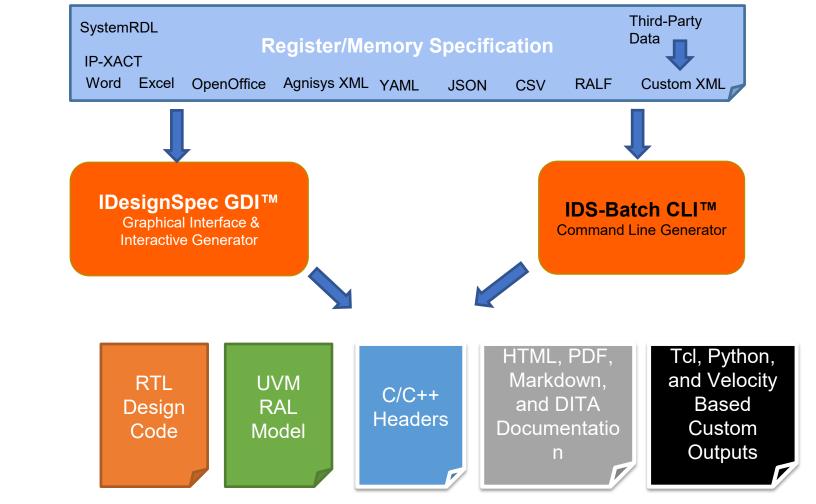

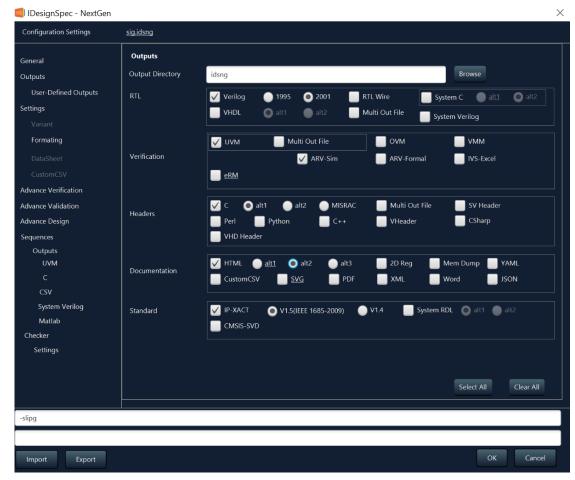

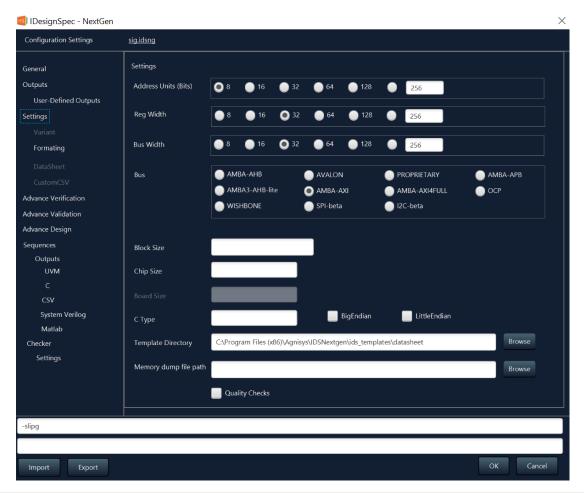

#### IDesignSpec $\neq$ GDI & CLI Data Flow

Generated Bus interfaces AMBA APB AMBA AHB AMBA AHB-Lite AMBA AXI-Lite AMBA AXI-Lite AMBA AXI5-Lite TileLink Avalon Wishbone

SYSTEMS INITIATIVE

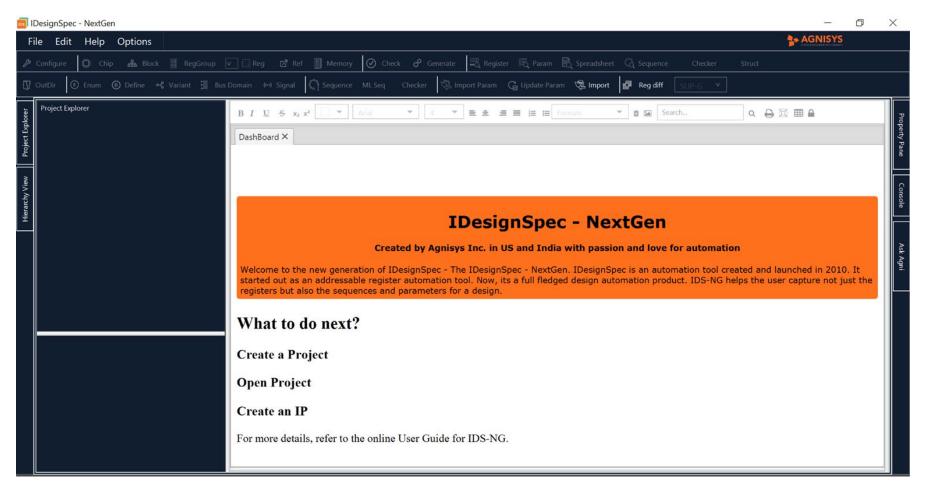

# **Designing IPs**

# Designing IPs - Cont'd

Addressable Register specification

|            | _ F | Re | gist                         | er vi             | ew:        |         |       |       |             |           |                         |                          |                    |                        |      |           |

|------------|-----|----|------------------------------|-------------------|------------|---------|-------|-------|-------------|-----------|-------------------------|--------------------------|--------------------|------------------------|------|-----------|

|            | 1   | DS | Regis                        | ster Sp           | ecificatio | n       |       |       |             |           |                         |                          |                    |                        |      |           |

|            |     |    |                              |                   | n          | eg_name |       |       |             |           |                         | 32                       | address<br>default |                        |      | C Header, |

| Define     |     |    | -                            | erties<br>ription |            |         |       |       |             |           |                         |                          |                    |                        |      | Misra-C,  |

| user 🚽     |     |    | and the second second second | name<br>pkt32     |            |         | 0     |       | h/w 🌻<br>ro |           | lescripti<br>a 32 bit p | i <b>on</b><br>packet fi | eld.               | \$                     |      | C Tests,  |

| registers  | S   | pr | ead                          | lshe              | et viev    | /:      |       |       |             |           |                         |                          |                    |                        |      | >-<br>    |

| ' settings |     | •  |                              |                   | ecificatio |         |       |       |             |           |                         |                          |                    | Open IDS Temp          | late | SystemRDL |

|            |     |    | Α                            | В                 | С          | D       | E     |       | F           | G         |                         | Н                        | I                  | J                      | ^    | Register  |

|            |     | 1  | chip                         | block             | register   | width   | field | sw ad | ccess       | hw access | field                   | d defau                  | lt bits            | description            |      | •         |

|            |     | 2  |                              |                   | reg_name   | 32      |       |       |             |           |                         |                          |                    |                        |      | Sequences |

|            |     | 3  |                              |                   |            |         | pkt32 | rw    |             | ro        |                         |                          | 31:0               | a 32 bit packet field. |      | •         |

|            |     | 4  |                              |                   |            |         |       |       |             |           |                         |                          |                    |                        |      |           |

SYSTEMS INITIATIVE

## Designing IPs in IDS-NG - Cont'd

#### Sample specification

| Board ethernet_ip   |                    |                   |                  |                        |            |                | S                     | equ             | en              | ce         | Vie         | <b>SN</b> | /        |                           |                 |                                            |                                                   |                |       |      |

|---------------------|--------------------|-------------------|------------------|------------------------|------------|----------------|-----------------------|-----------------|-----------------|------------|-------------|-----------|----------|---------------------------|-----------------|--------------------------------------------|---------------------------------------------------|----------------|-------|------|

| equence name        |                    | ip                |                  |                        |            | description    |                       |                 |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

| eq_name1            |                    |                   | et_ip_core.idsn  | ıg                     |            |                | ·                     |                 |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

| ranna anta          | -                  |                   |                  |                        |            |                |                       |                 |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

| arguments<br>arg1   | DashBoard ethernet | t_ip_core.idsng × |                  |                        |            |                |                       |                 |                 |            | Par         | 'ai       | m        | Vie                       | <b>W</b>        |                                            |                                                   |                |       |      |

|                     |                    |                   |                  |                        |            |                |                       |                 |                 |            | MI          | MI        | 11       |                           |                 |                                            |                                                   |                |       |      |

| constants<br>const1 |                    |                   |                  |                        |            |                |                       |                 |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

| onsti               | Address            | Register<br>Name  | bit bit bi<br>31 | it bit bit bit bit bit | bit bit bi | it bit bit bit | bit bit bit b         | t bit bit bit   | bit   bit   bit | bit bit    | bit bit bit |           |          |                           |                 |                                            | _                                                 |                |       |      |

| ariables            | 00                 |                   | Dashi            | Board ethernet_ip_core | idsng ×    |                |                       |                 |                 |            |             | S         | nr       | ead                       | lshe            | et V                                       | iew                                               |                |       |      |

| ar1                 | + 🗹 🕇 📙            | OURCE             |                  | 20 D 1 / 0 10          |            |                |                       |                 |                 |            |             |           | <b>P</b> | 949                       |                 |                                            |                                                   |                |       |      |

| ommand              | VA7                | -                 |                  | OS Register Specific   |            |                |                       |                 |                 |            |             |           |          |                           | Open IDS Ten    | plate                                      |                                                   |                |       |      |

| vrite               | 0x8                | INT_MASK          |                  | A                      | В          | С              | D                     | E               | F               | G          | Н           | Ι         |          |                           | l               | - â l l                                    |                                                   |                |       |      |

| vrite               | 0xC                | INT_FIFO          |                  | 1 enum name            | enum       | enum desc      | mneme                 | nic             |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

|                     | 0x10               | USER_Reg          |                  |                        | value      |                | name                  |                 |                 |            |             |           |          |                           |                 |                                            | <b>n</b> -                                        |                |       |      |

|                     | 0x14               | REG_FILE          |                  | 2 INT_Source_enum      | 0525599    | re DashBo      | ard ethernet_         | ip_core.idsng × |                 |            |             |           |          |                           |                 |                                            | Ке                                                | egist          | сег у |      |

|                     | 0x14               | IPGT              |                  | 3 INT_Source_enum      | 0x1        | re             | De l'atar C           | 15              |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

|                     | 0x18               | IPGR1             |                  | 4 INT_Source_enum      | 0x2        | tra            | Register S            | ecification     |                 |            |             |           |          |                           |                 |                                            |                                                   |                |       |      |

|                     | 0x1C               | IPGR2             |                  | 5 INT_Source_enum      | 0x3        | tra            | 1                     |                 | Etherne         | value      |             |           |          | Annahistian               |                 | address on                                 |                                                   |                |       |      |

|                     |                    | end section       |                  | 6                      |            |                | define nan<br>Enable1 | e               |                 | value<br>1 |             |           |          | description<br>Enable equ |                 | 0                                          | ite                                               |                |       |      |

|                     | 0x5C               | REG_ARR           |                  | 7 define name          | define     | de             | Disable1              |                 |                 | 0          |             |           |          | Disable equ               |                 | 0                                          |                                                   |                |       |      |

|                     | 0x5C               | PACKETLEN         |                  |                        | value      | de             |                       |                 |                 | INIT So    | ource enum  |           |          |                           |                 |                                            |                                                   |                |       |      |

|                     |                    | end section       |                  | 8 Enable1              | 1          | Er             | mnemonic              | name            |                 | value      | Juice_enum  |           |          |                           | de              | cription                                   |                                                   |                |       |      |

|                     | 0x1000             | MEM               |                  |                        |            | 1              | RXC_dis<br>TXC_dis    |                 |                 | 0x0        |             |           |          |                           |                 | eive enable                                |                                                   |                |       |      |

|                     | 0x1000             | COLLCONF          |                  | 9 Disable1             | 0          | Di<br>0        | TXC_dis<br>TXC_enb    |                 |                 | 0x1<br>0x2 |             |           |          |                           |                 | eive disable<br>nsmit enable               |                                                   |                |       |      |

|                     |                    | end section       |                  |                        | -          | 0              | RXC_enb               |                 |                 | 0x3        |             |           |          |                           | tra             | nsmit disable                              |                                                   |                |       |      |

|                     | 0x2000             | TX BD NUM         |                  | 10                     |            |                | variant na            |                 |                 |            | value       |           |          |                           |                 |                                            |                                                   |                |       |      |

|                     | 0x2004             | CTRLMODER         | 1                | 1 chip                 | block      | re             | altera                | le              |                 |            | 1           |           |          |                           |                 | lescription<br>For Altera target           |                                                   |                |       |      |

|                     | 0x2008             | MIIMODER          |                  |                        | -          |                | xilinx                |                 |                 |            | 1           |           |          |                           | I               | or Xilinx target                           |                                                   |                |       |      |

|                     | 0.2000             | MINODER           |                  | 2 Ethernet             |            |                | 1.1                   |                 | Eth_bl          | al-1       |             |           |          |                           |                 | address 0x                                 | 0                                                 |                |       |      |

|                     |                    |                   | 1                | 3                      | Eth block  | -1             | 1.1                   |                 | Eur_on          | JCKI       |             |           |          |                           |                 | addressjox                                 |                                                   |                |       |      |

|                     |                    |                   |                  |                        | Lui_olock  |                | 1.1.1                 |                 | MODE            | R          |             |           |          |                           |                 | address  0x0<br>default   0x00             | 004000                                            |                |       |      |

|                     |                    |                   | < (              |                        | 1          |                |                       | name            |                 |            | s/v         | w         | h/w      | default                   | description     | delant j 0,000                             | 50A000                                            |                |       |      |

|                     |                    |                   |                  |                        |            |                | 010                   |                 |                 |            |             |           |          | doublet                   | {0:ignore smal  | _pkt; 1:accept_sm                          | all_pkt; }                                        |                |       |      |

| •                   |                    |                   |                  |                        |            |                | 16                    | DECEMALI        |                 |            |             |           |          | <u>_</u>                  | = Packets small | Packets 0 = Packet<br>er than MINFL ar     | s smaller than MINFL<br>e accepted.               | are ignored. 1 |       |      |

|                     |                    |                   |                  |                        |            |                | 16                    | RECSMALL        |                 |            | rw          | v         | ro       | 0                         | Enum defined f  | or this Field in its                       | description.                                      |                |       | )2   |

| era 🔪 🔒             |                    |                   |                  |                        |            |                |                       |                 |                 |            |             |           |          |                           | {0:dont pad sh  | ort frame; 1:pad                           | in field's Default value<br>short_frame; }Padding | enabled 0 =    |       |      |

| $\mathcal{D}$       |                    |                   |                  |                        |            |                | 15                    | PAD             |                 |            | rw          | v         | ro       | 1                         | Do not add pad  | s to short frames. I<br>ame length is equa | = Add pads to short fi                            | rames (until   |       | нв   |

|                     | /                  |                   |                  |                        |            |                |                       |                 |                 |            |             |           |          |                           |                 |                                            |                                                   | LINIT          | ED ST | ATTE |

### Designing IPs Cont'd

Addressable Register configuration

SYSTEMS INITIATIVE

### Designing IPs - Cont'd

#### Generated sample code

```

module sig ids#(

parameter bus width = 32,

parameter addr width = 2,

parameter block size = 'h4,

parameter [addr_width-1 : 0] block_offset = {(addr_width){1'b0}}

output reg name enb,

input [32-1 : 0] reg name fld in,

input reg_name_fld_in_enb,

output [31 : 0] reg name fld r,

input aclk,

input aresetn,

input [addr width-1 : 0] awaddr,

input awvalid,

output awready,

input [2 : 0] awprot,

input [bus width-1 : 0] wdata,

input wvalid,

output wready,

input [bus_width/8 - 1 : 0] wstrb,

output [1 : 0] bresp,

input bready,

output bvalid,

input [addr_width-1 : 0] araddr,

input arvalid,

output arready,

input [2 : 0] arprot,

output [bus width-1 : 0] rdata,

output rvalid,

input rready,

output [1 : 0] rresp

);

axi widget # (.addr width(addr width), .bus width(bus width) )axi (

. . .

);

. . .

assign wr slave select = ((slvwaddr[addr width - 1 : 0] >= block offset) & (slvwaddr[addr width - 1 : 0]

<= block offset + block size -1)) ? 1'b1 : 1'b0;

assign rd slave select = ((slvraddr[addr width - 1 : 0] >= block offset) & (slvraddr[addr width - 1 : 0]

<= block offset + block size -1)) ? 1'b1 : 1'b0;

dmodule

RTL

```

SYSTEMS INITIATIVE

####

rand ethernet\_ip\_tx\_pkt tx\_pkt; rand ethernet\_ip\_rx\_pkt rx\_pkt;

// Function : new

function new(string name = "ethernet\_ip\_block");

super.new(name, UVM\_NO\_COVERAGE);

endfunction

// Function : build

virtual function void build();

//define default map and add reg/regfiles

default\_map= create\_map("default\_map", 'h0, 4, UVM\_BIG\_ENDIAN, 1);

//TX\_PKT

tx\_pkt = ethernet\_ip\_tx\_pkt::type\_id::create("tx\_pkt");

tx\_pkt.configure(this, null, "tx\_pkt");

tx\_pkt.build();

default\_map.add\_reg( tx\_pkt, 'h0, "RW");

#### //RX\_PKT rx\_pkt = ethernet\_ip\_rx\_pkt::type\_id::create("rx\_pkt"); rx\_pkt.configure(this, null, "rx\_pkt"); rx\_pkt.build(); default\_map.add\_reg( rx\_pkt, 'h4, "RW");

lock\_model();

endfunction

endclass `endif

UVN

### Designing IPs - Cont'd

#### Generated sample code

```

#ifndef ETHERNET IP REGS H

#define ETHERNET IP REGS H

typedef union {

struct {

/* 31 SW=rw HW=rw 0x0 */

hwint start : 1;

/* 30:2 SW=rw HW=rw 0x0 */

hwint pkt : 29;

hwint parity : 2;

/* 1:0 SW=rw HW=rw 0x0 */

> bf:

hwint dw;

} ethernet ip tx pkt;

typedef union {

struct {

hwint start : 1;

/* 31 SW=rw HW=rw 0x0 */

/* 30:2 SW=rw HW=rw 0x0 */

hwint pkt : 29;

/* 1:0 SW=rw HW=rw 0x0 */

hwint parity : 2;

} bf;

hwint dw;

} ethernet ip rx pkt;

typedef struct {

ethernet ip tx pkt tx pkt;

ethernet ip rx pkt rx pkt;

} ethernet ip s;

#define ethernet ip s SIZE 0x8

#define ethernet ip tx pkt SIZE 0x4

#define ethernet ip rx pkt SIZE 0x4

#define ethernet ip s OFFSET 0x0

#define ethernet ip tx pkt OFFSET 0x0

#define ethernet ip rx pkt OFFSET 0x4

#define ethernet ip s ADDRESS 0x0

#define ethernet ip tx pkt ADDRESS 0x0

#define ethernet ip rx pkt ADDRESS 0x4

#define ETHERNET IP TX PKT START OFFSET 31

#define ETHERNET_IP_TX_PKT_START_MASK 0x80000000

#define ETHERNET IP TX PKT START INV MASK 0x7FFFFFFF

#define ETHERNET IP TX PKT START VALUE MASK 0x40000000

#define ETHERNET IP TX PKT START INV VALUE MASK 0xBFFFFFFF

#define ETHERNET IP TX PKT START SIZE 1

#define ETHERNET IP TX PKT START DEFAULT 0

.

endif /* ETHERNET IP REGS H */

* end */

```

CHeader

SYSTEMS INITIATIVE

#### Block : ethernet\_ip

UNITED STATE

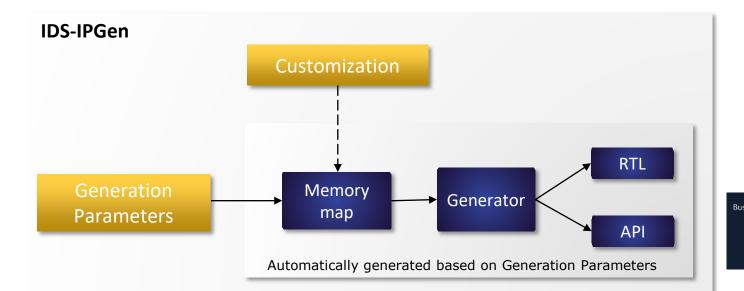

### Auto Generating Standard IPs

IDS-IPGen can also be used to automatically generate standard IPs (fully verified and validated) and their APIs, also provides add-in functionality of configurability and customizability

SYSTEMS INITIATIVE

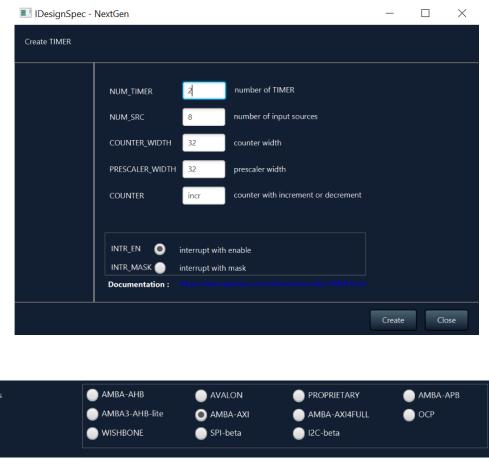

### Auto Generating Standard IPs - Cont'd

Register specification - Automatically generated by setting generation parameters

| timer                                            |                   | address                                                        |                                                                  |                      | control      |                       |         | address<br>default                                                                                          |                                                                                                                 | result                                 | addressdefault                                                                        |

|--------------------------------------------------|-------------------|----------------------------------------------------------------|------------------------------------------------------------------|----------------------|--------------|-----------------------|---------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|

| intr.irg per channel=true;                       | I                 |                                                                | count=2                                                          | 2.                   |              |                       |         | default                                                                                                     | rtl reg_enh=false:resetsigns                                                                                    | ll=result_reset%d:0:sync:low;count=2;  | defauit                                                                               |

| Description.                                     |                   |                                                                | Descrip                                                          |                      |              |                       |         |                                                                                                             | Thireg_eno Taise,resetsigna                                                                                     | in result_reserved.o.syne.tow,count 2, |                                                                                       |

|                                                  |                   |                                                                | bits 🖨                                                           |                      | € s/w        | <b>≜</b> h/w <b>≜</b> | default |                                                                                                             | bits 🗘 name                                                                                                     | ♦ s/w ♦ h/w ♥ defat                    | alt description                                                                       |

|                                                  |                   |                                                                |                                                                  |                      |              |                       | default | 1:- Enables the timer block or calculations 0:- Disables                                                    |                                                                                                                 |                                        | Stores the counting information depending upon the                                    |

| define name 🜲 value                              | 🗘 de              | scription 🗢 private                                            | 0                                                                | en                   | rw           | ro                    | 0       | the timer block                                                                                             | 31:0 data                                                                                                       | ro wo 0                                | selected modes.                                                                       |

| \$NUM_TIMER 2                                    |                   | 1                                                              | 2:1                                                              | mode                 | rw           | ro                    | 0       | 00: running mode 01: Periodic mode with source<br>enable 00: periodic mode without source 11: reserved      |                                                                                                                 |                                        |                                                                                       |

| \$NUM_SRC 8                                      |                   | 1                                                              |                                                                  |                      |              |                       |         | Legal values for running mode 000: high level 001:                                                          |                                                                                                                 |                                        |                                                                                       |

| \$COUNTER_WIDTH 32                               |                   | 1                                                              | 5:3                                                              | event sel            | rw           | ro                    | 0       | low level 010: between two high edges 011: between                                                          |                                                                                                                 | prescaler                              | address<br>default                                                                    |

| \$PRESCALER_WIDTH 32                             |                   | 1                                                              | 5.5                                                              | event_ser            | 1.00         | 10                    | ľ       | two low edges Legal values for the Periodic Mode<br>100: Posedges 101: negedges 110: both edges             |                                                                                                                 | prescaler                              | default                                                                               |

|                                                  |                   |                                                                |                                                                  |                      |              |                       |         | To select the source on which measurement will be                                                           | count=2;<br>Description                                                                                         |                                        |                                                                                       |

|                                                  |                   |                                                                |                                                                  |                      |              |                       |         | performed. These act as a counter enable signals for a                                                      | e e construir de la construir d |                                        |                                                                                       |

| timer_signals 🛹                                  |                   |                                                                | 8:6                                                              | Src_sel              | rw           | ro                    | 0       | given timer. If no source width is defined, then the<br>timer will count the clock edges depending upon the | bits 🗢 name<br>31:0 F1                                                                                          |                                        | ult  description  Defines the prescaling values                                       |

| Properties                                       |                   |                                                                |                                                                  |                      |              |                       |         | prescaling value.                                                                                           | 51:0 F1                                                                                                         | rw ro 0                                | Defines the prescaling values                                                         |

| Description                                      |                   |                                                                |                                                                  |                      |              |                       |         |                                                                                                             |                                                                                                                 |                                        |                                                                                       |

| name 🗘 po                                        | rt type           | description                                                    | 1                                                                |                      |              |                       |         |                                                                                                             |                                                                                                                 | counter                                | address<br>default                                                                    |

| status_reset[1:0] inp                            | put               |                                                                | 1                                                                |                      | period       |                       |         | address<br>default                                                                                          |                                                                                                                 |                                        | default                                                                               |

| result_reset[1:0] inp                            | out               |                                                                | count=2                                                          | 2:                   |              |                       |         |                                                                                                             | rtl.reg_enb=false;count=2;                                                                                      |                                        |                                                                                       |

| counter_reset[1:0] inp                           | out               |                                                                | Descrip                                                          | otion                |              |                       |         |                                                                                                             |                                                                                                                 |                                        |                                                                                       |

| counter_start[1:0] inp                           | put               |                                                                | bits 🖨                                                           | name                 | <b>♦</b> s/w | <b>♦</b> h/w <b>♦</b> | default | ♦ description                                                                                               | bits 🗢 name                                                                                                     |                                        |                                                                                       |

|                                                  |                   |                                                                | 31:0     F1     rw     ro     0     Provides the threshold value |                      |              |                       |         |                                                                                                             | 31:0 F1                                                                                                         | rw ro 0                                | {counter=incr;resetsignal=counter_reset%d:0:sync:hig<br>h.counter_start:1:sync:high;} |

| status                                           |                   | addressdefault                                                 | ]                                                                |                      |              |                       |         |                                                                                                             | · · · ·                                                                                                         |                                        |                                                                                       |

| rtl.reg enb=false;resetsignal=status reset%d:0:: | sync:low:count=2: |                                                                |                                                                  |                      | enable       |                       |         | address<br>default                                                                                          |                                                                                                                 |                                        |                                                                                       |

|                                                  | ,,                |                                                                | rtl.reg                                                          | g_enb-false;count-2; |              |                       |         | uciaut                                                                                                      |                                                                                                                 |                                        |                                                                                       |

| bits 🕈 name 🗘                                    | s/w ♥ h/w ♥ defau | ilt  description                                               | 1                                                                |                      |              |                       |         |                                                                                                             |                                                                                                                 |                                        |                                                                                       |

|                                                  | r/w1c wo 0        | Interrupt status for overflow{intr.status=overflow;}           | bits 🗧                                                           | name                 | <b>♦</b> s/w | \$ h/w \$             | default | ♦ description                                                                                               |                                                                                                                 |                                        |                                                                                       |

| 1 run_intr                                       | r/w1c wo 0        | Interrupt status for running<br>mode{intr.status=running;}     | 0                                                                | Over_intr_en         | rw           |                       | 0       | Interrupt enable for overflow {intr.enable=overflow;}<br>Interrupt enable for running                       |                                                                                                                 |                                        |                                                                                       |

|                                                  |                   | Interrupt status for periodic                                  | 1                                                                | Run_intr_en          | rw           | na                    | 0       | mode {intr.enable=running;}                                                                                 |                                                                                                                 |                                        |                                                                                       |

| 2 period_intr                                    | r/w1c wo 0        | mode {intr.status=periodic;}                                   | 2                                                                | Period_intr_en       | rw           | na                    | 0       | Interrupt enable for periodic<br>mode {intr.enable=periodic;}                                               |                                                                                                                 |                                        |                                                                                       |

| 3 cfg_ch                                         | r/w1c wo 0        | Interrupt status for configuration<br>change{intr.status=cfg;} | 3                                                                | cfg                  | rw           | na                    | 0       | Interrupt enable for configuration<br>change{intr.enable=cfg;}                                              |                                                                                                                 |                                        |                                                                                       |

|                                                  |                   |                                                                |                                                                  |                      |              |                       |         |                                                                                                             |                                                                                                                 |                                        |                                                                                       |

|                                                  |                   |                                                                |                                                                  |                      | ×            |                       |         |                                                                                                             | 1                                                                                                               |                                        |                                                                                       |

|                                                  |                   |                                                                |                                                                  |                      |              |                       |         |                                                                                                             |                                                                                                                 |                                        | 2023                                                                                  |

DESIGN AND VERI

UNITED STAT

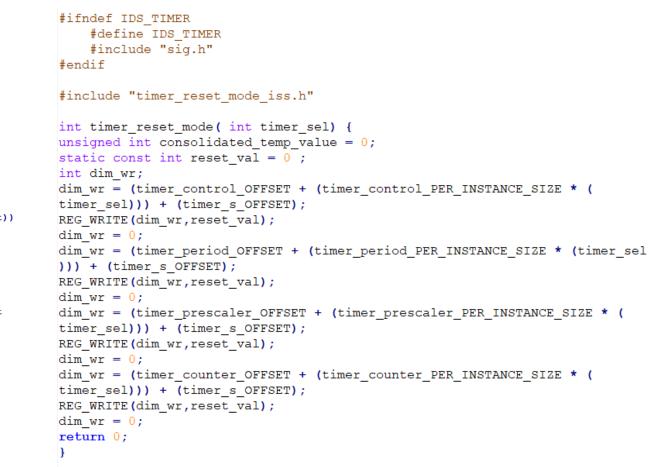

#### Auto Generating Standard IPs - Cont'd

#### Generated sample code

module timer\_top #(

```

parameter bus width = 32,

parameter addr width = 6,

parameter timer offset = 'h0,

parameter timer count = 2

)

(

input clk,

input reset,

input [7:0]src,

output [timer count-1:0]irg tmr,

);

reg [timer count-1:0] cfg f;

wire [timer count-1:0] irq wire;

timer ids #(.bus width(bus width),.addr width(addr width),.block offset(timer offset))

regmap(

.status reset (control en r),

.result reset (control en r)

);

generate

genvar tmr cnt;

for(tmr cnt =0; tmr cnt < timer count; tmr cnt = tmr cnt + 1) begin : timer cnt

timer core #(.bus width(bus width),.addr width(addr width)) core(

.clk(clk),

.src(src),

.reset(reset),

.timer enb(control en r[tmr cnt]),

. . .

.pre_clk(clk_en[tmr_cnt])

);

assign irq_tmr[tmr_cnt] = irq_wire[tmr_cnt];

end

```

#### endgenerate

endmodule

C sequence

# What's Complete-IP ?

□ Generating the RTL for the register IP/specification for the addressable registers

Once a register specification is captured and its RTL generated -

- A synthesizable application logic layer is required to interact with the addressable registers

- The intended functionality and configuring of the RTL registers in done using this user logic

The pushbutton Complete-IP helps in capturing this design functionality (User Application Logic) by using simple templates, which will help in the overall "completeness" of an IP

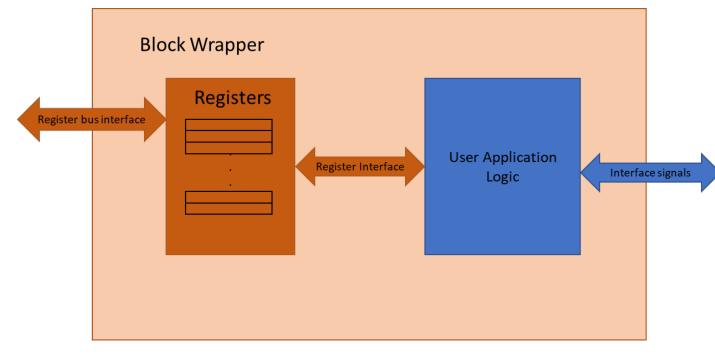

### **Complete-IP Overview Diagram**

•The orange box depicts the addressable registers for the IP

•The blue box depicts the user application logic which the user creates manually. The aim is to automate this application logic creation with the help of predefined templates

## User Application Logic Constructs

Over the year on looking at different sort of register IP and its user hardware logic, it can be said that the user logic mainly constitutes of the following constructs -

- State machines

- DQ tables

- Assign statements

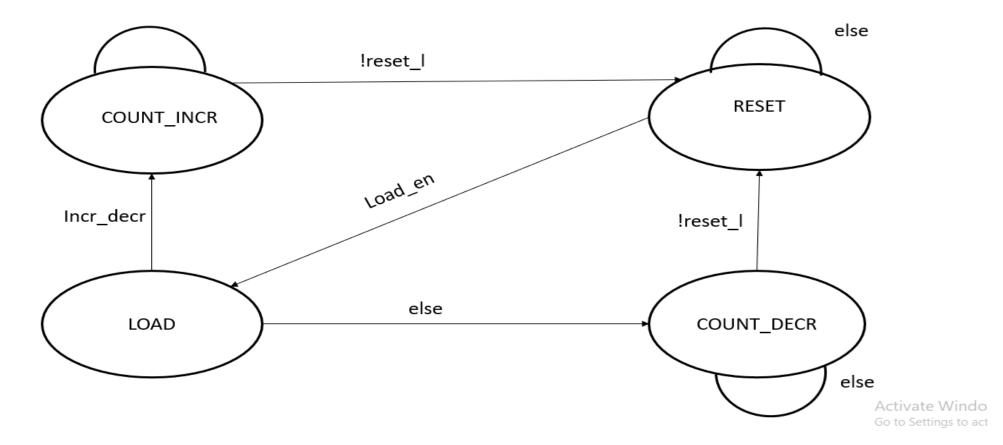

# State Machine Design Template

- A construct which makes transitions through a series of states based on external inputs and the current state of the machine

- Used for designing more complex hardware

- The hardware functionality can be broken down into a collection of states which determines when the system transitions from one state to another

- Uses can capture these states and align then on different external inputs the next state as described. Also, outputs at different states can be specified.

- User can also capture the state transitions from the current state to the next state and all the outputs associated with it

### Sample State Machine Design

A sample template for capturing FSM

## DQ Table Design Template

- A flip-flop is the basic storage element in a sequential logic, which is a fundamental building block of any electronic system

- Thus it becomes more important to give designers some way to make flops to capture sequential logic

- A template (DQ Table) can be used for the above purpose, where the user can specify the outputs in one column and specify the assignments on the other column

#### DQ Table Design Template Cont.

| DQ Name           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| description       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Q name            | D Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \$ |

| counter_reg[15:0] | <pre>if (!reset_l){     counter_reg = 0     } else{     if (load_en){         counter_reg = block1.load.load     } else if (incr_decr){         if((incr_decr_sat_val -counter_reg) &lt;= incr_decr_val){         counter_reg = incr_decr_sat_val         } else {         counter_reg = counter_reg + incr_decr_val         }     } else{         if((counter_reg -incr_decr_sat_val) &lt;= incr_decr_val){         counter_reg = incr_decr_sat_val     }     } else {         counter_reg = incr_decr_sat_val     }     } }</pre> |    |

#### Assign Table Template

- For designing circuits often dataflow modelling is used. Dataflow modelling describes the flow of data from input to output in hardware.

- The continuous assignment statement is the main construct of dataflow modelling and can be used to drive(assign) values.

- The introduction of the assign table as below can be used to capture dataflow modelling.

| assign Name             |                                                                   |

|-------------------------|-------------------------------------------------------------------|

| description             |                                                                   |

| assign 🗢                | value                                                             |

| block1.status.overflow  | ((counter_reg >= incr_decr_sat_val) && incr_decr) ? 1'b1 : 1'b0;  |

| block1.status.underflow | ((counter_reg <= incr_decr_sat_val) && !incr_decr) ? 1'b1 : 1'b0; |

Activate Windows

24

An assign table template

#### Non Addressable Registers Template

- Creation of application logic requires registers to store certain results, etc. A table can be incorporated which captures the register names and the width of the register.

- For making the non addressable registers as output, then a register can be specified in the table below with direction as out.

| register Name     |   |         |   |

|-------------------|---|---------|---|

| description       |   |         |   |

| register name     | ¢ | default | ¢ |

| counter_reg[15:0] |   | 0x0     |   |

A sample template to add non-addressable registers

# Generated User RTL

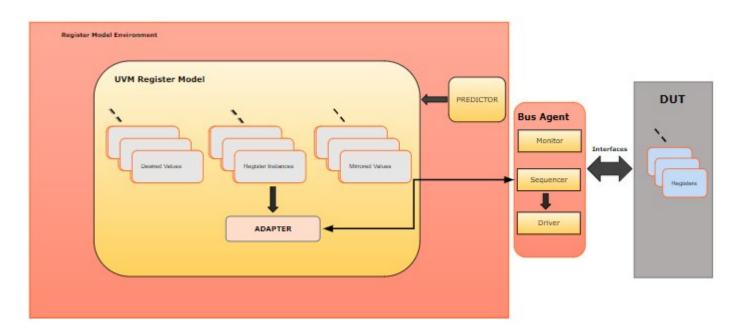

- By using the mentioned templates, the user can generate the RTL as well as the UVM prediction model for their user logic interaction with the RTL of the addressable registers

- And along with it, the UVM prediction model will be hooked in the environment automatically for the same

```

// FSM1: Registered outputs, sequential always block

always @ (posedge clk) begin

case (FSM1 next state)

RESET: begin

counter req <= 0;

end

LOAD: begin

counter reg <= load load q;</pre>

end

COUNT INCR: begin

if((incr decr sat val - counter reg) <= incr decr val)</pre>

begin

counter reg <= incr decr sat val;

end

else

begin

counter reg <= counter reg + incr decr val;</pre>

end

end

COUNT DECR: begin

if((counter reg - incr decr sat val) <= incr decr val)</pre>

begin

counter reg <= incr decr sat val;

end

else

begin

counter req <= counter req - incr decr val;

end

end

endcase

```

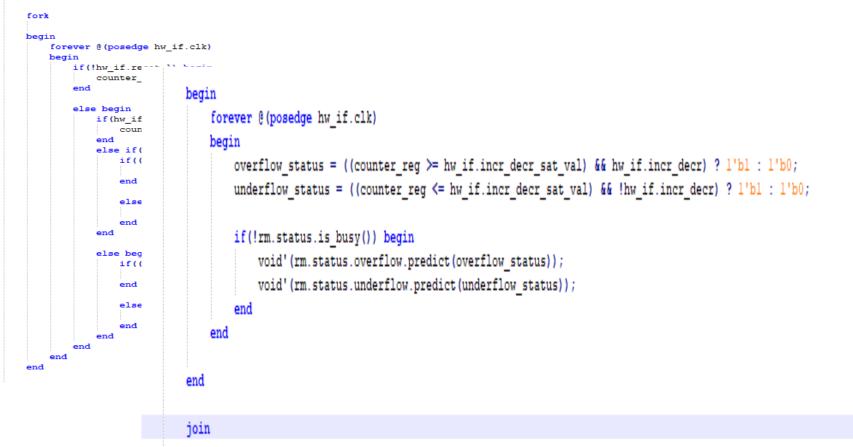

## Generated UVM Prediction Model

- The signal which corresponds to the non addressable registers can be monitored and can be compared with the UVM model, if the mismatch occurs then the model will give generate errors

- Call the predict method in UVM when there are assignments back to the IDS

CSR registers (IDS CSR updated through applogic)

ESIGN AND VERIFICATION DESIGN AND VERIFICATION SYSTEMS INITIATIVE UNITED STATES

### **Generated UVM Prediction Model Example**

task update();

## **Auto-Generated Tests**

General algoritm for test generation

- 1. Create a list of all outputs from the app logic app\_logic\_out\_list

- 2. Create a list of all inputs to IDS generated register logic. Mark all the nets that are pairs (enable and input).

- 3. For each item in the above two lists, create a LOGIC CONE that drives the net

- a. The graph will have nodes and arrows going in (inputs) and coming out (outputs) of the node

- b. The node will be either combinational or sequential

- c. Combinational will simply have a combinational function based on the inputs

- d. Sequential will have a clock, reset and some properties that affect the clock

- 4. For each item, traverse the graph and find how to make the net transition to 1 and 0

- 5. There will be several solutions; store them in appropriate data structure

#### Auto-Generated Tests - Cont'd

rand int RV\_16\_0 ;

rand int RV\_4\_1 ;

constraint RV\_16\_0\_constraint

RV\_16\_0 <= RV\_4\_1;</pre>

constraint RV\_4\_1\_constraint

RV\_4\_1 >= RV\_16\_0;

#### task body;

```

if(!uvm_config_db #(virtual blockl_hw_if)::get(null,"*","blockl_hif",blockl_hwif)) begin

`uvm_fatal("**CUSTOM_SEQ**", "cannot get blockl_hwif from config_db")

```

#### end

if(!\$cast(rm, model)) begin

```

`uvm_error("RegModel : blockl_block","cannot cast an object of type uvm_reg_sequence to rm");

end

```

#### if (rm == null) begin

```

`uvm_error("block1_block", "No register model specified to run sequence on, you should specify regmodel by using property 'uvm.regmodel' in the sequence") return;

```

#### end

#1000; blockl\_if.load\_en = 'h0;

blockl\_if.incr\_decr = 'hl;

void'(this.randomize());

blockl\_if.incr\_decr\_val = RV\_4\_1;

```

blockl_if.incr_decr_sat_val = RV_16_0;

```

```

while (!blockl_hwif.status_overflow_r)

begin

```

**#**1000;

end

Activate Windows Go to Settings to activate Wind

#### Auto-Generated Tests - Cont'd

```

function new(string name = "uvm_seq_1_seq") ;

super.new(name);

```

endfunction

task body;

```

if(!uvm_config_db #(virtual block1_hw_if)::get(null,"*","block1_hif",block1_hwif)) begin

`uvm_fatal("**CUSTOM_SEQ**", "cannot get block1_hwif from config_db")

```

end

```

if(!$cast(rm, model)) begin

```

```

`uvm_error("RegModel : block1_block","cannot cast an object of type uvm_reg_sequence to rm");

end

```

```

if (rm == null) begin

```

`uvm\_error("block1\_block", "No register model specified to run sequence on, you should specify regmodel by using property 'uvm.regmodel' in the sequence")

#### return;

end

#### **#**1000;

```

block1_hwif.valid = 'h1;

```

block1 hwif.ff1 = 'h0;

```

while (!block1_hwif.reg1_f1_r)

begin

```

```

#1000;

end

```

Activate Windows Go to Settings to activate Windows.

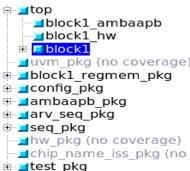

### Coverage Report

• We can get code coverage of the design that is created to check whether all lines of code have been covered or not

#### 🗄 😹 🕼

#### Testplan <mark>Design</mark> DesUni

**Coverage Summary By Instance:**

| Scope 🖣 | TOTAL 🚽 | Statement | Branch ୶ | FEC Expression < | Toggle |

|---------|---------|-----------|----------|------------------|--------|

| TOTAL   | 80.70   | 93.93     | 92.59    | 60.86            | 75.41  |

| block1  | 83.97   | 91.30     | 90.47    | 80.00            | 74.11  |

| apb     | 85.10   | 100.00    | 100.00   | 46.15            | 94.28  |

#### Local Instance Coverage Details:

| Total Covera              | age: |      |          |          | 74.86%     | 83.97%     | Te       |

|---------------------------|------|------|----------|----------|------------|------------|----------|

| Coverage<br>Type ∢        | Bins | Hits | Misses 🛛 | Weight ୶ | %<br>Hit ∢ | Coverage 🛛 |          |

| Statements                | 23   | 21   | 2        | 1        | 91.30%     | 91.30%     | St       |

| <b>Branches</b>           | 21   | 19   | 2        | 1        | 90.47%     | 90.47%     | B        |

| <u>FEC</u><br>Expressions | 10   | 8    | 2        | 1        | 80.00%     | 80.00%     | FI<br>E: |

| <u>Toggles</u>            | 1020 | 756  | 264      | 1        | 74.11%     | 74.11%     | Т        |

#### **Recursive Hierarchical Coverage Details:**

| Total Covera       | ige: |      |         |          | 76.04%     | 80.7  |

|--------------------|------|------|---------|----------|------------|-------|

| Coverage<br>Type ∢ | Bins | Hits | Misses  | Weight ୶ | %<br>Hit ∢ | Cover |

| Statements         | 33   | 31   | 2       | 1        | 93.93%     | 93.9  |

| Branches           | 27   | 25   | 2       | 1        | 92.59%     | 92.5  |

| FEC<br>Expressions | 23   | 14   | 9       | 1        | 60.86%     | 60.8  |

| Toggles            | 1090 | 822  | 268     | 1        | 75.41%     | 75.4  |

|                    |      |      | Activat | Mindow   | -          |       |

### Benefits

- Fully configurable and customizable IPs/addressable registers that can be generated for varied set of needs

- All the generated files are available as plain text for easy debugging and use by downstream tools

- Generation of the synthesizable RTL for both the user logic and the addressable register logic

- The complete IP / entire design can further be extended for the verification of the design.

- Supports specification of finite state machines (FSMs), data paths, signals, and other parts of custom IP blocks in your application logic

- For both standard and customer blocks, IDS-IPGen generates RTL models, UVM verification models, and on the fly AI based tests that provide high functional and code coverage right out-of-the-box.

# Conclusion

- Reduction in time and cost of development

- Focus more on creating the algorithm for your design, and let the tool handle and ensure the correctness

- Complexity can be handled by using abstraction

- One of the forms of abstraction is reuse

- Reuse is possible if the IPs are customizable and configurable

- Create the complete IP and validate the synthesizable design through auto-generated tests with optimum code coverage

#### Questions