## Improving Debug Productivity using latest AI & ML Techniques

#### Amod Khandekar Sr Principal Customer Engagement Engineer Cadence

Amod has been working with Cadence for past 20 years. He has worked as Pre Sales and Customer Support Engineer supporting all the verification related tools. Currently he is part of Product Engineering team with Focus on Verisium Apps.

SYSTEMS INITIATIVE

Sundararajan Ananthakrishnan Application Engineer Architect Cadence

Sundar has been at Cadence for 13 years, with an overall Experience of 23+ years in the field of SoC & IP Verification. Sundar leads the Cadence AVS field team for India region and drives the Advanced ML/AI and Verification Solutions in the region.

#### Amit Verma Software Engineering Director Cadence

Amit has been at Cadence for 18 years, and until 2021 he was managing multiple coverage related Formal apps for Cadence's Formal product, IEV earlier and currently Jasper. For 2 years he has been managing innovative software developments for Verisium buglocalization apps.

He is passionate about exploring how the ML/AI and Verification technologies can be used together to accelerate the design verification.

# Improving Debug Productivity using latest AI & ML Techniques

Amod Khandekar, Amit Verma, Sundararajan A Cadence Design Systems

> Narasimha Rao Chinni Samsung

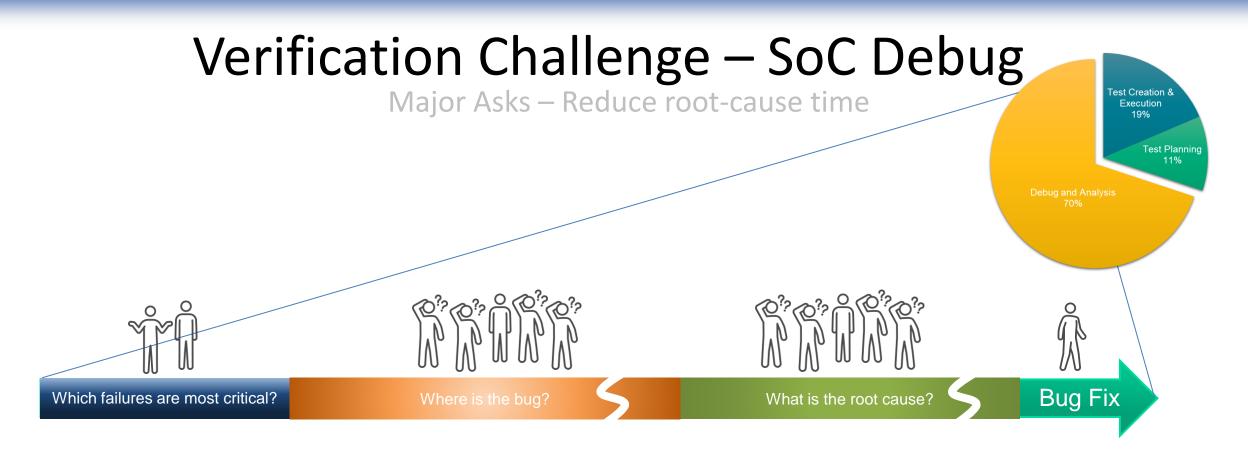

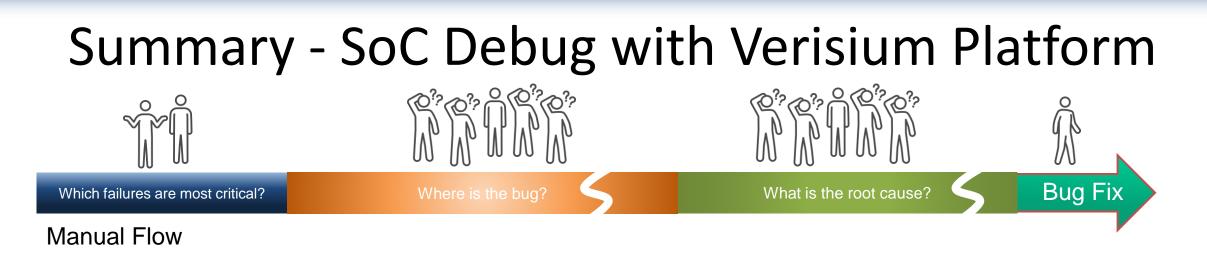

- SoCs integrate hundreds of IP

- Each of the IP is constantly changing, evolving, improving

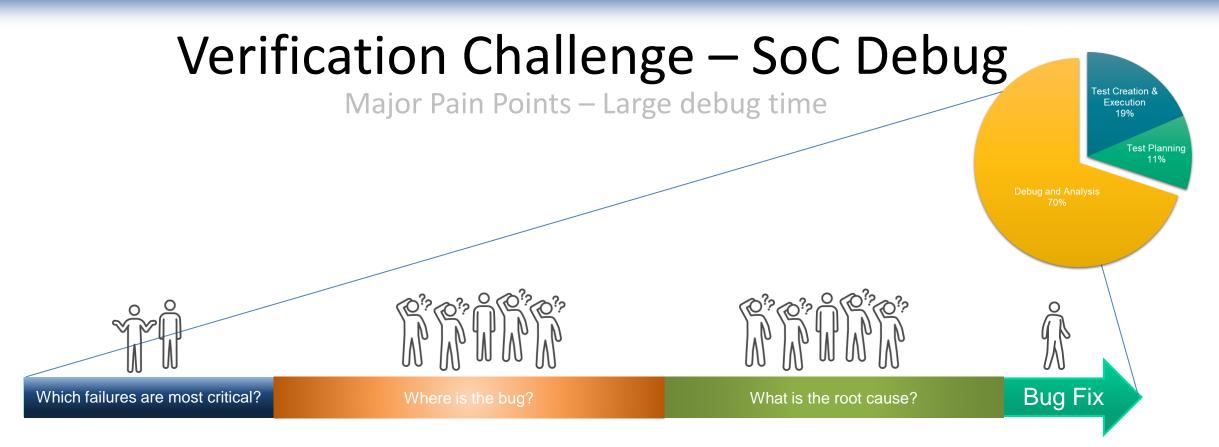

- Week to week, SoC-level testing results in several test failures

- 2 major pain points

- Determining the root cause (source code) of the failure takes significant time/resources

- Determining the **test** to reproduce the failure in shortest time takes significant time/resources

- Provide the Semantic behavior changes (Structural) for quick analysis for design changes

- Provide the Functional behavior changes for accurate analysis for design changes

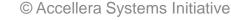

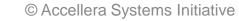

- Provide the failure causing repository version from large chain of versions for filtered analysis of failure

- Provide the shortest failing test per failure for reproducing faster a failure

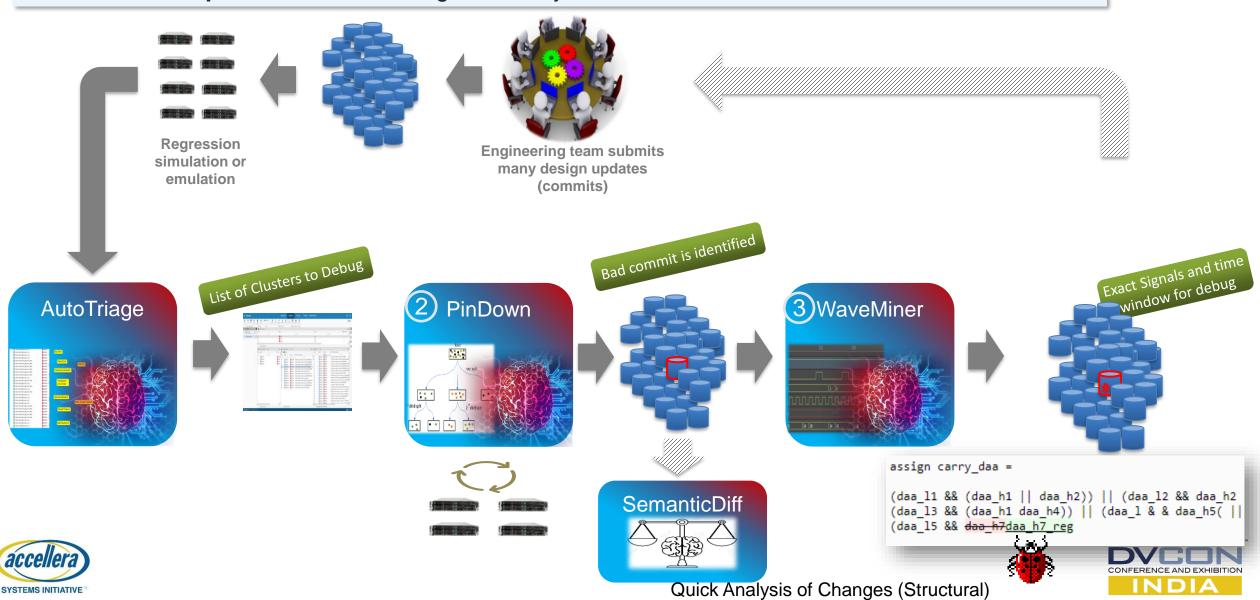

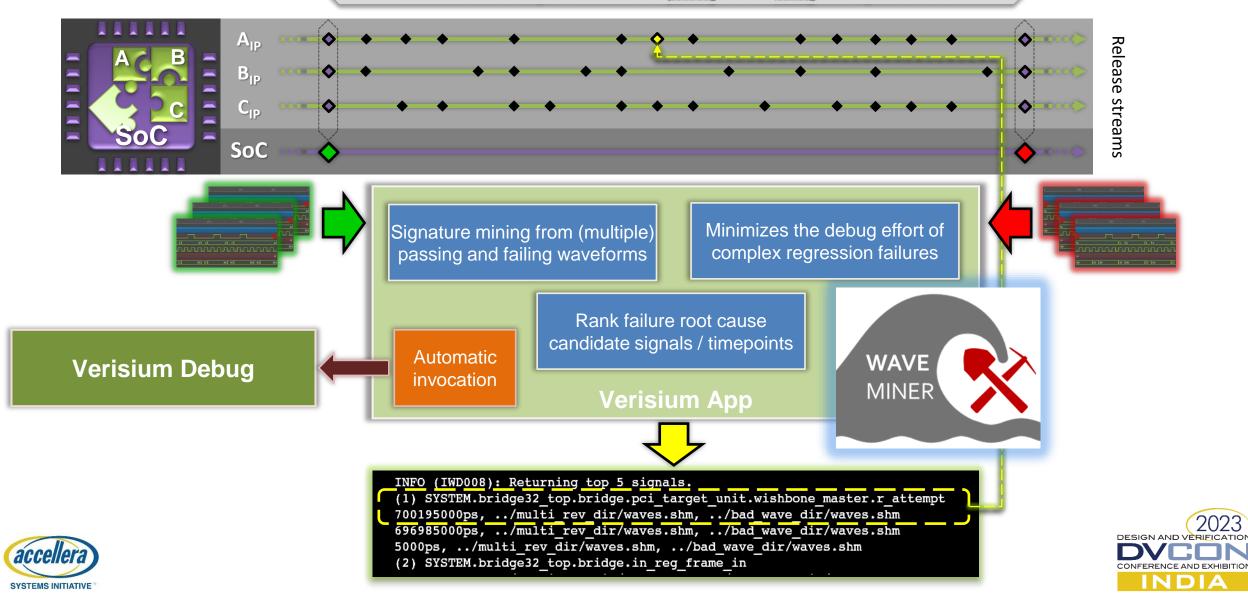

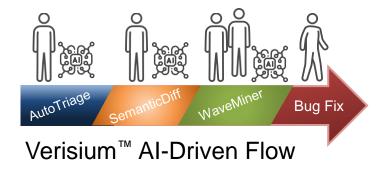

#### **Automatic Bug Localization Solution & Apps**

Given two design versions and regression failure, predict/locate with high accuracy the root-cause at source code

## Verisium AutoTriage

#### Vanilla Failure Triage Flow

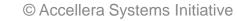

### AutoTriage – Automated ML Bucketing of Regression Failures

- Solution

- Automate the failure analysis/classification using Supervised Learning ML

- Initial results show success rate of ~95% prediction

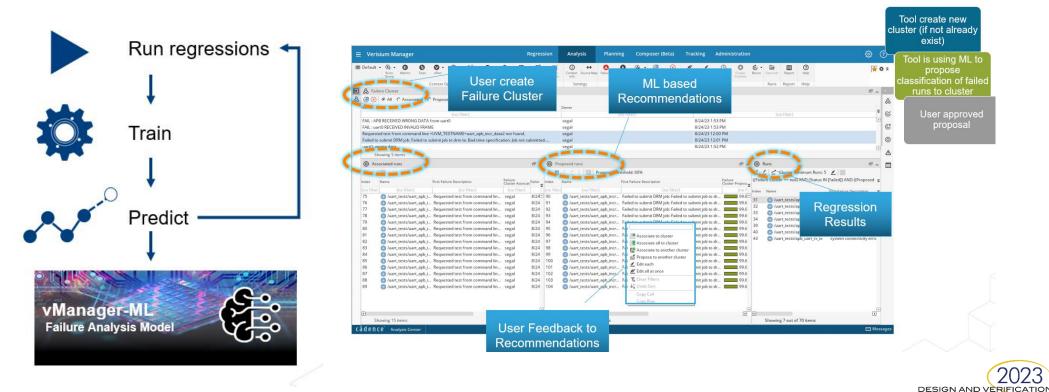

## Configuring Verisium Manager for AutoTriage

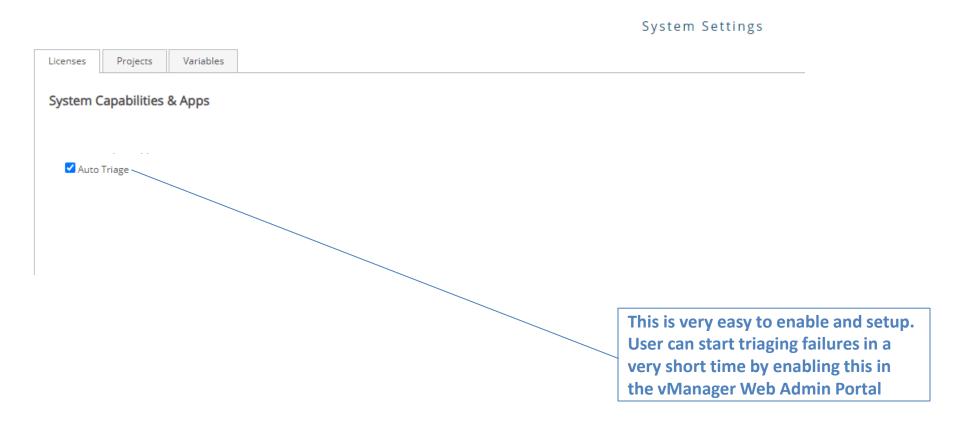

## Run Attributes used in learning

- By default, only the Run name and first failure description are used in the ML learning process however if other attributes are useful, they should be added **before** the learning process begins

- Changing the attributes will <u>reset the learning</u>, however after reset if the previous data (failed run to cluster association) exist the tool learning curve is very fast

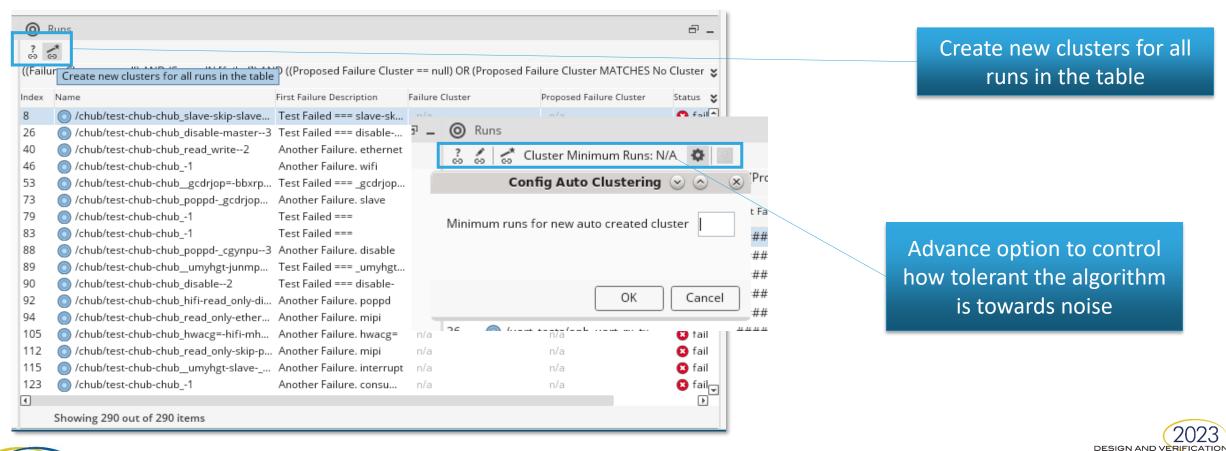

# Enhancements to Create New Clusters Unsupervised ML

Unrecognized pattern (Unsupervised ML)

> ML create new clusters, and proposed failed runs to the new Cluster (trigger by user)

New Button added to Failure Cluster Analysis Context to create Automatic Clusters

## Enhancements to Control Automatically Proposed Existing Clusters, Supervised ML

& Failure Cluster 🕏 🛃 🔙 🥵 🖉 🥢 😣 🥜 🕟 💽 🕞 🌍 🔈 Proposal threshold: 50 0 Proposed runs 6 22 2 2 X Proposal Threshold: 50 Failure First Failure Description Cluster Proposal Assurance vM ######## FAIL : uart0 RECEIVED WRONG DATA 90.26% ####### FAIL : uart0 RECEIVED WRONG DATA 90.26% νN ####### FAIL : APB RECEIVED WRONG DATA 'h4c from uart0 99.57% νN 99.57% ####### FAIL : APB RECEIVED WRONG DATA 'h86 from uart0 vN ####### FAIL : APB RECEIVED WRONG DATA 'h12 from uart0 99.58% νN ####### FAIL : APB RECEIVED WRONG DATA 'hc2 from uart0 νN 99.57% ####### FAIL : APB RECEIVED WRONG DATA 'hb7 from uart0 99.57% νN ####### FAIL : APB RECEIVED WRONG DATA 'h3c from uart0 99.57% νN ####### FAIL : APB RECEIVED WRONG DATA 'h13 from uart0 99.57% v٨ ####### FAIL : APB RECEIVED WRONG DATA 'h7b from uart0 99.57% νN ####### FAIL : APB RECEIVED WRONG DATA 'h93 from uart0 99.57% νN ####### FAIL : APB RECEIVED WRONG DATA 'hfb from uart0 99.57% νN ####### FAIL : uart0 RECEIVED WRONG DATA 90.26% ####### FAIL : APB RECEIVED WRONG DATA 'h99 from uart0 99.57% vN ####### FAIL : APB RECEIVED WRONG DATA 'hcc from uart0 99.57% νN ####### FAIL : APB RECEIVED WRONG DATA 'h2e from uart0 99.57% ####### FAIL : APB RECEIVED WRONG DATA 'h84 from uart0 99.57%

accellera

SYSTEMS INITIATIVE

The threshold can be configured in the admin page

The configurable threshold for proposals

New attribute show the percentage of the assurance level we have for the cluster proposal

Recognized pattern

(Supervised ML)

ML proposed failed runs to existing Clusters (automatically)

### VERISIUM AUTOTRIAGE DEMO

| Launch Impo    | rt Collect Refresh Scripts | Export Export Stop Au<br>Merge | to. Suspend Resume | Set as Delete Rel | locate Open dir Sessi | ion Recalc UDA Chart | Eq. C +                   | Recover     Metrics     Tests | 💟 - 🙆 - 🜔 - (<br>vPlan Failures Runs Fo |                  | ()<br>Help         | 🚖 🕸 🌣        |

|----------------|----------------------------|--------------------------------|--------------------|-------------------|-----------------------|----------------------|---------------------------|-------------------------------|-----------------------------------------|------------------|--------------------|--------------|

|                | Il Operations Scripts      |                                |                    | Sessi             |                       | 0                    | Selected Pallures Session | Session                       | Analyze                                 | Report           |                    |              |

| Flow Sessions  |                            |                                |                    |                   |                       |                      |                           |                               |                                         |                  |                    | 8 <b>-</b> 1 |

| on Status      | Name                       |                                | Total Runs         | #Pa               | issed                 | #Failed              | #Running                  | #Waiting                      | #Other                                  | Start Time       | ▼ <sub>Owner</sub> | * 모          |

| (no filter)    |                            | (no filter)                    |                    | filter)           | (no filter)           | (no filter)          | (no filter)               | (no filter)                   | (no filter)                             | (no filter)      | (no filte          | er)          |

| pleted         | auto_triage_1              | *                              | 94                 | 30                |                       | 64                   | 0                         | 0                             | 0                                       | 10/13/22 6:40 PM | amodk              | - E          |

|                |                            |                                |                    |                   |                       |                      |                           |                               |                                         |                  |                    |              |

|                |                            |                                |                    |                   |                       |                      |                           |                               |                                         |                  |                    |              |

| Showing 1 item |                            |                                |                    |                   |                       |                      |                           |                               |                                         |                  |                    |              |

CONFERENCE AND EXHIBITION

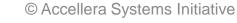

## Verisium SemanticDiff

# SemanticDiff – Meaningful Diff Analysis

- An advanced AI Driven RTL design comparison tool

- Handles both DUT and TB

- Compares two snapshot versions of the same RTL design

- Determines the meaningful semantic differences between them

- Generates diff metrics for the analysis

- CSV and summary log, useful for postprocessing

- Module and design-hierarchy metrics

- Analysis completes very fast

- in 30% of the time it takes to compile + elaborate entire design

## SemanticDiff – Meaningful Diff Analysis

### Launching SemanticDiff

verisium -semanticdiff

-xmlibdirpath\_golden <path of reference snapshot>

-xmlibdirpath\_new <path of the new snapshot>

<other user configurable options>

### Verisium SemanticDiff Results

| semantic_diff version: 23.05-a071-a007               |

|------------------------------------------------------|

| Module analyzed: 682 diff found in : 24              |

| Interface analyzed: 185 diff found in : 6            |

| LibItem analyzed: 132 diff found in : 0              |

| Program analyzed: 0 diff found in : 0                |

| Global analyzed: 0 diff found in : 0                 |

| Primitive analyzed: 0 diff found in : 0              |

| Class analyzed: 7177 diff found in : 38              |

| Entity excluded because of protected in Golden: 3827 |

| Entity excluded because of protected in New: 3827    |

| Return status 0                                      |

|                                                      |

The summary log shows how many entities we analyzed and where we found semantic differences

> The detailed csv report gives individual statistics about each file where semantic differences were found

> > DESIGN AND VERIFICA

| Entity Typ | Entity Name | Entity golden File/Line                           | Entity new File/Line                              | Mode     | Modified | Added lin | Deleted I | Total lines | Diff count | Total cour | Rank |

|------------|-------------|---------------------------------------------------|---------------------------------------------------|----------|----------|-----------|-----------|-------------|------------|------------|------|

| Class      | class1      | /user/project/dv/verif/tb/class1.sv(23)           | /user/project/dv/verif/tb/class1.sv(23)           | Modified | 253      | 641       | 645       | 2452        | 303461     | 539651     | 1    |

| Class      | class2      | /user/project/dv/verif/tb/class2.sv(18)           | /user/project/dv/verif/tb/class2.sv(18)           | Modified | 0        | 256       | 257       | 584         | 61414      | 72210      | 2    |

| Module     | module1     | /user/project/dv/rtl/core_registers/module1.v(18) | /user/project/dv/rtl/core_registers/module1.v(18) | Modified | 208      | 432       | 16        | 182002      | 4001       | 488749     | 3    |

| Class      | class3      | /user/project/dv/verif/config/class3.sv(48)       | /user/project/dv/verif/config/class3.sv(48)       | Modified | 2        | 2781      | 4287      | 8286        | 25412      | 291789     | 4    |

| Class      | class4      | /user/project/dv/verif/common/class4.sv(67)       | /user/project/dv/verif/common/class4.sv(67)       | Modified | 9        | 758       | 775       | 6393        | 25097      | 60230      | 5    |

| Class      | class5      | /user/project/dv/verif/random/class5.sv(27)       | /user/project/dv/verif/random/class5.sv(27)       | Modified | 3        | 238       | 246       | 4189        | 24500      | 34570      | 6    |

| Module     | module2     | /user/project/dv/rtl/phy/module2.v(19)            | /user/project/dv/rtl/phy/module2.v(19)            | Modified | 10       | 6         | 45        | 37850       | 1057       | 186019     | 7    |

| Interface  | interface1  | /user/project/dv/verif/sve/interface1.sv(132)     | /user/project/dv/verif/sve/interface1.sv(132)     | Modified | 0        | 0         | 1         | 16585       | 11         | 90446      | 8    |

| Module     | module3     | /user/project/dv/rtl/core/module3.v(8)            | /user/project/dv/rtl/core/module3.v(8)            | Modified | 1        | 0         | 0         | 20836       | 6          | 80227      | 10   |

|            |             |                                                   |                                                   |          |          |           |           |             |            |            |      |

|            |             |                                                   |                                                   |          |          |           |           |             |            |            |      |

|            |             |                                                   |                                                   |          |          |           |           |             |            |            |      |

## Verisium SemanticDiff Performance

| DESIGN   | Compile + Elaboration Time(sec) | SemanticDiff Analysis Time(sec) |

|----------|---------------------------------|---------------------------------|

| Design 1 | 921                             | 220                             |

| Design 2 | 2596                            | 716                             |

| Design 3 | 8558                            | 2901                            |

| Design 4 | 14480                           | 3120                            |

- The numbers here represent SemanticDiff Analysis on the entire snapshot

- Semantic ff completes in 20-30% of compile+elab time.

- $\circ~$  User has flexibility to run SemanticDiff on portion of the snapshot for faster turnaround time

### VERISIUM SEMANTICDIFF DEMO

I

[amodk@nofccl103 SIM]\$ ./RUN\_SD

## Verisium PinDown

### **Running PinDown**

verisium -pindown -config <path to pindown\_config file > --session\_name <session to run PinDown analysis> --vmanager server <server on which PinDown should run analysis>

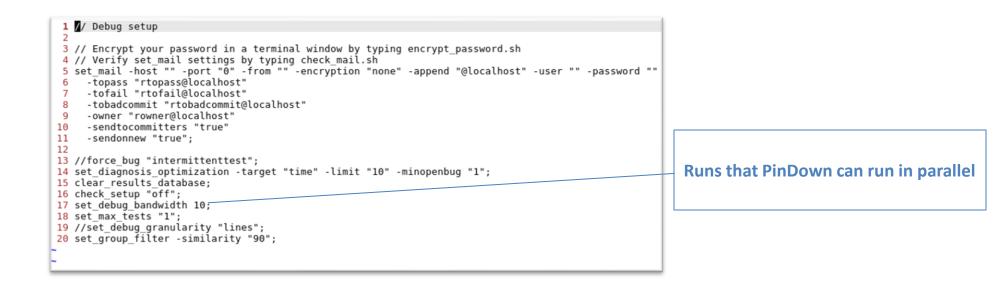

- Config file configures the PinDown Debug Analysis

- Defines debug options for PinDown

- Provides version control information

- Defines how long should PinDown Debug run

### **Revision Control and Debug Options**

1 // Encrypt your password in a terminal window by typing encrypt\_password.s

2 set\_repository -option "GIT=\$GIT\_INSTALL";

3 set\_repository -type "git" -location "\$PINDOWN\_STARTDIR/git\_repo/selected\_demo.git" -username "daniel" -password "ENC:92jSGCHnt80vSzAaHrwxtw" -checkoutarea "apb\_uart"; 4 set\_earliest\_revision -days "To be set at launch"; // don't change this line. PinDown needs it. Instead modify settings in pindown\_config

32

Revision Control information that PinDown uses for debug.

### PinDown Bug Report in Demo

pindown.log:

| Open workdir/latest_debug/pindownlogs/text/pi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Debug result accepted:<br>Bug ID: C1<br>Run ID: 1067                                                   |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| runnerpostsess regression: 1 bug (committed by daniel) - Full Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                        |                                  | Debug Status: pilot_validated_bug                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| PinDown has debugged the following in <i>runnerpostsess</i> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                        |                                  | Committer: daniel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Bug No C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| <pre>PinDown made the failing test pass again by only removing the bad commit. The<br/>Test: apb_to_uart_1stopbit_seed_1539187831<br/>• id = 1067<br/>Build: uart_tests</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s was done locally, nothing was committed.                                                             |                                  | Generating waveminer results for bug: C1 (new bug)<br>waveminer results for bug C1 (new bug) are ready under run<br>directory:<br>vmrunner_pindownprerunscript/manual_checkout/apb_uart/apb_<br>uart/my_sessions/uart_ctrl/uvm_regression_25_10_22_14_06_2<br>9/chain_0/uart_tests/run_3/debug<br>Debug is completed.<br>e<br>For the WaveMiner analysis of signals<br>go the folder shown at the end of<br>pindown.log. Here you find 2 important<br>files: waveminer_top_signals and<br>show_waveminer |  |  |  |  |

| Error:<br>first failure description: Assertion wart ctrl top.wart dut.regs.rece                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F                                                                                                      | rror message                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Error at failing revision: first_failure_description: Assertion uart_ctrl_top.uar<br>Validated: true<br>Committer: daniel (why me?)<br>Commit Message:<br>scenario_singlebug.git: 84c80e7cc.2. updated LCR reset value<br>Committed Files (2 files):<br>\$START_PWD/git_repo/scenario_singlebug.git/apb_uart/designs/socv/rtl/rtl_lpw,<br>\$START_PWD/git_repo/scenario_singlebug.git/change [text/plain, text]<br>Changes (shown if small):<br>apb_uart/apb_uart/designs/socv/rtl/rtl_lpw/opencores/uart16550/rtl/uart_regs.v<br>// WRITES AND RESETS //<br>// Line Control Register<br>always @(posedge clk or posedge wb_rst_i)<br>if (wb_rst_i)<br>lcr <= #1 8'b0000001100; // 8n1 setting<br>else<br>if (wb we i && wb addr i==`UART REG LC) | t_dut.regs.receiver.output_counter_t has failed<br>/opencores/uart16550/rtl/uart_regs.v [verilog, hdl] | Commit message<br>for bad commit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| <pre>lcr &lt;= #1 wb_dat_i;<br/>// Interrupt Enable Register or UART_DL2<br/>apb_uart/change: [text/plain, text]</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remember the path to the PinDown logs:<br>workdir/latest_debug/pindownlogs/text                        | 1. ua<br>2. ua                   | weminer_top_signals:       Ranked most         uart_ctrl_top.uart_dut.regs.block_value       problematic signal         uart_ctrl_top.uart_dut.regs.counter_t       problematic signal                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The path is always the same                                                                            |                                  | art_ctrl_top.uart_dut.regs.block_cnt                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Other Failures Linked To The Same Commit:<br>apb_to_uart_1stopbit_seed943840138 on build uart_tests<br>apb_to_uart_1stopbit_seed_406969239 on build uart_tests<br>apb_to_uart_1stopbit_seed_675404693 on build uart_tests<br>apb_to_uart_1stopbit_seed_71424920 on build uart_tests                                                                                                                                                                                                                                                                                                                                                                                                                                                               | All PinDown logs are here<br>It's where you go to see what Pindown did                                 |                                  | w_waveminer:<br>this script to show the wave forms in WaveMiner                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

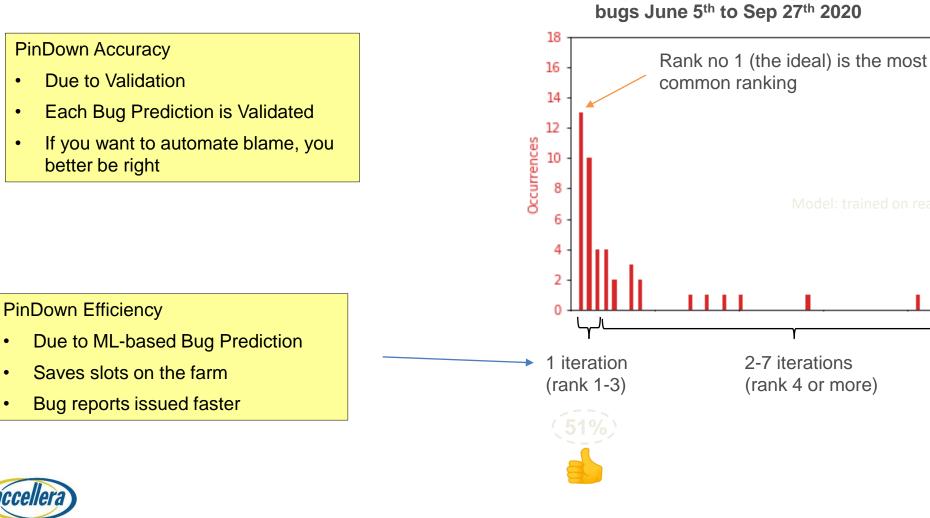

## Customer Use-Case: Bug Report in 1 iteration in 51% of cases

Bug prediction ranking for 53 validated

SYSTEMS INITIATIVE

CONFERENCE AND EXHIBITION

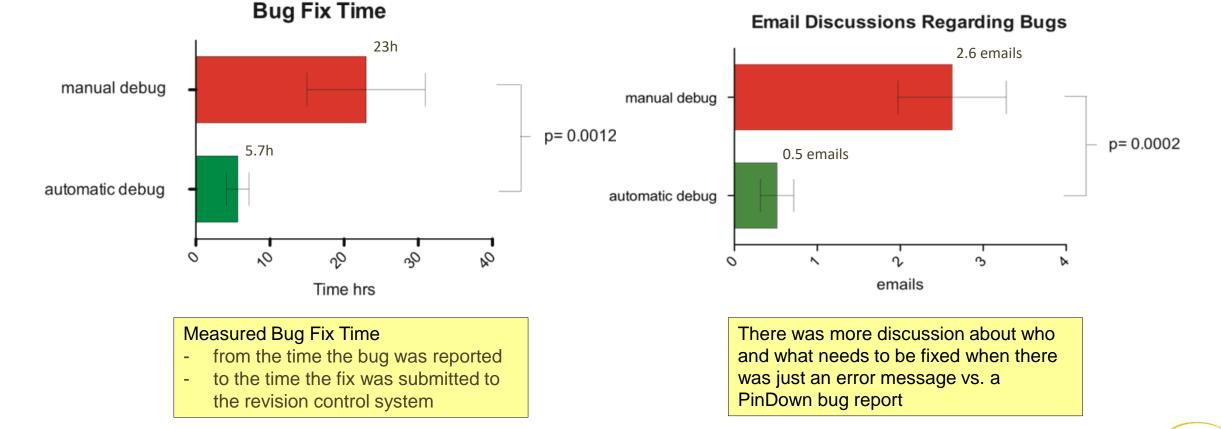

#### Customer Use-Case: Bugs Fixed 4x Faster, 5x Less Discussion

#### **Project Details**

- ASIC IP Project (Microprocessor)

- About 40 people (ASIC designers plus DV engineers)

DESIGN AND VERIFICATION

- Multi-site

- Measured over 3 months

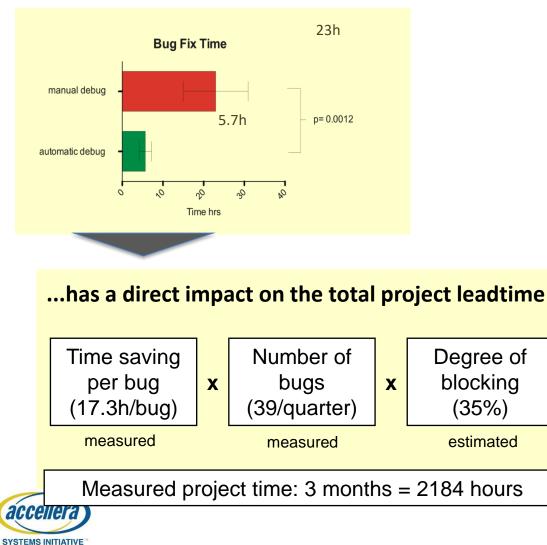

#### **Customer Use-Case: 11% reduced project time**

Time to correct bugs 75% shorter (4x) with PinDown...

#### **Freed up Verification Lead**

- PinDown took over the job of chasing down engineers to fix issues

- Half of the verification lead's time was saved (0.5 engineer years)

#### 11% shorter total project lead time!

- Faster time-to-market

- Major cost savings: 4.4 engineer years (40 engineers in project)

## Verisium PinDown Demo

```

Debugging session uvm regression 28 08 23 12 27 54

12:28 (init) preparing to check out these repositories at the latest revisions:

12:28 (init) $START PWD/git repo/selected demo.git at 7ae9104d1b6c73e7b8f41ab76c75bb1890d5d6ab (latest). Earliest is a3b3e6227ea9ea1697c1de61e8ecc6fc75348c33

12:28 (init)

checking out revision for test (from a monolithic repository)

12:28 (init)

to folder: /servers/noivl-amodk/Amodk/VERISIUM/BUGLOC/23 05 demos/pindowndemos 22 06 23 15 38 22/regressionflows/vmrunner/vmrunner pindownafterregression/workdir/checkoutarea/test

12:28 (init)

checkout done

12:37 (init) Completed: Test suite has completed. Requested session has completed (completed).

12:37 (init) Summary of job completion: All 1 jobs PinDown was waiting for have completed. Waited 8 min (Aug 28 12:37 PM)

12:38 (debug iteration1/try1) Now PinDown will run these debug tests:

12:38 (debug iteration1/try1) 7ae9104d1b apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) 0845b1310b apb_to_uart_1stopbit_seed_-1511915075 (id=34209793)

12:38 (debug iteration1/try1) c47f9b8772 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) f094657344 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) 84c80e7cc2 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) 06aa417e24 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) a3b3e6227e apb to uart 1stopbit seed -1511915075 (id=34209793)

12:38 (debug iteration1/try1) 7ae9104d1b apb to uart 1stopbit seed -1511915075 (id=34209793), patch 84c80e7cc2 -> 06aa417e24 (validating, speculative)

12:38 (debug iteration1/try1) 7ae9104d1b apb to uart 1stopbit seed -1511915075 (id=34209793), patch 9617a41238 -> 7f89e2d69a (validating, speculative)

12:38 (debug iteration1/try1) 7ae9104d1b apb to uart 1stopbit seed -1511915075 (id=34209793), patch 6a1fd365ad -> c47f9b8772 (validating, speculative)

12:38 (debug iteration1/try1) checking out revision requested for debug (from a monolithic repository)

12:38 (debug iteration1/try1) checkout done

12:41 (debug iteration1/try1) Completed: Debug phase pindownID1 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID2 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID3 has completed. Requested session has completed (completed).

12:41 (debug iteration1/trv1) Completed: Debug phase pindownID4 has completed. Requested session has completed (completed).

12:41 (debug iteration1/trv1) Completed: Debug phase pindownID5 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID6 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID7 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID8 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID9 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Completed: Debug phase pindownID10 has completed. Requested session has completed (completed).

12:41 (debug iteration1/try1) Summary of job completion: All 10 jobs PinDown was waiting for have completed. Waited 2 min (Aug 28 12:41 PM)

12:41 (debug iteration2/try1) fail 7ae9104d1b apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) fail 0845b1310b apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) fail c47f9b8772 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) fail f094657344 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) fail 84c80e7cc2 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) pass 06aa417e24 apb to uart 1stopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/try1) pass a3b3e6227e apb to uart lstopbit seed -1511915075 (id=34209793)

12:41 (debug iteration2/tryl) pass 7ae9104dlb apb to uart 1stopbit seed -1511915075 (id=34209793), patch 84c80e7cc2 -> 06aa417e24 (validating speculative)

12:41 (debug iteration2/tryl) fail 7ae9104dlb apb to uart 1stopbit seed -1511915075 (id=34209793), patch 9617a41238 -> 7f89e2d69a (validating, speculative)

12:41 (debug iteration2/try1) fail 7ae9104dlb apb to uart 1stopbit seed -1511915075 (id=34209793), patch 6a1fd365ad -> c47f9b8772 (validating, speculative)

12:41 (debug iteration2/try1)

12:41 (debug iteration2/try1) Bug reported /servers/noivl-amodk/VERISIUM/BUGLOC/23 05 demos/pindowndemos 22 06 23 15 38 22/regressionflows/vmrunner /vmrunner pindownafterregression/workdir/runarea/test/run5/pindownlogs/text/bugs/h

l/regression/validated/bug no C1

12:41 (debug iteration2/try1) Bug reported /servers/noivl-amodk/VERISIUM/BUGLOC/23 05 demos/pindowndemos 22 06 23 15 38 22/regressionflows/vmrunner pindownafterregression/workdir/runarea/test/run5/pindownlogs/text/bugs/h

l/regression/validated/bug no C1

12:41 (debug iteration2/try1) Email report generated: /servers/noivl-amodk/VERISIUM/BUGLOC/23 05 demos/pindowndemos 22 06 23 15 38 22/regressionflows/vmrunner pindownafterregression/workdir/runarea/test/run5/pindownlogs/

xt/mail/sent 1.html

12:41 (debug iteration2/try1) PinDown debug has finished.

```

DESIGN AND VERIFICATION

CONFERENCE AND EXHIBITION

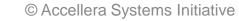

# Verisium Waveminer

## WaveMiner simplifies Regression Debug

Several IP level changes in between the **passing** and the **failing SoC** regression runs

### Launching Verisium WaveMiner

verisium -waveminer -wavepath\_new <path to the new waveform> -xmlibdirpath\_new <path to the new snapshot> -wavepath\_golden <path to reference waveform> -xmlibdirpath\_golden <path to the reference snapshot>

#### Verisium WaveMiner Report

INFO (IWM003): Extracting signal information for waveform processing. WARNING (WWM001): Unable to find signal tb.myFifo.memory. INFO (IWM010): Found 9 from 10 signals to process. INFO (IWM014): Starting clock detection. INFO (IWM012): Detected clock "tb.myFifo.clk", and it will be used for 9 signals (number of clock events = 161). INFO (IWM004): Building groups of signals for signature mining. INFO (IWM005): Loading first batch of waveforms (total = 1). INFO (IWM011): Loading waveform: good/ida.db/ida.shm. INFO (IWM011): Wave "good/ida.db/ida.shm" has 79 cycles (simulation end time: 795, size: 0MB). INFO (IWM006): Performing signature mining on loaded waveforms. INFO (IWM005): Loading second batch of waveforms (total = 1). INFO (IWM011): Loading waveform: bad/ida.db/ida.shm. INFO (IWM011): Wave "bad/ida.db/ida.shm" has 79 cycles (simulation end time: 795, size: 0MB). INFO (IWM006): Performing signature mining on loaded waveforms. INFO (IWM007): Finding most relevant signals and their corresponding time points. INFO (IWM008): Returning top 2 signals. tb.myFifo.rptr 770ns, good/ida.db/ida.shm, bad/ida.db/ida.shm 790ns, good/ida.db/ida.shm, bad/ida.db/ida.shm 110ns, good/ida.db/ida.shm, bad/ida.db/ida.shm (2) tb.myFifo.DATAOUT 790ns, good/ida.db/ida.shm, bad/ida.db/ida.shm 10ns, good/ida.db/ida.shm, bad/ida.db/ida.shm

> WaveMiner generates ranked list of signals based on waveform analysis and ranks the timepoints also to help narrow down the debug and opens Verisium Debug Window for further debugging

> > DESIGN AND VERIFICATION

## Verisium WaveMiner Demo

[amodk@nofcsl062 SHM\_DB\_TESTCASE]\$ ls

sad diff\_verisium\_debug\_logs golden\_verisium\_debug\_logs good run\_wave\_miner\_shm\_probe.tcl src waveminer.workdir

[amodk@nofcsl062 SHM\_DB\_TESTCASE]\$ ./run\_wave\_miner

DESIGN AND VERIFICATION

# Verisium WaveMiner Performance

| Waveform DB's | Size                         | WaveMiner Analysis Time |

|---------------|------------------------------|-------------------------|

| Waveform DB 1 | Golden – 1GB, Diff – 850MB   | ~ 20 min                |

| Waveform DB 2 | Golden – 26 GB , Diff – 25GB | ~ 35 min                |

| Waveform DB 3 | Golden - 46GB, Diff - 43GB   | ~ 15 min                |

| Waveform DB 4 | Golden – 648MB, Diff – 702MB | ~57 min                 |

The analysis time taken for generating results is dependent on multiple factors like size of the waveform, number of signals to analyze and total activity happening on each signal of interest.

# Verisium Platform 1.0 in Action

## Agenda

#### Potential for 10X improvement in debug productivity

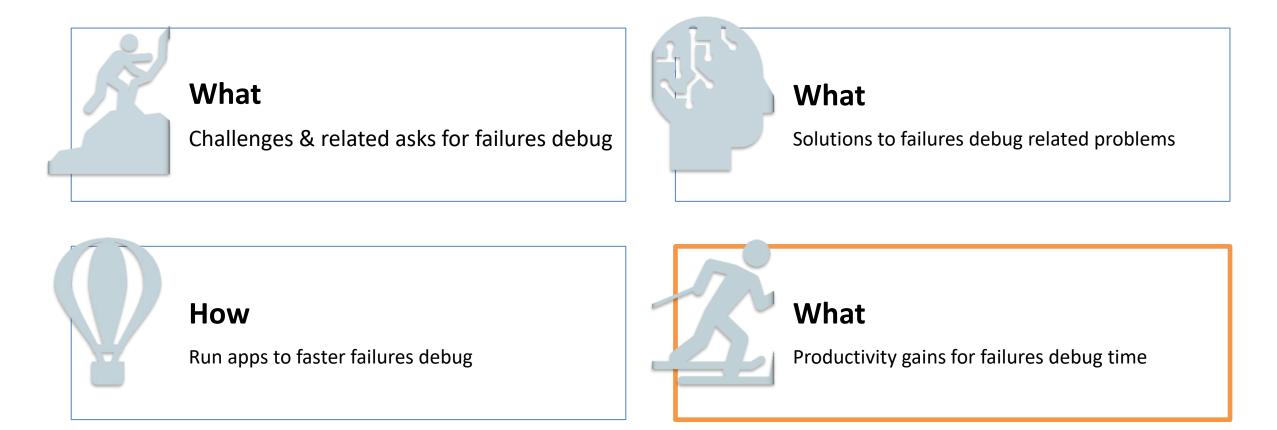

# Samsung Collaboration

C2023

#### **VERISIUM APPS Collaboration with Samsung**

#### cādence

#### Verisium Results

- To validate the tool Mid Level Complexity IP(~100k gate count)

- Results

| Complexity of Failure | Debug time without<br>tool(Minutes) | Debug time with<br>tool(Minutes) | Debug gain  |

|-----------------------|-------------------------------------|----------------------------------|-------------|

| Less                  | 30                                  | 20                               | 1.5X        |

| Less                  | 40                                  | 25                               | <b>1.6X</b> |

| Moderate              | 60                                  | 40                               | 1.5X        |

| Moderate              | 80                                  | 45                               | 1.7X        |

| Hard                  | 130                                 | 70                               | 1.85X       |

| Hard                  | 135                                 | 80                               | 1.7X        |

cādence

# Q & A