# An Enhanced DV Approach for Effectively Verifying High **Speed, Low Power MIPI-MPHY 5.0 Designs**

Eldhose PM (eldhose.pm@samsung.com), Kuntal Pandya (k.pandya@samsung.com), Sagar Jayakrishanan (sagar.j@samsung.com), Suraj Vijay Shetty(shetty.suraj@samsung.com), Parag S Lonkar (parag.lonkar@samsung.com) Samsung Semiconductor India Research, Bangalore, India

## UNITED STATES

SAN JOSE, CA, USA FEBRUARY 27-MARCH 2, 2023

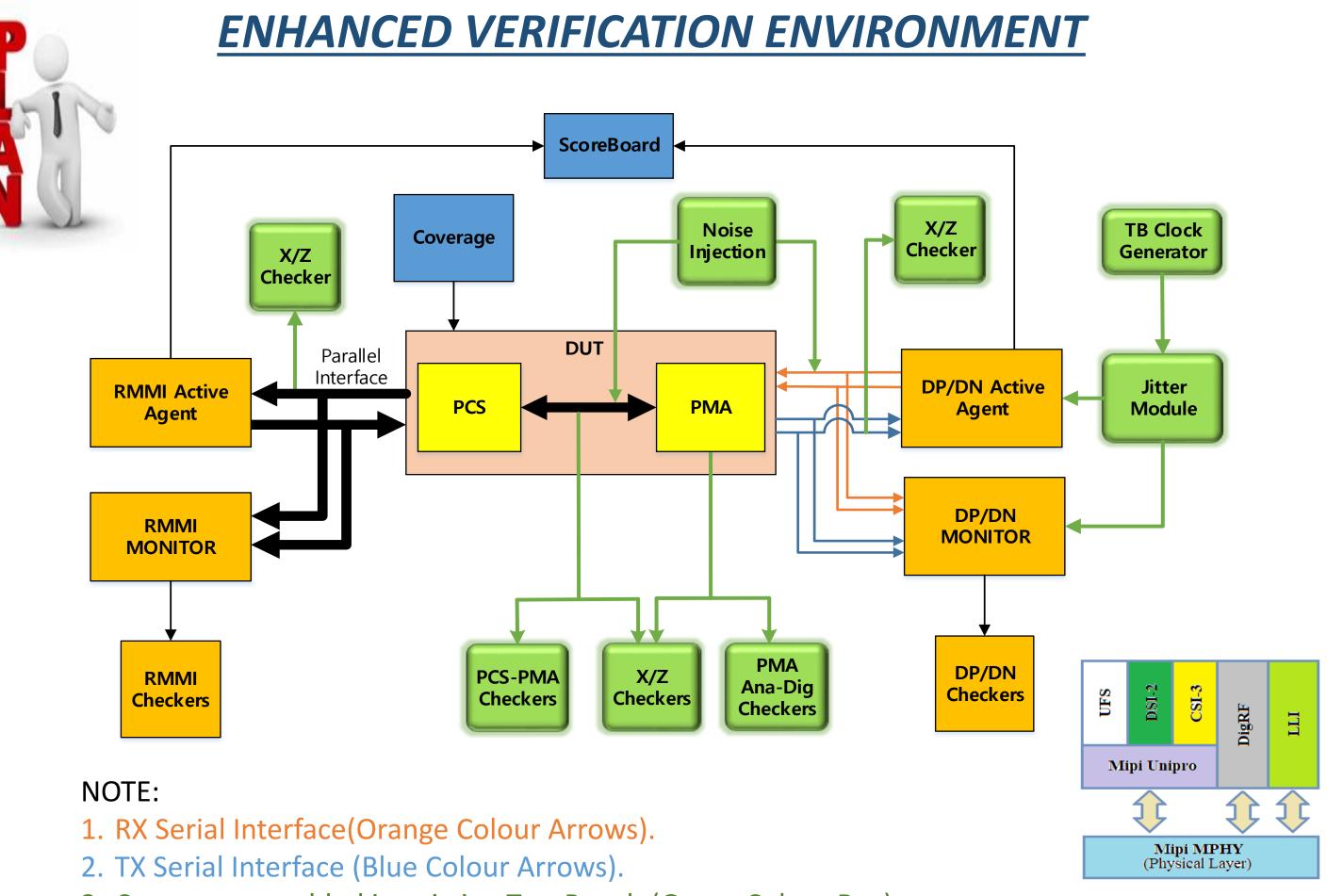

3. Components added in existing Test Bench (Green Colour Box).

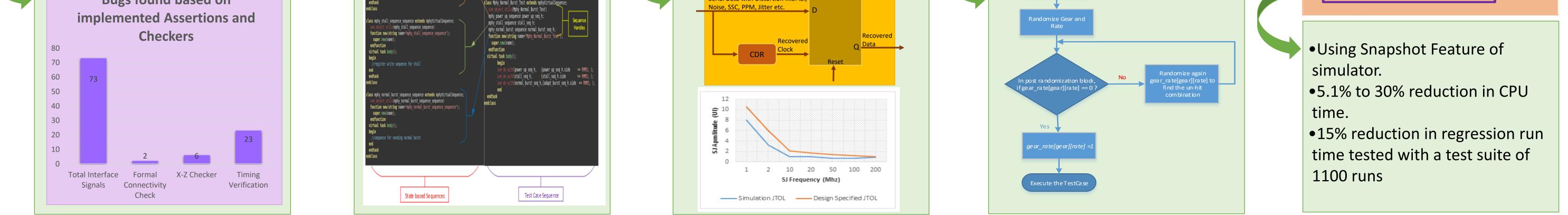

| Interface Connectivity and Timing<br>Checks                                                                                                                            |  | FSM Based Scalable Test Bench<br>Architecture                                      |    | Jitter Module for CDR Stress<br>Testing                                                                                                                                  | Approach for faster Functional<br>Coverage Closure                                                                                                                                 |  | Increasing Regression Throughput<br>using EDA Tool                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>MPHY Design consists of PCS and<br/>PMA (Analog-Digital) Interface.</li> <li>Signal Connectivity and protocol<br/>related checks across I/F become</li> </ul> |  | <ul> <li>Each MPHY FSM State is defined<br/>as a separate sub-sequence.</li> </ul> | 2d | <ul> <li>Critical to assure Receiver Logic works well within tolerance limits set by Protocol.</li> <li>Introducing Jitter/SSC/Noise on incoming Serial Data.</li> </ul> | <ul> <li>Test Case Ranking and custom regression suite generation</li> <li>An array based coverage collection. Ex:</li> <li>Supported Gear = {1,2,3,4,5}, Rate = {0,1};</li> </ul> |  | Power-Up Sequence + Hibern8 Exit (1.5ms wait<br>time)<br>Update of INLINE configuration<br>settings during SLEEP or STALL<br>after Re-Configuration Trigger (RCT)<br>UIF-Z<br>Power<br>Supply<br>On<br>USABLED<br>VIF-P for Tuxe |

| mandate.<br>Bugs found based on                                                                                                                                        |  | <pre>class mphy_power up_sequence extends mphyVirtualSequence;</pre>               |    |                                                                                                                                                                          |                                                                                                                                                                                    |  |                                                                                                                                                                                                                                  |

Frequency

Offset

+300ppm

0

#### High Precision Analog Models

• MPHY PMA is a typical AMS Design.

•Analog behavior is modelled in a way to closely mimic the real functionality for digital simulation purpose using 3<sup>rd</sup> party utility.

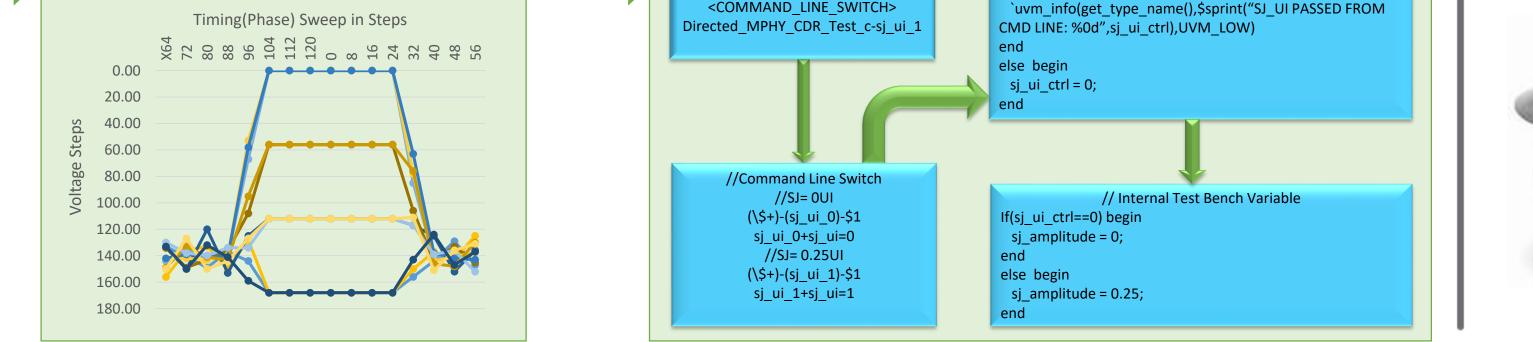

Parameterized Test Sequences

Reproduction of scenario needs Test Bench change and compilation. RJ SJ Maintenance and functional 0 coverage closure with such Test 0.12UI 0.25UI Bench architecture is difficult.

> stead of `define macro, \$value\$plusargs API is used to set a value for reproducing scenario. If(\$value\$plusargs ("sj\_ui=%d",sj\_ui\_ctrl)) begin

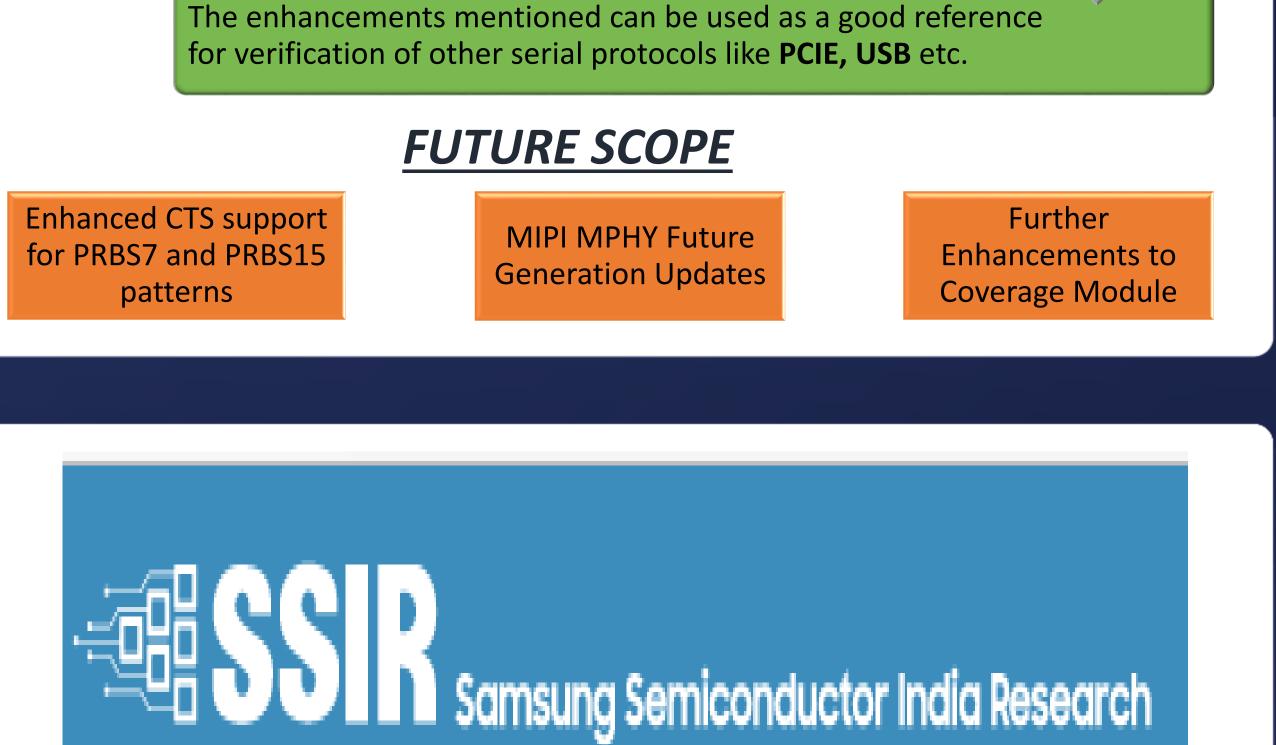

### **CONCLUSIONS**

Test Bench has become **efficient and effective** in fulfilling Design requirements.

Unearth some really critical **bugs**, which could have led to excess power consumption.

> Regressive CDR testing ensured high quality Jitter Tolerant Receiver.

Runtime switches, save and restore option, coverage handling helped in **on-time** verification closure.

EOM Plot

yntax to pass command line switch:

<TEST NAME>-

### © Accellera Systems Initiative

REFERENCES

mipi\_M-phy\_specification\_v5-0.pdf, by MIPI Alliance

• SystemVerilog 3.1a Language reference Manual

• https://www.academia.edu/30128384/SERDES\_Rx\_CDR\_Verification\_using\_Jitter\_Spread\_spectrum\_clocking\_SSC\_stimulus