#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

### Gherkin Implementation in SystemVerilog Brings Agile Behavior-Driven Development to UVM

William L. Moore

Paradigm Works

## The Problem with Documentation

- Static

- Asynchronous

- Separate

- Richly formatted

- Specialized

- Causes bugs!

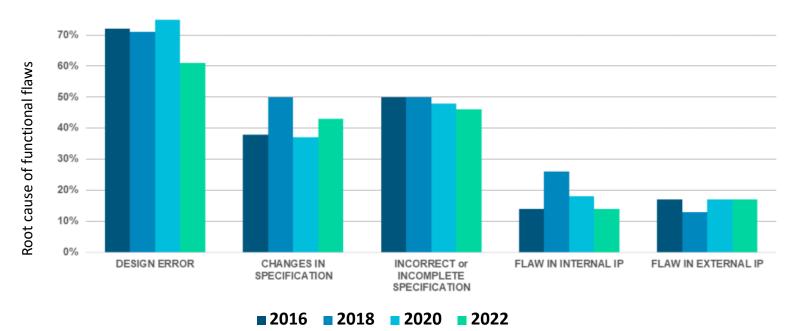

#### **Root cause of ASIC functional flaws**

Source: Wilson Research Group and Siemens EDA, 2022 Functional Verification Study Unrestricted |© Siemens 2022 | Functional Verification Study

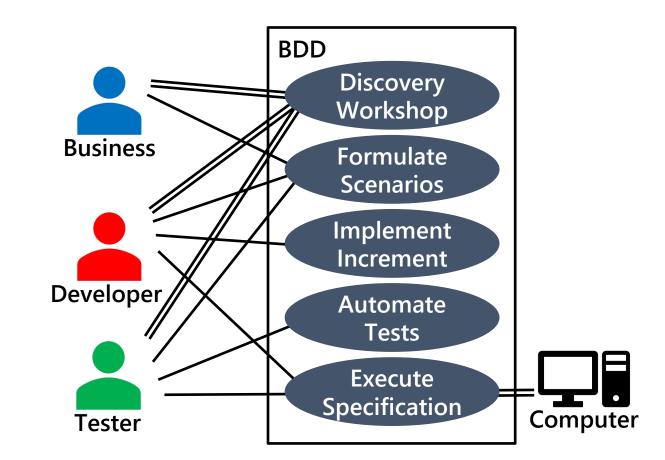

## Behavior-Driven Development (BDD)

- Agile software methodology

- Team collaboration and communication

- Concrete examples

- Natural language text files

- Automated executable specifications

- Living documentation

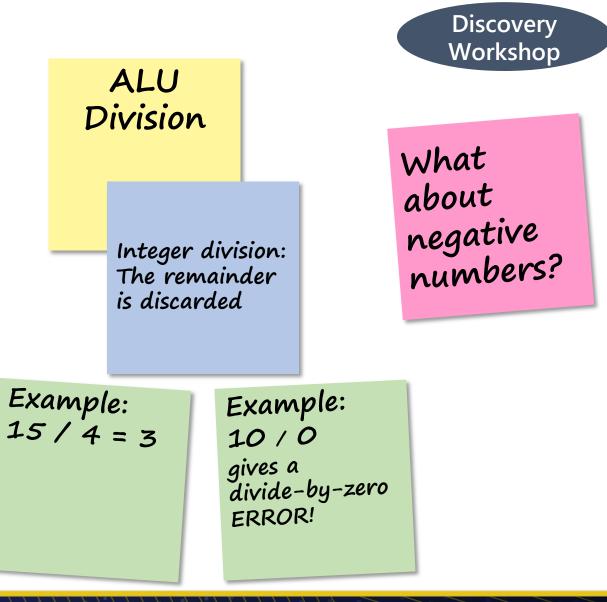

## Illustrative Example

- Arithmetic logic unit (ALU)

- Integer division feature

- Behavior

- Corner cases and exceptions

- Examples

- Questions

## Gherkin

- Executable specification AKA feature file

- Open-source domain-specific language

- Plain text file

- Natural language

- Keywords provide structure

- Given-When-Then steps

# This Gherkin feature file's name is alu\_division.feature

Feature: Arithmetic Logic Unit division operations

The arithmetic logic unit performs integer division.

Scenario: In integer division, the remainder is discarded Given operand A is 15 and operand B is 4 When the ALU performs the division operation Then the result should be 3 And the DIV\_BY\_ZERO flag should be clear

Scenario: Attempting to divide by zero results in an error

Given operand A is 10 and operand B is 0

When the ALU performs the division operation

Then the DIV\_BY\_ZERO flag should be raised

**Formulate**

**Scenarios**

## **BDD** for Silicon Projects

- RTL and verification environments are code

- Same roles in silicon as software

- Different increments

- Feature could be a verification component

- No native SystemVerilog support for Gherkin

- Until...

### Bathtub

- Pure native SystemVerilog library

- Built on UVM

- Runs in simulator

- Parses Gherkin files

- Executes specification against DUT

- Runs virtual sequences on environment's sequencer

BDD **A**utomated Tests Helping Teams Understand **B**ehavior

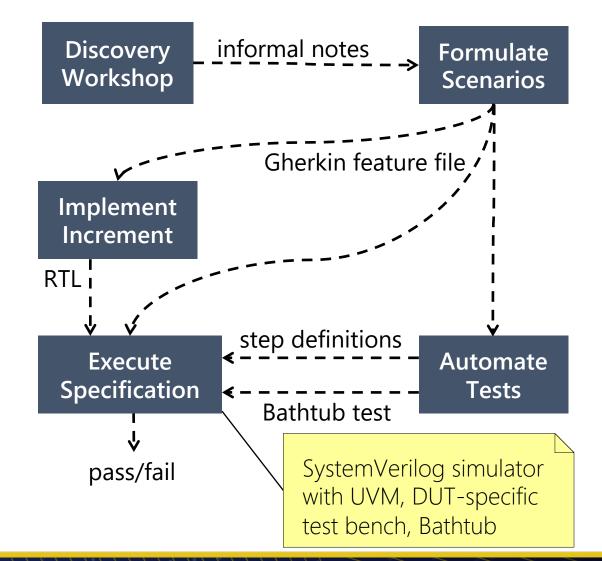

## Bathtub Flow

- Map Gherkin steps to SystemVerilog tasks

- Encapsulate tasks, assertions in UVM sequences

- Parameterized step definitions

- Class needed for every step

- Write a Bathtub UVM test

- Instantiate bathtub object

- Configure with feature file names and virtual sequencer

- Compile and simulate until tests pass

### Sample Step Definition

```

// Given operand A is 15 and operand B is 4

```

class set\_operand\_A\_and\_B\_vseq extends alu\_base\_vsequence implements bathtub\_pkg::step\_definition\_interface;

`Given("operand A is %d and operand B is %d")

```

int operand_A, operand_B;

```

```

`uvm_object_utils(set_operand_A_and_B_vseq)

function new (string name);

super.new(name);

```

endfunction : new

```

virtual task body();

// Extract the parameters

`step_parameter_get_args_begin()

operand_A = `step_parameter_get_next_arg_as(int);

operand_B = `step_parameter_get_next_arg_as(int);

`step_parameter_get_args_end

```

// Do the work using the API in the base sequence super.set\_operand\_A(operand\_A); super.set\_operand\_B(operand\_B); endtask : body endclass : set operand A and B vseq

Automate

Tests

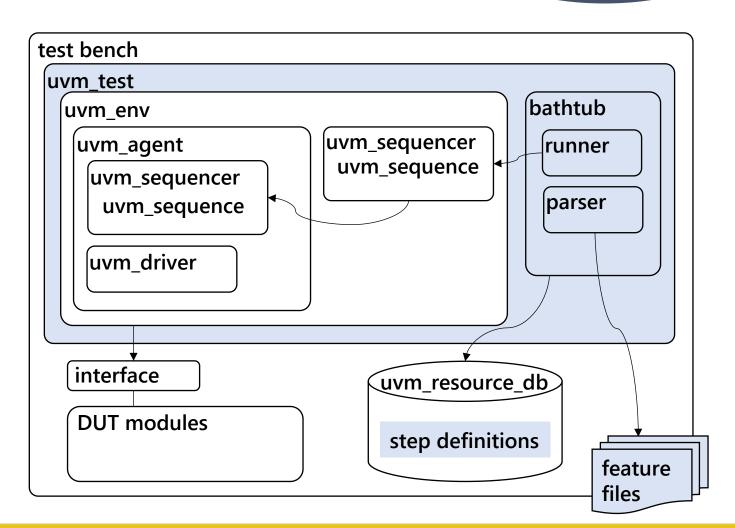

## Bathtub and UVM

- Shaded regions are Bathtub-specific

- Unshaded regions are reused unchanged

- Resource database stores step definitions

- Bathtub parses Gherkin, collects steps

- Runs step definitions on virtual sequencer

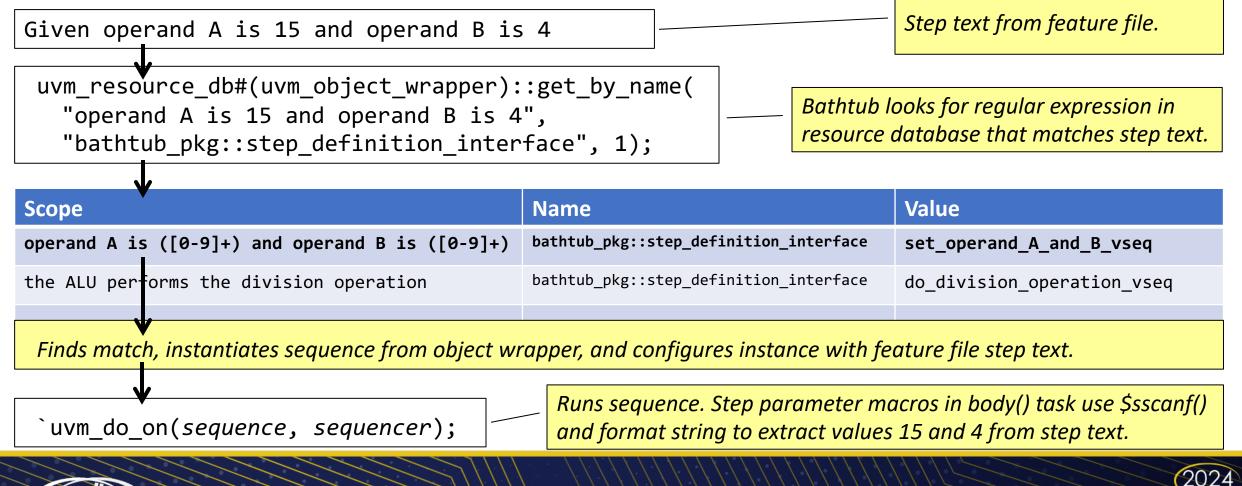

#### Bathtub Operation at Time Zero

Given("operand A is %d and operand B is %d")

Macro with parameterized template string from step definition.

uvm\_resource\_db#(uvm\_object\_wrapper)::set(

"operand A is ([0-9]+) and operand B is ([0-9]+)",

"bathtub\_pkg::step\_definition\_interface",

set\_operand\_A\_and\_B\_vseq::get\_type());

Bathtub converts "%d" to regular expression "([0-9]+)" and stores the step definition object wrapper in the resource database. The name is a constant.

| Scope                                           | Name                                              | Value                                  |

|-------------------------------------------------|---------------------------------------------------|----------------------------------------|

| operand A is ([0-9]+) and operand B is ([0-9]+) | <pre>bathtub_pkg::step_definition_interface</pre> | <pre>set_operand_A_and_B_vseq</pre>    |

| the ALU performs the division operation         | <pre>bathtub_pkg::step_definition_interface</pre> | <pre>do_division_operation_vseq</pre>  |

| The result should be ([0-9]+)                   | <pre>bathtub_pkg::step_definition_interface</pre> | check_result_vseq                      |

| The DIV_BY_ZERO flag should be (\S*)            | <pre>bathtub_pkg::step_definition_interface</pre> | <pre>check_DIV_BY_ZERO_flag_vseq</pre> |

#### Bathtub Runtime Operation

### Bathtub Results

- Ran on two SoC project blocks

- Success from discovery workshop to regression

- BDD is not verification, but dovetails

- Feature file & step definition advantages, challenges

- Communication, planning, reuse, debug benefits

- Power of SystemVerilog language

- Available open-source at <a href="https://github.com/williaml33moore/bathtub">https://github.com/williaml33moore/bathtub</a>

#### Questions

# Thank you!