# **Achieving End-to-End Formal Verification** of Large Floating-Point Dot Product Accumulate Systolic Designs

Emiliano Morini, Bill Zorn, Disha Puri, Madhurima Eranki, Shravya Jampana **Intel Corporation**

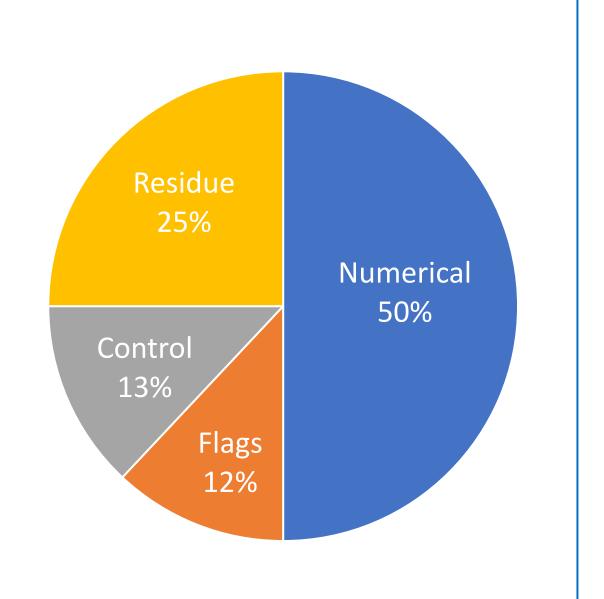

#### Mathematical Functionality $R^{m,p}$ DPn.5 2n + 1 floats with precision t $2^{(2n+1)t+2}$ input 4 rounding modes values for each $r_{ii}$ DP4.5 DP4.5 DP4.5 DP8.5 DP8.5 DPn.5 **Precision** 32 64 Usually implemented in Input Dot Product Accumulate Systolic units 2578 2546 $2^{290}$ $2^{146}$ 21090 Space Hard to verify due to the **massive input space** and the **arithmetic** involved

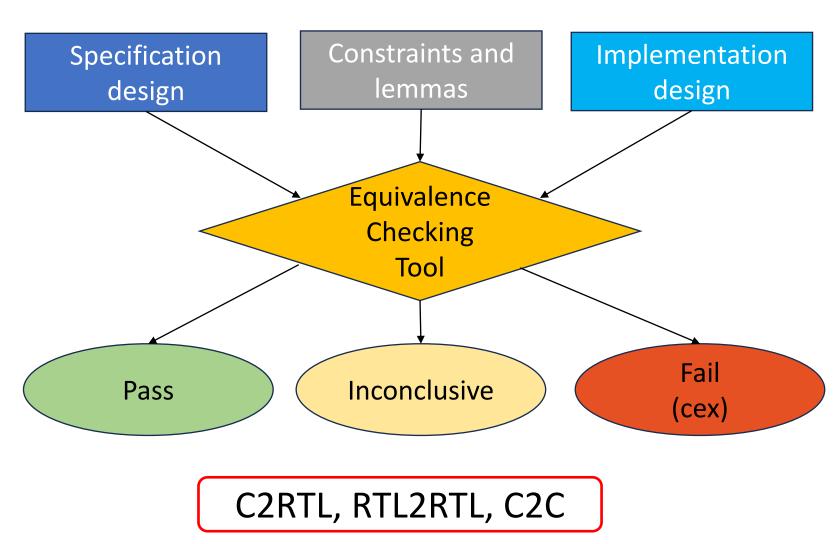

### Formal Verification Approach: Equivalence Checking

### C2RTL for $r_{11}$ : Double Precision Complexity

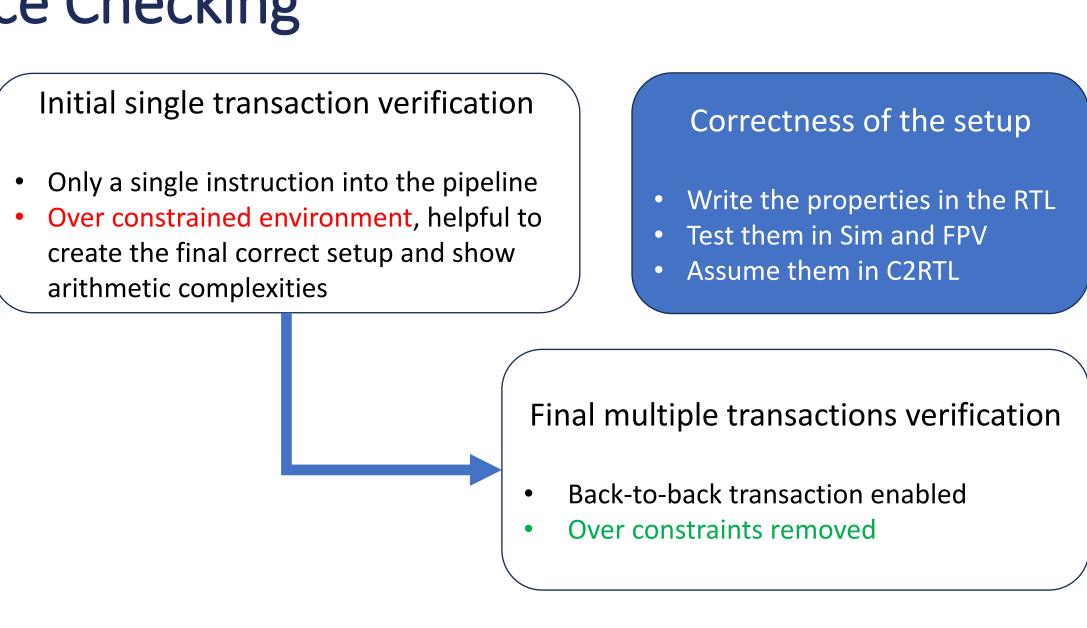

Inclusive results out of the box, **proof decomposition** required

Internal equivalence points between C++ and RTL are unlikely, due to the RTL optimizations.

Find **equivalent relations** among multiple signals:

impl.prod == (spec.prod << spec.ren)

Abstract the design introducing cutpoints based on the relations proven

Vast usage of case-splits and assume-guarantee approaches

Due to RTL optimizations, the double precision multiplication involved in a DPn.5 was inconclusive.

Convergence achieved using the EC tool as an automatic theorem, proving these steps:

- Encoding

- Array creation

- Array reduction

- CSA form

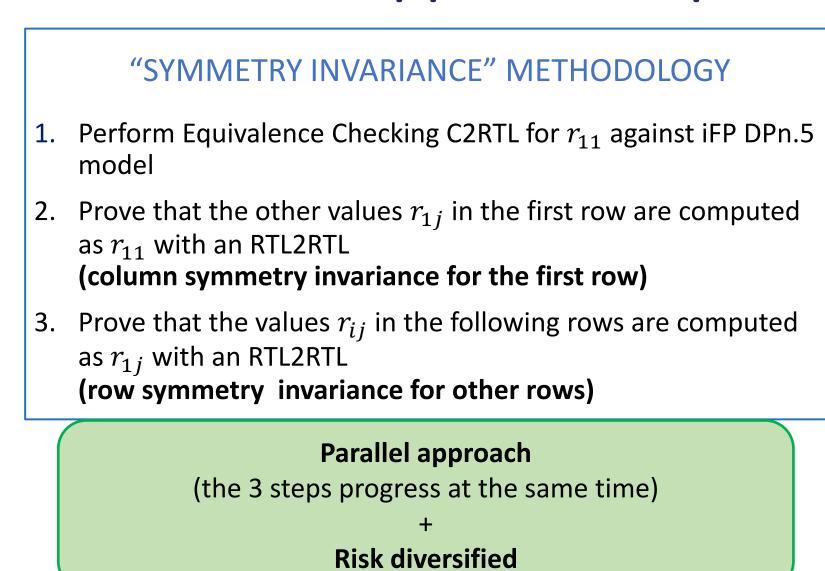

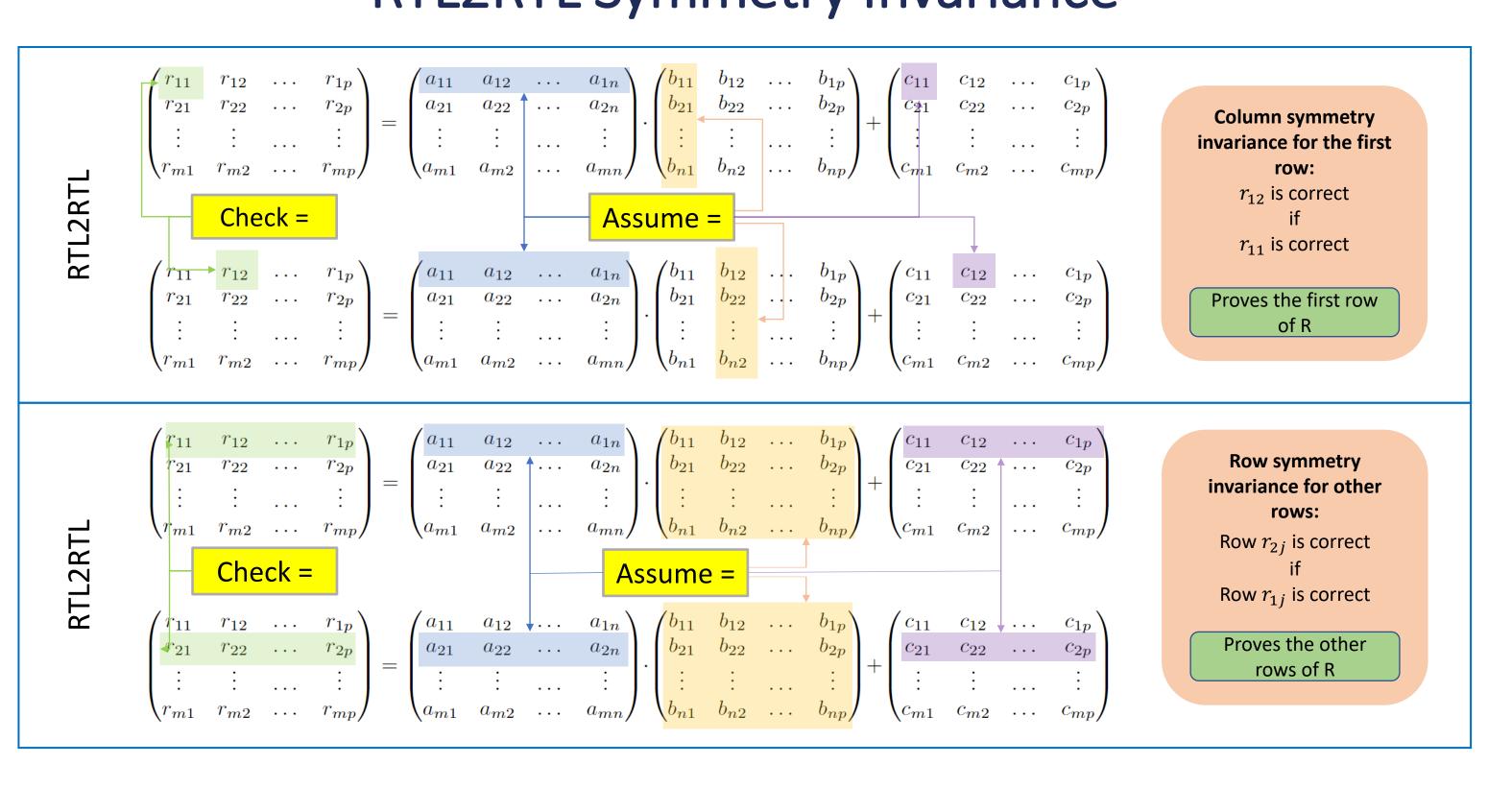

## RTL2RTL Symmetry Invariance

### Results & Conclusions

#### **Bugs found during the process**

- Good initial results with bug hunting approaches (e.g., constrain most of the mantissas of the inputs to 0)

- Detected hard corner cases, happening with a probability of less than  $2^{-50}$ , practically impossible to find via random sim!

#### Proven the absence of bugs in the final RTL

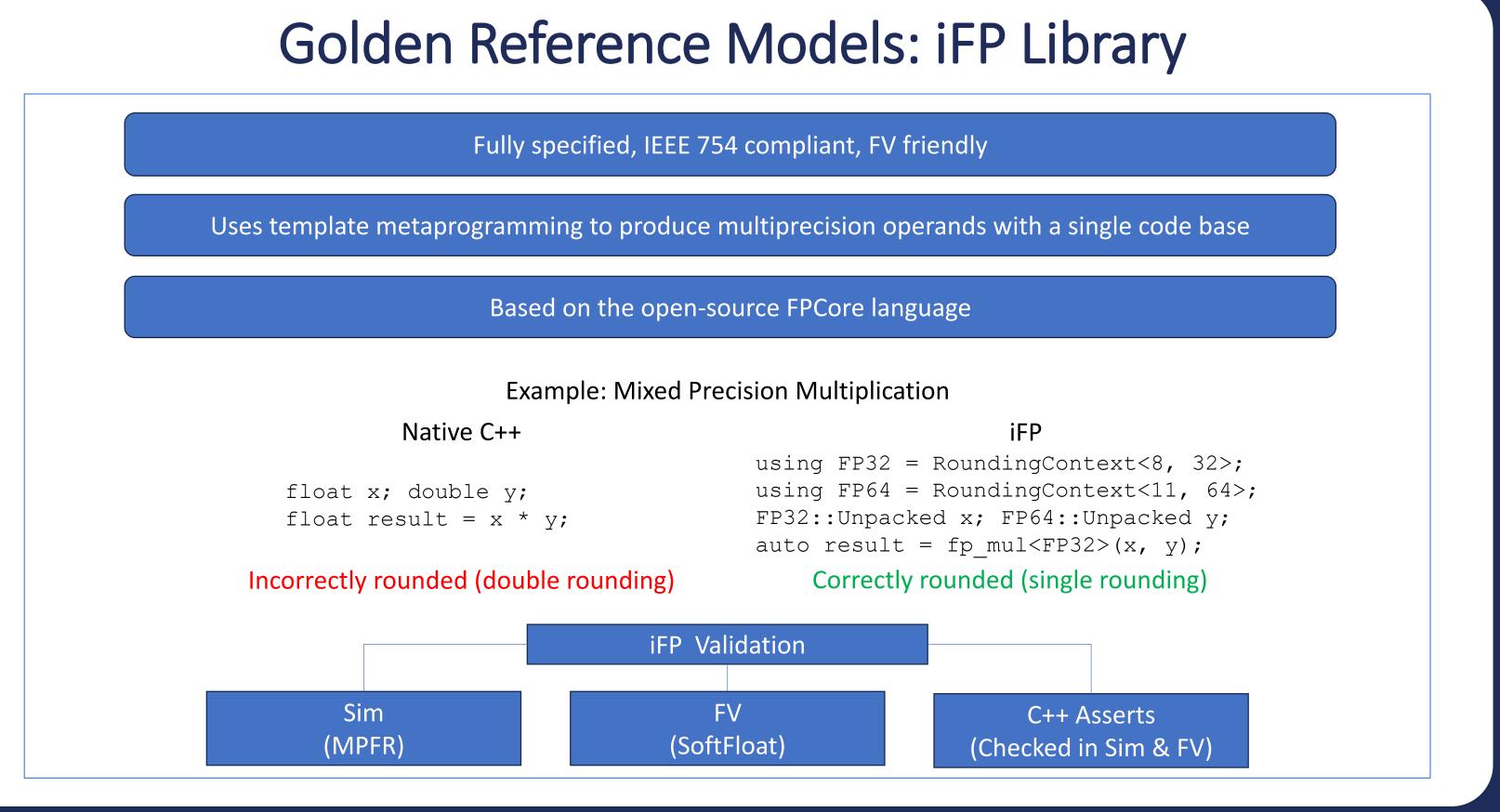

Completed formal equivalence between RTL and iFP C++ model (independent, validated and FV friendly) + Symmetry techniques

### Our approach

- Scales up to designs with hundreds of input bits

- Can be reused to verify similar components

- Enables a **shift left** for every future generation of RTL

- Fully verifies large double precision DPAS in < 24h

- Is used in for **regressions** (smoke testing and weekly)

We developed advanced proofs leveraging RTL, computer arithmetic and FV skills,

obtaining results never been achieved before