SYSTEMS INITIATIVE

# A HARDWARE AND SOFTWARE INTEGRATED POWER OPTIMIZATION APPROACH WITH POWER AWARE SIMULATIONS AT SOC

Eldin Ben Jacob (eldin.jacob@samsung.com), Harshal Kothari (harshal.k1@samsung.com), Sriram Kazhiyur Soundarrajan (sriram.k.s@samsung.com), Somasunder Kattepura Sreenath (soma.ks@samsung.com) Samsung Semiconductors India Research, Bangalore, India

TESTED

## UNITED STATES

SAN JOSE, CA, USA FEBRUARY 27-MARCH 2, 2023

0%

### INTRODUCTION

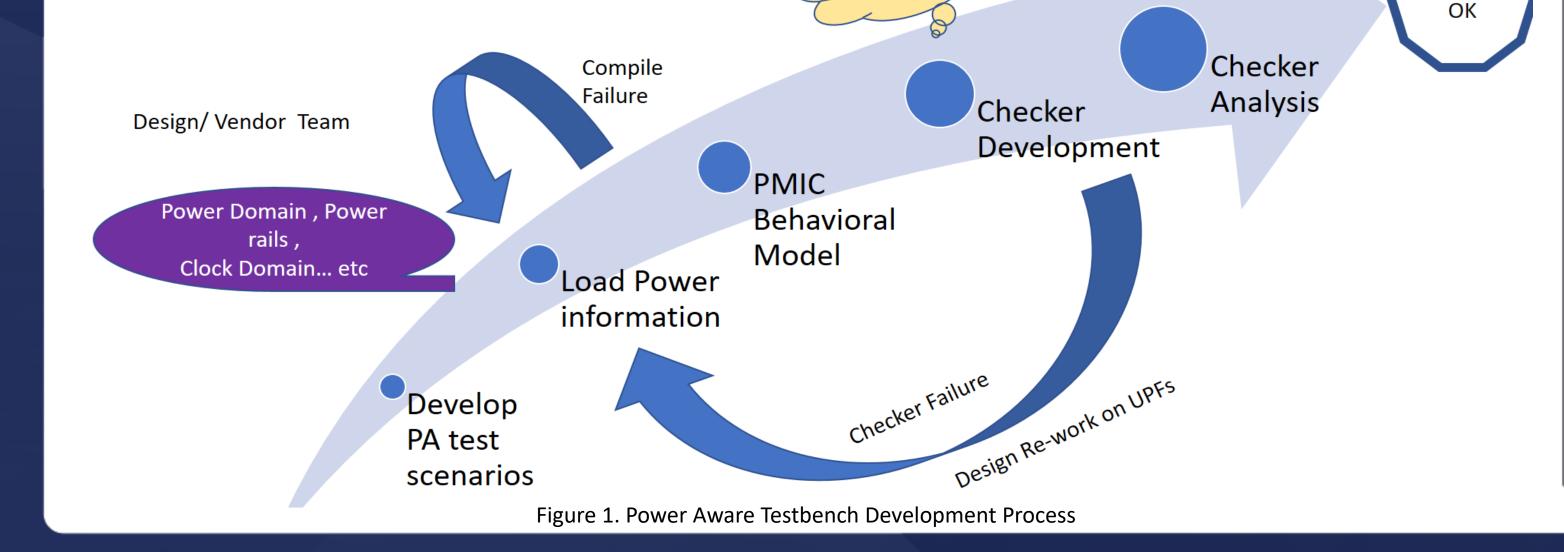

A systematic approach is inculcated to target an efficient and smooth verification flow for low-power simulations for large SOCs. Analysis of power/voltage/clock domains

→ Defining verification scope One time compile  $\rightarrow$  Loading the power information of design PMIC controller

→ Mimic the behavior in the test bench Power operations isolation, level shifters, retention -> Checkers to reinforce

Isolation/Retu

**PROPOSED METHODOLOGY**

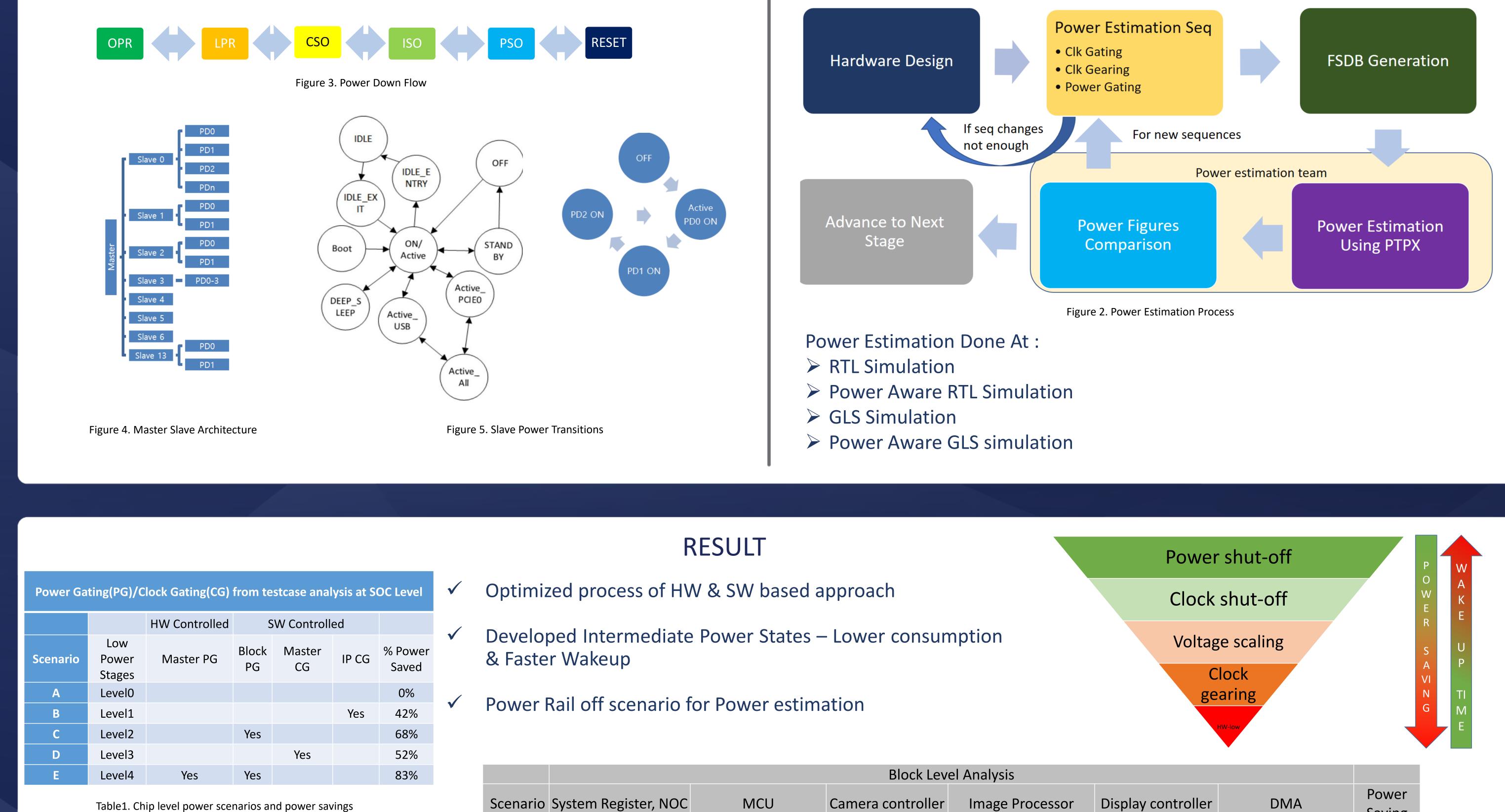

$\succ$  Variable voltage level  $\rightarrow$  Operating from 0.6V to 3.3V.

- Switchable power supplies Power gating

- $\succ$  Clock shut off  $\rightarrow$  Clock gating when PD is idle.

- $\succ$  Isolation cells  $\rightarrow$  Avoid leakage to nearby PDs.

- > Level shifters -> Sampling signals that cross voltage levels.

- Retention Data saved during power shut off and restored during power on

## POWER CONTROLLER ACHITECTURE AND POWER STATES

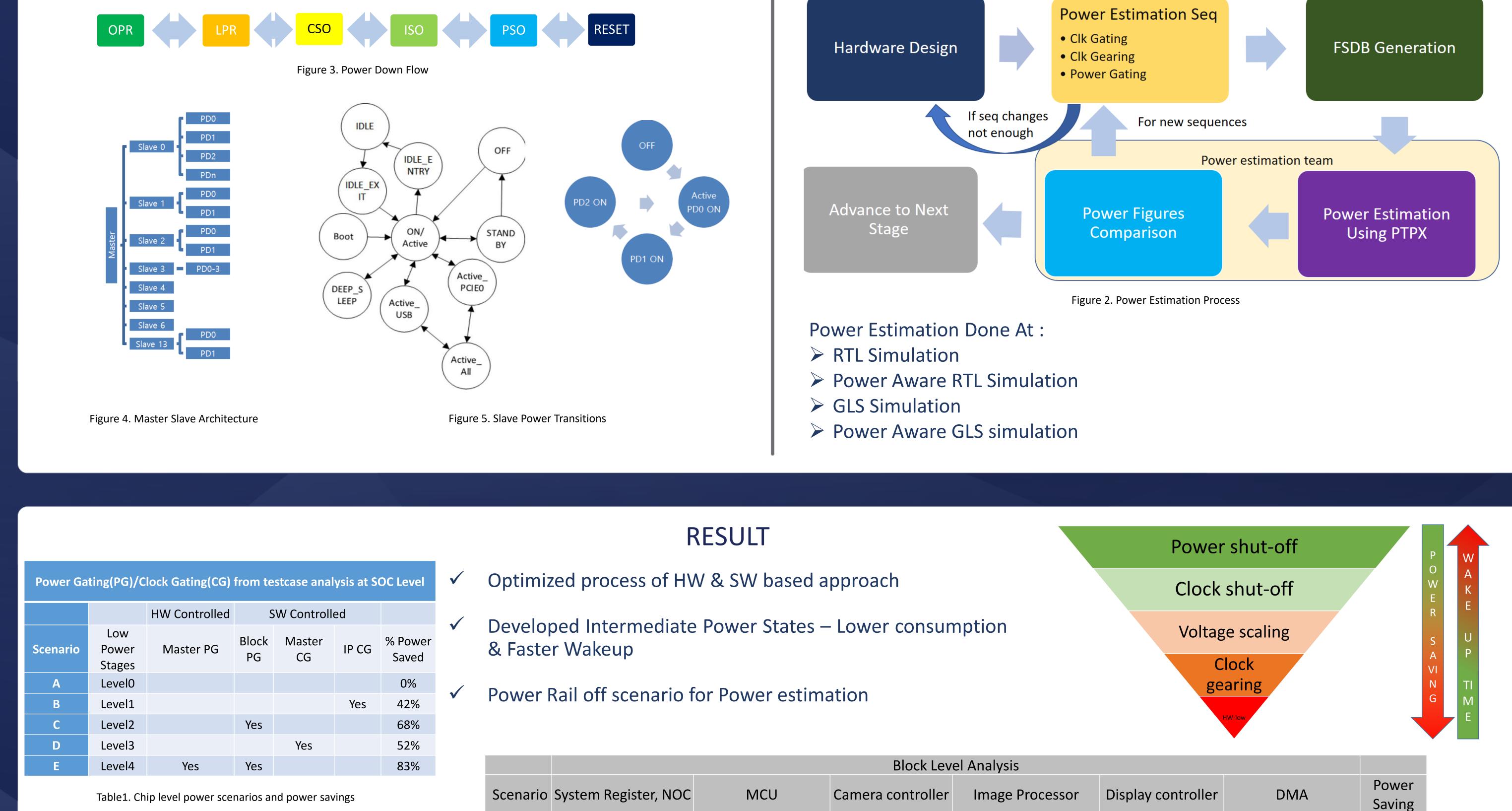

#### **POWER ESTIMATION PROCESS**

|          | Block Level Analysis |                 |                   |                 |                    |                |

|----------|----------------------|-----------------|-------------------|-----------------|--------------------|----------------|

| Scenario | System Register, NOC | MCU             | Camera controller | Image Processor | Display controller | DMA            |

| А        | FC, NOP (100Mhz)     | FC,NOP (800Mhz) | FC,NOP(800 Mhz)   | FC,NOP(800Mhz)  | FC,NOP (800Mhz)    | FC,NOP (800Mhz |

| -        |                      |                 | Clock             | Clock           | Clock              | Clock          |

|                                                                   | В | FC, NOP (100Mhz) | FC,NOP (800Mhz)          | Clock           | Clock           | Clock           | Clock           | 10%  |

|-------------------------------------------------------------------|---|------------------|--------------------------|-----------------|-----------------|-----------------|-----------------|------|

|                                                                   | D |                  |                          | gearing(100Mhz) | gearing(100Mhz) | gearing(100Mhz) | gearing(100Mhz) | 1070 |

|                                                                   | С | FC, NOP (100Mhz) | FC,NOP (800Mhz)          | FC,NOP (800Mhz) | FC,NOP (800Mhz) | Clock Gating    | FC,NOP (800Mhz) | 25%  |

|                                                                   | D | FC, NOP (100Mhz) | FC,NOP (800Mhz)          | Clock Gating    | Clock gating    | Clock Gating    | Clock Gating    | 40%  |

|                                                                   | Е | FC, NOP (100Mhz) | Clock<br>Gearing(100Mhz) | Clock Gating    | Clock gating    | Power Gating    | Clock Gating    | 58%  |

|                                                                   | F | FC, NOP (100Mhz) | FC,NOP (800Mhz)          | Power Gating    | Power Gating    | Power Gating    | Power Gating    | 68%  |

|                                                                   | G | FC, NOP (100Mhz) | Clock Gated              | Power Gating    | Power Gating    | Power Gating    | Power Gating    | 79%  |

|                                                                   | Н | Clock Gated      | Power Gated              | Power Gating    | Power Gating    | Power Gating    | Power Gating    | 91%  |

| Table 3. Power saving in Block level Power down states/ Scenarios |   |                  |                          |                 |                 |                 |                 |      |

| LEAK POWER                            | IDLE POWER | POWER GATED IDLE |  |  |  |  |  |

|---------------------------------------|------------|------------------|--|--|--|--|--|

| 40MW                                  | 5.99MW     | 0.58MW           |  |  |  |  |  |

| Table 2. Power figures at block level |            |                  |  |  |  |  |  |

#### REFERENCES

> Harshal Kothari, Eldin Ben Jacob, Sriram Kazhiyur Soundarrajan, Somasunder Kattepura Sreenath, "Challenges In Power-Aware Verification with Hardware Power Controller and Novel Approach to Harness Xcelium Low-Power Functional Coverage for Complex SoC", CadenceLive India 2021