# UVM Based Mixed-Signal Verification of a Display **PMIC Designed for OLED Display Applications**

Vijay Kumar & Adnan Malik

Samsung Semiconductor India Research

## INTRODUCTION (or REQUIREMENTS)

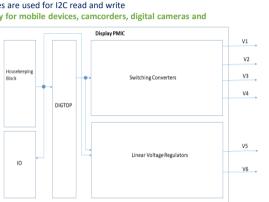

- The Display PMIC consists of Switching Converters, Housekeeping Circuits, viz., Reference voltage

- and Bias current generators, On-chip LDO and Clock generation unit Contains Protection logic circuits to guard it against various fault scenarios such as TSD, UVLO, SCP, IVP, OVP, UVP, OCD, SSD

- Comes with two slave addresses, each with its own set of register banks

- ۵

- One set of registers programmable by I2C protocol using the serial clock and data lines Another set of registers programmable by a separate set of lines

- ••• GPIO input decides which set of lines are used for I2C read and write

- Finds its applications in OLED power supply for mobile devices, camcorders, digital cameras and multimedia players

#### atures of the Display PMIC are:

- Adaptive power-on sequence &

- shutdown mode

- Fast discharge of outputs after shutdown

- Output high-Z by Always-On Display

- (AOD) mode

- Single-byte and multi-byte write & read through one of the I2C interfaces

- Soft-start with inrush current limitation Thorough protection by triggering

- interrupts against various fault scenarios

#### RESULTS

## SV-UVM ASSERTIONS TO CHECK THE STATUS REGISTERS AND CONVERTER OUTPUTS TO DISPLAY THE PASS/FAIL STATUS Checks for the status registers and converter outputs to display the pass/fail status

p\_sequencer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE1); //Enabling Converter 1 (Converters 2 & 3 are auto-enabled) #t\_converter\_1\_enable; p sequencer.i2c intf.I2C WRITE (SLAVE ADDR, REG1, VALUE2); //Enabling converters 4 & 5

converter 4 5 enable: //Converters 4 & 5 enable wait time and display all converter c isplay("%f %f %f %f %f", V\_Converter\_1, V\_Converter\_2, V\_Converter\_3, V\_Converter\_4, V\_Converter\_5);

//POK Registers Check

p\_sequencer.i2c\_intf.I2C\_READ (SLAVE\_ADDR, REG2, i2c\_rdata);

\$display("POK\_STATUS at %f = %h", \$time, i2c\_rdata); if(i2c rdata == expected data) uvm\_info(get\_full\_name(), "POK Good\n", UVM\_LOW)

rm\_error("MAIN\_CHIP", "POK Bad\n");

#### UVM TEST CASES FOR TRIGGERING FAULT SCENARIOS IN THE RNM MODELS

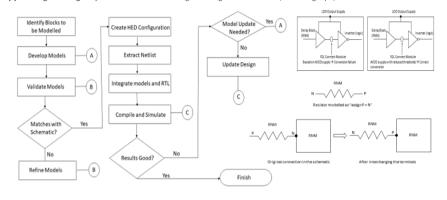

Since we use RNM and not the transistor level schematic, the fault scenarios may not occur in the simulation as we do not model those scenarios in the RNM. So in order to run test cases that check for the protection logic against such scenarios, we had to set the corresponding flag for each fault condition and see if the fault status registers and interrupt requests (IRQB) are triggered accordingly

sequencer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE1); //Enabling Converter 1 (Converters 2 & 3 are auto-enabled) #t\_converter\_1\_enable; //Converters 1-3 enable wait time

p\_sequencer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE2); //Enabling converters 4 & 5

142 test cases were completed on time with thi approach spanning across various scenarios:

Power-on and power-off

Write and read from dedicated clock and the work of the second s data lines or separate set of lines using I2C lock & Data protocol Dynamic Voltage Scaling ÷ Protection logic Pin connectivity checks between analog and Enables Outputs digita Level shifter checks across supply do 45 VAMS wreal models were developed and validated against the schematic 7-8 weeks TAT for the whole activity Regulators ON

## OBJECTIVES

- **D** To compile the major challenges faced in verifying the PMIC in a UVM based mixed-signal verification

- nt (MSV)

How we addressed those challenges?

Major challenges were:

(a) Handling interaction of signals between blocks at different abstraction levels (logic and real number) under different supply

(b) Mechanism to cover fault scenarios in a real number model (RNM) based Digital and Mixed-Signal (DMS) verification ronment with UVM, that are typically addressed in the transistor-level abstraction (c) Handling mixed-signal specific driver conflicts arising out of logic and real drivers, modelling style, etc

## RESULTS

#### #t\_wait\_time\_for\_flag\_set; //Wait time before setting the flag uvm\_hdl\_force("top.Main.I\_CONV\_1.OVP", 1'b1); //Triggering OVP condition for Converter 1

ister Check

//UVP Kegister Cneck p\_sequencer.i2c\_intf.12C\_READ (SLAVE\_ADDR1, REG\_OVP, i2c\_rdata); \$display("OVP\_STATUS = %h", i2c\_rdata); iffi2c\_rdata == expected\_data) //Checking the OVP register status `uvm\_info(get\_full\_name(), "OVP interrupt generated", UVM\_LOW) else

`uvm error("MAIN CHIP", "OVP interrupt generation failed");

#t\_wait\_time\_for\_flag\_release; //Wait time before releasing the flag

uvm\_hdl\_force("top.Main.I\_CONV\_1.OVP", 1'b0); //Releasing OVP condition for Converter 1

Once the OVP condition is triggered for Converter 1, all the converters shut down during which we check the status registers and display pass/fail status as shown above. After this, we re-enable the converters to see if they would power-up, followed by power down of all the converters.

//rower op p\_sequencer.i2c\_intf:I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE1); //Enabling Converter 1 (Converters 2 & 3 are auto-enabled) #\_converter\_1\_enable; //Converters 1-3 enable wait time p\_sequencer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE2); //Enabling Converters 4 & 5

#### //Power Down #t wait time

2.

p\_sequencer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE1); //Disabling Converters 4 & 5 #t\_converter 1\_enable;

ncer.i2c\_intf.I2C\_WRITE (SLAVE\_ADDR, REG1, VALUE0); //Disabling Converters 1-3

#### REFERENCES

- Kiyeong Kim, Hwan-woo Shim, Chulsoon Hwang, "Analysis and Solution for RF Interference Caused by PMIC Noise in Mobile Platforms", IEEE Transactions on Electromagnetic Compatibility, June 2019 1.

- Abdullah Abdulslam, Patrick P. Mercier, "A Symmetric Modified Multilevel Ladder PMIC for Battery-Connected Applications", IEEE Journal of Solid-State Circuits, December 2019

- Chunlei Shi, Brett Walker, Eric Zeisel, Brian Hu, Gene McAllister, "A Highly Integrated Power Management IC for Advanced Mobile Applications", IEEE Custom Integrated Circuits Conference, 3. September 2006

- Nicola Dall'Ora, Sara Vinco, Franco Fummi, "Functionality and Fault Modeling of a DC Motor with Verilog-AMS", IEEE 18th International Conference on Industrial Informatics, July 2020 4

- Constantina Tsechelidou, Nikolaos Georgoulopoulos, Alkiviadis Hatzopoulos, "Design of a 5. SystemVerilog-Based Sigma-Delta ADC Real Number Model", 22nd Euromicro Conference on Digital System Design, August 2019

- 6. Vijay Kumar, Shrikant Pattar, Yaswanth Chebrolu and Vinavak Hegde, "Harnessing SV-RNM Based lling and Simulation Methodology for Verifying a Complex PMIC designed for SSD Applications", **DVCON INDIA 2022**

- 7. Nikolaos Georgoulopoulos, Alkiviadis Hatzopoulos, "Real number modeling of a flash ADC using SystemVerilog", Panhellenic Conference on Electronics and Telecommunications, November 2017

- Nikolaos Georgoulopoulos, Alkiviadis Hatzopoulos, "Efficiency evaluation of a SystemVerilog-based real 8. number model", 7th International Conference on Modern Circuits and Systems Technologies, May 2018

- Nikolaos Georgoulopoulos, Athanasios Mekras, Alkiviadis Hatzopoulos, "Design of a SystemVerilog Based VCO Real Number Model", 8th International Conference on Modern Circuits and Systems 9. Technologies, May 2019

### Add acknowledgements, organization involved, logo's contact infomation here

- Manish Parmar, Manish Goel, Balajee Sowrirajan, Deepa Devendran, Shyam Prasad Venkata Voleti, Divij Kumar and Vinayak Hegde of 1. Samsung Semiconductor India Research

- 2. YuBeom Jeon of Samsung Electronics

CONCLUSIONS