SAN JOSE, CA, USA FEBRUARY 24-27, 2025

Refinable Macros and Terminal Boundaries in UPF 4.0: Empowering Soft IPs of the Future

Non-Intrusive Refinements for Seamless Soft IP (SIP) Integration

Presenter: Amit Srivastava Synopsys Inc

## Agenda: Solving the SIP Integration Puzzle

### The Problem

- SIPs vs. SoC Constraints

- UPF 3.1

- Progress & Gaps

- UPF 4.0

- Refinable Macros to the Rescue

- Case Study

- Optimizing Without Breaking Trust

- Future-Proofing SoC Design

### The SIP Integration Challenge

### SoC Complexity

• 50+ SIPs, each with unique power rules

### The Dilemma

- Modify SIPs -> risk introducing bugs

- Revalidate SIPs -> wastes time

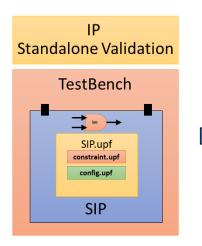

### • UPF 3.1's Fix

- Good for implementation

- Too rigid for verification

Intrusive Updates

Invalidates the

Standalone Validation

create\_power\_domain

set\_retention

## UPF 3.1: Progress and Gaps

### Successive Refinement

- Layered power intent

- Constraint -> Configuration -> Implementation

### UPF 3.1: Progress and Gaps

### Successive Refinement

- Layered power intent

- Constraint -> Configuration -> Implementation

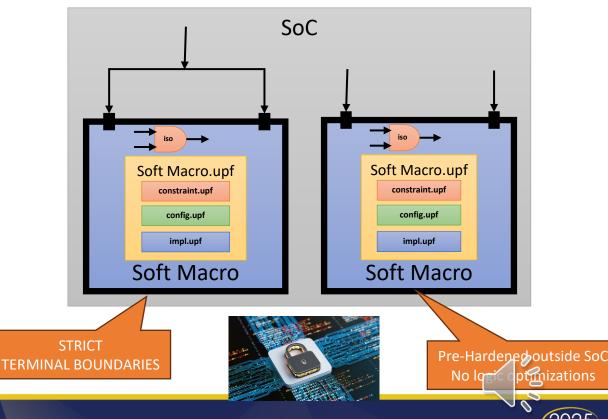

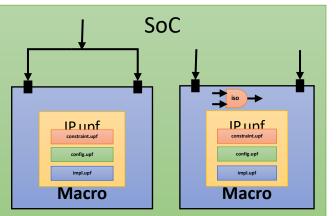

#### Soft Macros

- IPs as locked boxes (Terminal Boundaries)

- Bottom-Up Implementation Focus

### The Gap

No safe way to adjust boxes post integration

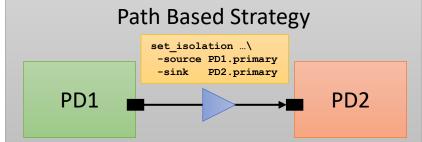

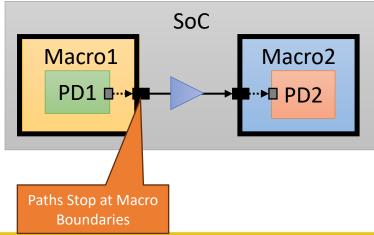

# Path Based Strategy Mismatch: Simulation vs. Synthesis

#### Path Based Strategies:

- Insert cells based on connectivity

- Automate power-management cell insertion

- Pose problems for IPs

#### • Scenario:

- IP with 2 Supplies

- SoC Shorts One Instance

- Problem: Simulation Omits Isolation, but Synthesis Retains Isolation

- Terminal Boundaries mitigate these mismatches in UPF 3.1

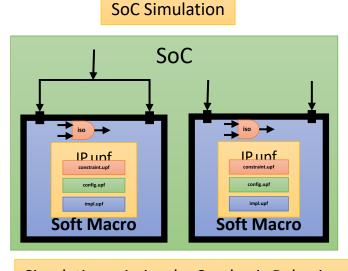

SoC Simulation

Simulation will not see Isolation Cell In the instance where supply is shorted

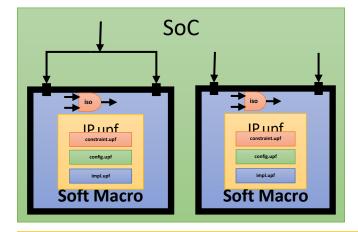

SoC Implementation

Macro synthesized as standalone block

SoC reuses netlist of Macro regardless

Both Instance of Macro have isolation cells

### Terminal Boundaries: Guarding the IP Fortress

- Protects IP from External Overrides

- Path-Based strategies respect the boundary

- Boundary constraints are user defined and Tool-Validated

- **Essential** for Consistent Interpretation, but can be limiting

### Soft Macros: Bottom-Up Implementation

Create Terminal Boundaries for implemented blocks

#### Pros

- Preserve IP integrity

- Ensure consistent Simulation vs Synthesis semantics

#### Cons

- Rigid Terminal boundaries

- No refinements

- Not suited for preverified SIPs

- Intrusive updates break standalone validation

Simulation mimics the Synthesis Behavior Because of Soft Macro marking

#### SoC Implementation

Macro synthesized as standalone block SoC reuses netlist of Macro regardless Both Instance of Macro have isolation cells

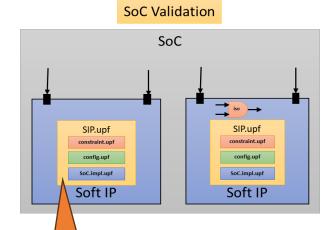

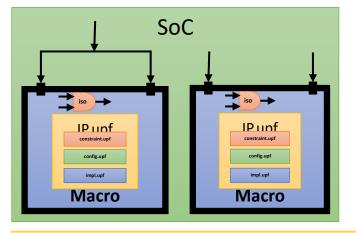

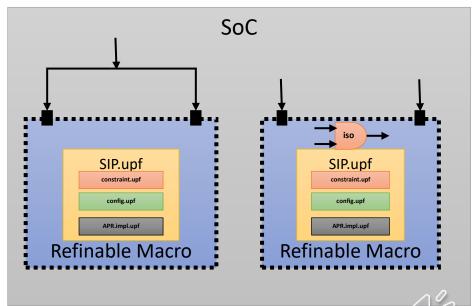

### Refinable Macros in UPF 4.0

- Refinable Terminal Boundaries

- Tool-Enforced Safety

- Non-Intrusive Power Intent Updates

- Preserved Verification

- Original IP UPF remains untouched

- Enables System-Level

Optimization during

Implementation

- Ideal for Bottom-Up Verification

### Coding Refinable Macros

- Simple UPF Attribute

- Mark IP internally or externally

- Maintains IP Verification

- Override to Soft Macro if Needed

```

# Mark directly in IP UPF:

set_design_attributes -models . -is_refinable_macro true

# Or mark externally:

set_design_attributes -models IP_Design -attribute {UPF_is_refinable_macro TRUE}

```

Implementation UPF: The Safety Filter

- Safe Refinements via Allowed Commands and options

- UPF 4.0 defines allowed commands and options

- -implementation Enforces

Correct-by-Construct UPF

- EDA Tools Enforce Compliance

- No Alteration of Original IP UPF

- Preserves Verification Integrity

```

# SoC UPF

load_upf ip_impl.upf \

-scope myIP \

-implementation

# ip_impl.upf

set_isolation PGD_to_AON \

-domain PGD \

-location parent

-update

```

### Practical Example: Refinable Macros in Action

#### ip.upf

```

set design attributes -models . \

-is refinable macro TRUE

create supply set ss IP AON

create supply set ss IP PGD

create power domain AON -elements {.}

create power domain PGD -elements

{ip1 pgd wrapper}

## Isolates all outputs where different

## supplies power source and sink

set isolation PGD to AON -domain PGD \

-isolation supply set ss IP AON \

-applies to outputs -source ss IP PGD

-diff supply only TRUE

-isolation signal pwr manager/iso en b \

-isolation sense low

```

#### ip\_impl.upf

```

set_isolation PGD_to_AON \

-domain PGD \

-location parent

-update

```

Implementation updates only

AON and PGD supplies are shorted for one instance of the IP

### ParlP.upf

```

create_power_domain par_AON -elements {.}

create_supply_set ss_SOC_AON

create_supply_set ss_SOC_PGD

load_upf ip.upf -scope ip1

load_upf ip_impl.upf -scope ip1 -implementation

associate_supply_set {ss_SOC_AON ip1/ss_IP_AON}

associate_supply_set {ss_SOC_AON ip1/ss_IP_PGD}

load_upf ip.upf -scope ip2

load_upf ip_impl.upf -scope ip2 -implementation

associate_supply_set {ss_SOC_AON ip2/ss_IP_AON}

associate_supply_set {ss_SOC_AON ip2/ss_IP_AON}

associate_supply_set {ss_SOC_PGD ip2/ss_IP_PGD}

```

ip1

SoC (ParIP.upf)

### Guidelines & Best Practices

- Always mark terminal boundaries

- ✓ Use Refinable Macro Marking for SIPs

- Keep Original IP UPF Intact; add SoC adjustments in Implementation UPF

**Leverage –implementation for Correct-by-Construct**

# Conclusion: Empowering Soft IPs of the Future

- Terminal Boundaries -> Unified Tool Behavior

- UPF 4.0 -> Bridges SIP Verification Gaps

- Refinable Macros = Flexibility + Safety + Performance

- Implementation UPF -> Correct-by-Construct

- Preserves Verification & Saves Time

## Acknowledgements

- Co authors

- John Decker, Cadence

- Lakshmanan Balasubramanian, TI

- IEEE 1801-UPF WG members

- Contact

- Amit.Srivastava@synopsys.com

SAN JOSE, CA, USA FEBRUARY 24-27, 2025

Thank you