# A Comprehensive High Speed Link Verification Test Bench Harnessing Scripting to Achieve Faster Functional Coverage Closure.

Piyush Tankwal (p.tankwal@samsung.com), Arnab Ghosh (arnab.ghosh@samsung.com), Piyush Agnihotri (piyush.a@smasung.com), Mukesh Gandhi (mukesh.g@samsung.com), Parag S Lonkar (parag.lonkar@samsung.com) Samsung Semiconductor India Research (SSIR), Bengaluru, India.

*Abstract*- This paper introduces a verification framework tailored to the challenges of High-Speed Link Design Verification (DV), with a focus on improving efficiency and maintaining high-quality results. In the context of complex High Speed Link designs such as UniPro, where an extensive number of functional coverage bins must be addressed within strict time constraints, this work offers a comprehensive approach. The proposed framework incorporates a "Smart Coverage Closure Technique" that leverages test ranking and Perl script integration. This technique not only expedites the coverage closure process but also enhances its effectiveness. The script facilitates the creation of a directed test suite by extracting data on un-hit coverage bins, which precisely targets and covers specific bins with a single test run, optimizing resource utilization. Also, to find bug at the initial stage of verification some scenarios are proposed which creates simulation condition close to the real world by incorporating skew, lane mapping. Different kind of techniques, checkers and automation are also discussed to ensure robust verification framework.

## I. PROPOSED WORK AND APPLICATION

The proposed work aims to address challenges in the High-Speed Link DV (Design Verification) process by introducing a general verification framework. Our framework is designed to reduce the time and effort required for verification activities while ensuring high-quality results. Several key strategies are discussed:

The work proposes scenarios that enable the detection of bugs at an early stage to improve the efficiency of the verification process. These scenarios aim to create simulation conditions that closely resemble to real-world conditions. They incorporate elements like skew injection in between the lanes and lane mapping for cross lane connection between lanes for the IP having more than one lane, which can help uncover potential issues in the design early on.

The link designs are usually complex, in term of the features and cross scenarios they support hence the functional coverage bins turn out to be humongous. So, to meet the coverage goals for all these bins within time constraints can be challenging and to address this issue, a smart coverage closure technique is proposed. This technique involves test ranking and Perl script for coverage holes. The script is responsible for extracting statistics on un-hit bins, and then it creates a directed test suite to target those specific bins with a single test run. This approach optimizes the coverage closure process.

In summary, the proposed general verification framework aims to enhance the High-Speed Link DV process by adding robust checkers, improving functional coverage closure, and facilitating early bug detection. These strategies are geared towards streamlining the verification process while maintaining high-quality results. Though we have taken reference of UniPro IP in multiple places, these strategies are not limited to specific Link IP and can be extrapolated widely to any other High Speed Link IP's.

## A. High Speed Link-PHY Test Bench Architecture

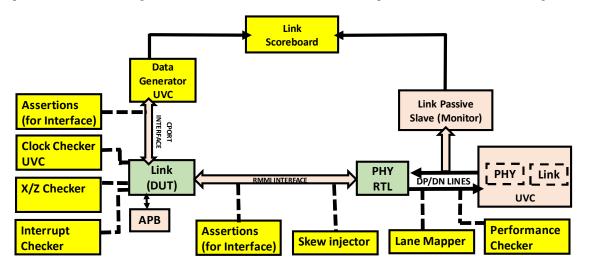

Our robust testbench encompasses a wide range of verification aspects to ensure the quality, functionality, and performance of the design under test. Here's an overview of the components we've mentioned in Fig1.

Figure 1. Configurable Robust Test bench (Reference: UniPro2.0 Link-PHY interface).

1) Performance Analysis: Our testbench goes beyond functional verification by including performance checks. Specifically, we're evaluating two key performance metrics:

*Throughput:* This metric measures the rate at which data is processed or transmitted through the design. It helps ensure that the system can handle data at the expected rate. Few factors like Link protocol overhead at different message, frame size and PHY protocol overhead in different power mode and gear can reduce the actual throughput of the DUT than the theoretical maximum.

*Latency:* Latency measures the delay or time taken for data to traverse the design. Low latency is often crucial in real-time systems, so verifying this aspect is important.

- 2) Save-Restore: In High-Speed Link, initialization itself can take more than half of the simulation time that delays the verification process. So, to avoid that we can save the repetitive process of Link Up (Link Enable and Training) and re-store it when required. Though it is not a novelty but for the completeness and general awareness of DV engineers we would like to highlight the significance of this step. We have achieved closed to 50-60 % efficiency improvement using it.

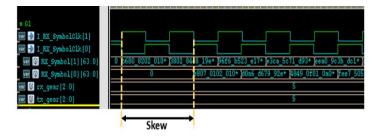

- 3) Skew Injector: Inter-lane skew is a common phenomenon at the serial lanes and standards are mentioned in the PHY specification. This skew is passed to the upper layer and it is responsibility of the Link layer to merge the data correctly. So, skew injection at Link-PHY interface is required considering all possible scenario and adequate randomization for proper verification sign-off, which is achieved by configuring the Clock UVC appropriately.

Figure 2. Skew insertion between Lane0 and Lane1 at RMMI for HS-G5 in Rx symbol (Reference: UniPro2.0 Link-PHY interface).

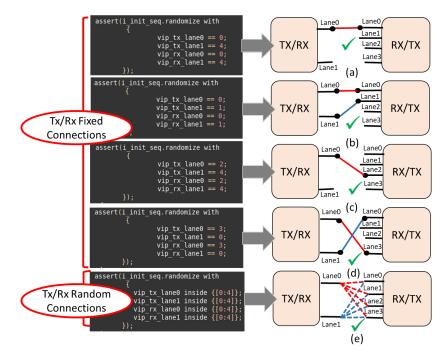

4) Lane Mapper: As per MIPI Standards, the Lane Mapping functionality is used to discover the physical lanes on the high-speed link. Most of the times, it is seen that this feature is not tested rigorously as compared to other features and mostly testing is limited to fixed connections.

- Figure 4. Random lane connection example for UniPro 2.0 DUT (2 Lane) and Peer Device (4 Lane ) (a) Single-Lane Straight Connection (b) Dual-Lane Straight Connection (c) Single-Lane Cross Connection (d) Dual-Lane Cross Connection (e) Random Lanes Connection

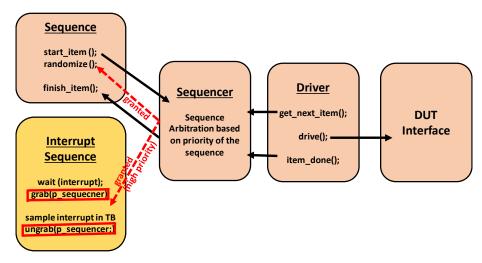

- 5) *Interrupt Checker:* The interrupt checker component is designed to verify the functionality of interrupt handling within the design. It validates if interrupts are triggered, processed and cleared correctly and timely, which is especially important in systems where timely responses to events are critical.

Figure 3. Interrupts handler sequence in UVM based test bench.

6) Clock UVC: Clock UVC (Universal Verification Component) is responsible for checking the behavior of clock signals within the design. It ensures that clocks are generated, distributed, and gated correctly, which is crucial for synchronization and proper operation of the design. Automation script is used to dump the clock UVC which generates appropriate clock for the DUT and also check the output clock with respect to different parameter like frequency, phase, division factor, jitter, skew etc.

7) Assertions for Protocol Compliance: Assertions are used to verify that the design adheres to specific protocols or standards. In our case, these assertions are employed to ensure that the design follows the specified communication protocols correctly, which is essential for interoperability and data integrity.

Overall, our testbench seems well-rounded, addressing both functional and performance aspects of verification, which is essential for thoroughly testing a design's quality and capability. Incorporating performance analysis into our testbench is valuable because it ensures that our design not only functions correctly but also meets performance requirements.

It demonstrates a comprehensive approach to verification that goes beyond mere functionality to evaluate realworld performance, making it robust and suitable for rigorous testing of your design.

# B. Smart Coverage Closure using Scripting

The challenges like the constrained random verification and directed test case verification are effective methodologies but can be time-consuming and demanding in terms of DV engineer effort. These standard methodologies involve creating and running numerous tests to achieve comprehensive coverage, which may not always be feasible within project timelines. As a solutions coverage hole script is introduced which ensures efficient verification processes in a dynamic environment. Let us go a bit in details:

- 1) Coverage Hole Perl Script Agent: To address the challenge of coverage holes and streamline the verification process, the coverage hole script agent plays a crucial role. It helps by:

- a) Obtaining the latest coverage database.

- b) Extracting information about un-hit coverage bins.

- c) Creating a directed test suite to target the remaining uncovered bins with a single test run.

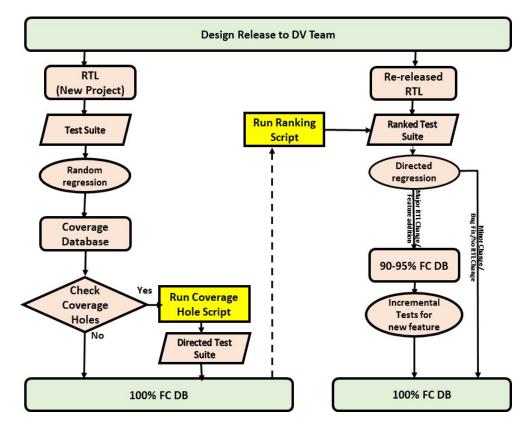

Figure 5. Test bench integrated with Coverage Hole Perl and Ranking script for coverage.

*Benefits:* We have well-structured process for achieving and maintaining coverage in our RTL verification as shown in Fig 5. By running random regression and then using our coverage hole script to generate directed test suites to target un-hit bins, we can efficiently approach 100% coverage. Also, at times there are few legacy cover groups which may not be needed and impossible to hit so to avoid overworking of script for the invalid bins, there is provision that the user can pass the refine file to script as an input and the script will ignore those bins. Additionally, the ranking script helps prioritize tests based on their contribution to overall coverage and generate a ranked test suite. For minor RTL changes, the ranked test suite can help in achieving nearly 100% coverage without much effort. However, for major changes user may need to write new test to cover the newly added features which is common practice to ensure comprehensive verification.

*Limitation*: The script has a limitation that it will generate the directed test cases targeting specific un-hit bins only. So, a word of caution here that it should not be taken up as a first step in closing the functional coverage. To find the hidden bugs and hit corner scenarios, random regression is essential and should not be bypassed. So, in other word, though this script can be run for most of the coverage but it is not recommended as randomness of DV test bench will be lost. This script is more suitable where a big covergroup or cross coverage is targeted by randomizing or constraining one single testcase with multiple inputs.

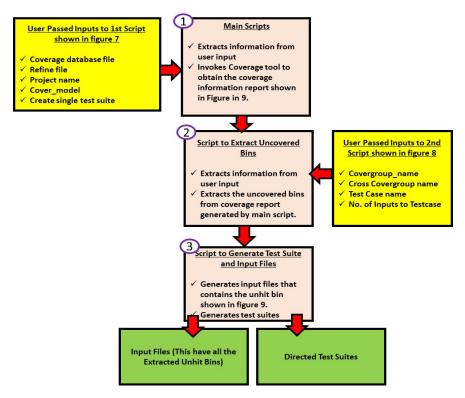

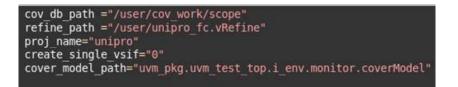

*Coverage Hole Script Working Flow:* This script is designed to focus on stimulus coverage, making it easily adaptable to different complex IP's. We have a sequential script process consisting three scripts as shown Fig. 6. Initially, the main script is responsible for extracting essential information from the user's passed input data like project name, coverage model, refine file, coverage database and these user's passed input will be changed project to project. This refines file includes identifying invalid cases for dependent random variables. Additionally, this main script triggers the coverage tool to generate a coverage report, as illustrated in Fig. 9. This coverage report has the details about both hit and un-hit bins. Following this, the second script examines the user's provided inputs, which contain the information about the for which cover group user want to extract un-hit bin information and this script determines which generic random test cases these extracted unhit bins should be passed to. These generic random test cases need to be written according to the targeted cover groups. As evident, described script is very generic and can be used for any stimulus coverage closure for any kind of IP or Sub-system. The required input files and testcases will only change based on the use case scenario.

Figure 6. Working Flow of Coverage Hole Script.

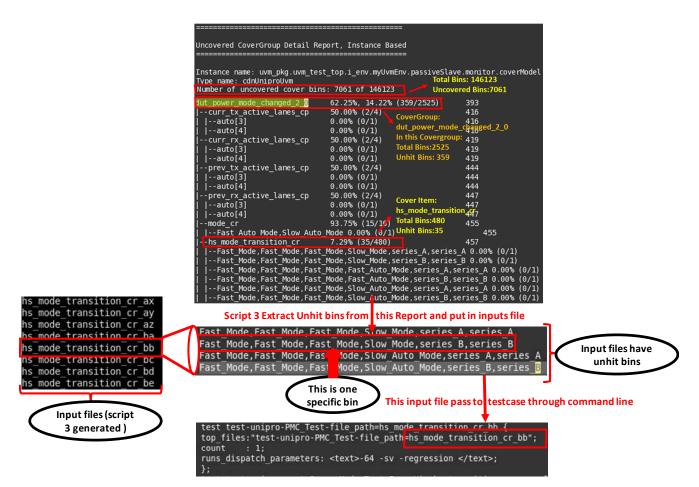

Finally, the third script takes the extracted bins for the user-specified cover groups and leverages them to create input files as shown in Fig 9. Also, this script generates the test suites associated with these input files. The purpose of these generated test suites is to specifically target the un-hit bins in script generated inputs files.

Figure 7. 1st Input File to Script for Main Script.

```

#COVERGR00UP_NAME, CROSS_BIN_NAME, TEST_NAME, No_of_inputs_to_the_testfile (0 for all)

```

dut\_power\_mode\_changed\_2\_0, hs\_mode\_transition\_cr, Power\_Mode\_Test\_From\_Vip\_hs\_transition\_cross, 1

dut\_power\_mode\_changed\_2\_0, ls\_mode\_transition\_cr, Power\_Mode\_Test\_From\_Vip\_ls\_transition\_cross, 1

dut\_power\_mode\_changed\_2\_0, lanes\_transition\_cr, Power\_Mode\_Test\_From\_Vip\_lanes\_transition\_cross, 1

dut\_power\_mode\_changed\_2\_0, gear\_transition\_cr, Power\_Mode\_Test\_From\_Vip\_gear\_transition\_cross, 1

Figure 8. Input File to the 2<sup>nd</sup> Script.

Figure 9. Snaps of Uncovered Covergroup Detail Report, Script generated input file and Test Suite.

Our case study on complex High-Speed Link UniPro IP have around total 146123 bins as shown in Fig 9. The coverage hole script will take approximately 40 to 60 seconds to extract and create directed test suites for these many bins and it can be scaled up easily for more complex IP's or sub-system. Perl is a high-level, general-purpose language which is easy to learn and good choice for short scripting and text processing. Based on the use-case and scripting requirement this looks perfect fit for our need.

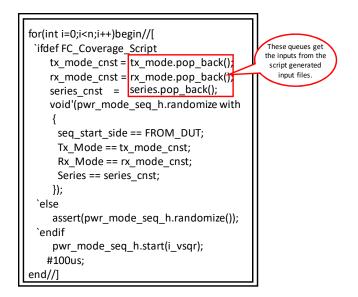

Our approach is for test reusability. We are using "define" mechanism to determine variable values in our test cases. When user used "FC\_Coverage\_Script" define then test variables get the values from the script generated input files and this allow tests to target specific combination of un-hit bins in single run as shown Fig 9. Otherwise, variable values are decided randomly during random regression. This flexibility can save time and effort in testcase development as same testcase, created for random verification, is reused.

Figure 10. Example code of Power Mode Change (PMC) with Script generated Unhit Bins

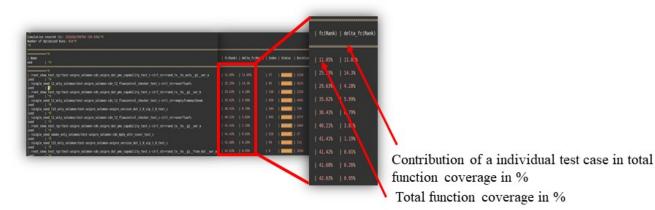

2) Coverage Ranking Script: Another important script in efficient verification is the coverage ranking script.

Figure 11. Ranking Script output log file

This script:

- a) Ranks regression runs based on their contribution to coverage as shown in Fig 11.

- b) Creates a test suite that focuses on the specifically on all bins with single run.

c) Proves particularly valuable in scenarios where multiple RTL (Register-Transfer Level) releases occur, and the verification team needs to quickly close coverage gaps as part of iterative development.

In summary, our approach leverages automated scripts and ranking methodologies to expedite the verification process, especially in scenarios with time constraints and multiple RTL releases. These proposed methodologies aim to reduce the burden on verification engineers, streamline the closure of coverage holes, and improve the overall efficiency of the verification process.

## II. RESULTS AND CONCLUSIONS

The proposed methodologies and setup help DV engineers in finding the bugs at early stage of the product development. Also, user will be able to close the DV in quick succession with the help of proposed coverage scripts as results shown in Table I and Table II. User will not able to achieve 100% coverage in single run in case of major changes in RTL and hence TB changes, because same seed will not create the same test vector. As coverage hole script stores the test vectors, it reduces the coverage slip as shown in Table II and still able to achieve 90-95% coverage in single run. In addition, the same DV setup can be and scaled up for sub-system verification and reused for other high speed link verification with minimal effort.

Table I. Comparison of Number of Test Runs with and without Script (Reference: UniPro2.0 DV)

| Approximate Number of 1est Kuns to Achieve 100 % FC Coverage |                   |                         |                              |  |

|--------------------------------------------------------------|-------------------|-------------------------|------------------------------|--|

| Method                                                       | Random Regression | After Adding PMC Script | After Running Ranking Script |  |

| Total Test Run                                               | 20000-25000       | 8000-10000              | 3000-3500                    |  |

## Table II. Comparison of Coverage Replay with Beta Test Suite (Reference: UniPro2.0 DV) Approximate Coverage Replay with Beta Test Suite regression (New RTL release)

| Method of generation | Ranking Script (only) | Ranking + Coverage Hole Script |  |  |

|----------------------|-----------------------|--------------------------------|--|--|

| FC (%)               | 80-87%                | 90-95%                         |  |  |

### REFERENCES

- [1] "MIPI Alliance DRAFT Specification for Unified Protocol, version 2.0 r10", mipi.org.

- https://members.mipi.org/wg/UniPro/document/folder/14599 (accessed Jan 17, 2022). [2] "MIPI Alliance DRAFT Specification for M-PHY v5.0 r06," mipi.org. https://members.mipi.org/wg/M-PHY/document/folder/14115

- [2] MIPT Annance DKAPT Specification for Mi-PHT V3.0 roo, https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.https://members.http