#### **UNITED STATES**

SAN JOSE, CA, USA MARCH 4-7, 2024

#### Metric Driven Microcode Verification: Navigating Microcode Coverage Complexities

Seungyeon Yu, Damin Son, Tony Gladvin George, Kihyun Park, Dongkun An, Wooseong Cheong, ByungChul Yoo

Samsung Electronics

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

#### Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

#### Motivation

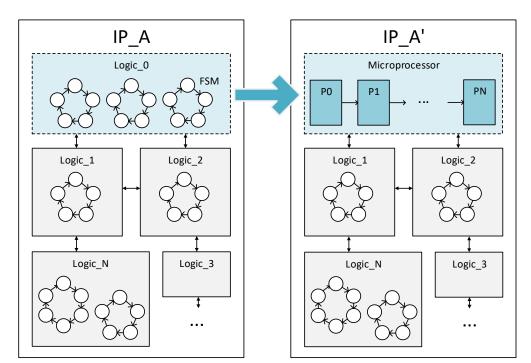

- Microprocessor applications to an in-house project

- Changes in architecture

- Expansion of verification scope

- FSM Logic  $\rightarrow$  FSM Logic + Microcode

#### Motivation

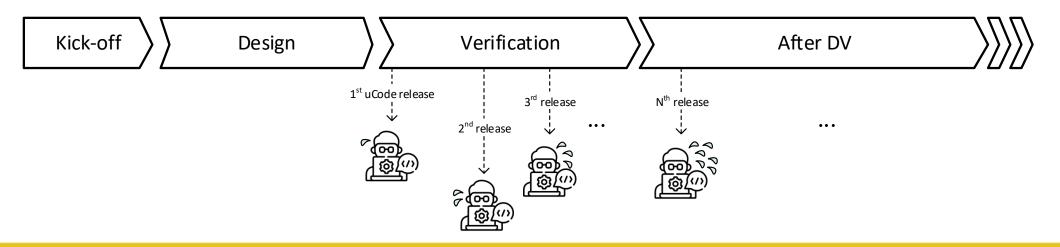

- The absence of indicators for the completion of microcode verification

- Unpredictable whether all microcode is covered.

- Possibility of bugs in microcode that has not been covered yet.

- The problem repeats whenever microcode is changed.

- So We propose a methodology to analyze the coverage of microcode.

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

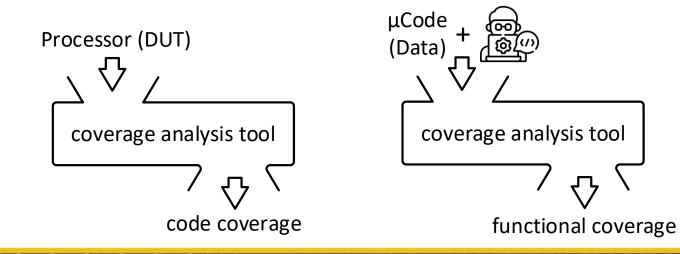

# How to analysis the coverage of microcode?

- The coverage analysis tool only supports coverage analysis results for microprocessors(DUT), not microcode(Data).

- For coverage analysis of microcode, verification engineers must write functional coverage manually.

#### An Increase in workload

- Whenever microcode is updated, verification engineers are required to manually modify the functional coverage.

- This approach increases the workload of verification, which affects the project schedule.

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

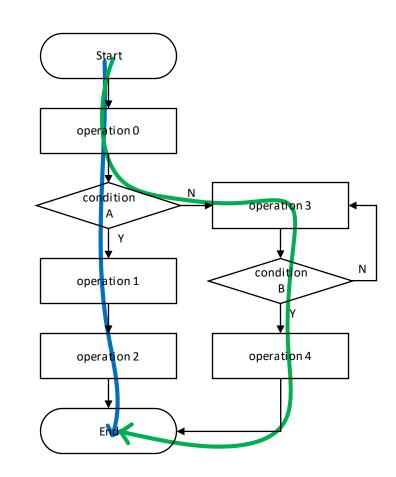

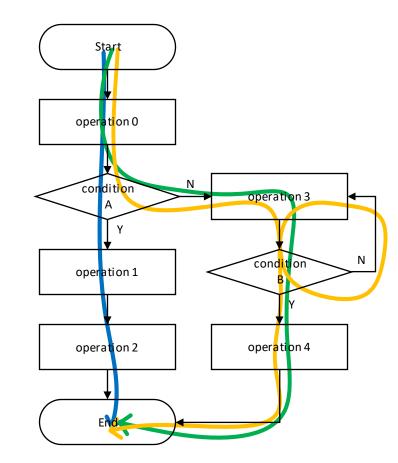

# FC Checker: Operating concept

- Assumption

- What if the criterion for achieving coverage 100% is to perform all operations?

- The operation flow implemented in microcode

- blue path

- op0  $\rightarrow$  (condition\_A == T)  $\rightarrow$  op1  $\rightarrow$  op2

- green path

- op0  $\rightarrow$  (condition\_A == F)  $\rightarrow$  op3  $\rightarrow$  (condition\_B == T)  $\rightarrow$  op4

# FC Checker: Operating concept

- If only the blue path and the green path are executed, it satisfies 100%.

- However, there is an additional path that needs to be covered.

- yellow path

- op0  $\rightarrow$  (condition\_A == F)  $\rightarrow$  op3  $\rightarrow$  (condition\_B == T)  $\rightarrow$  op4

- Therefore, the important part is where the flow changes according to the condition.

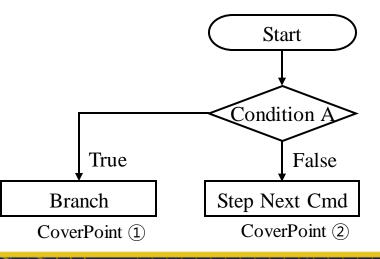

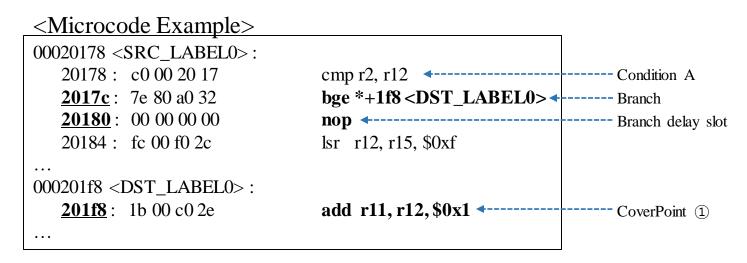

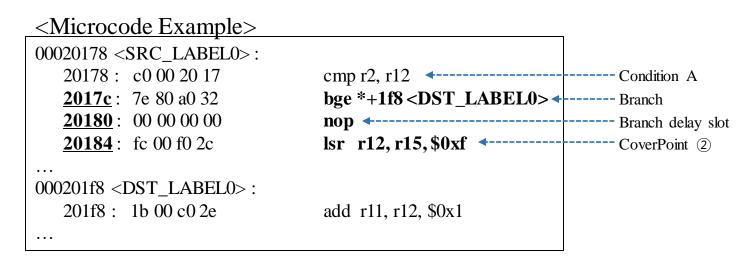

# FC Checker: Coverpoints of the Checker

- Implement a checker by monitoring the path of the microcode address (PC).

- Check these two cases to generate functional coverage for microcode.

- Cover Point 1 : Condition A == TRUE  $\rightarrow$  Branch

- Cover Point 2 : Condition A == FALSE  $\rightarrow$  Step Next Command

# FC Checker: Coverpoints of the Checker

- Check these two cases to generate functional coverage for microcode.

- Cover Point 1 : Condition A == TRUE  $\rightarrow$  Branch

- Cover Point 2 : Condition A == FALSE → Step Next Command

# FC Checker: Coverpoints of the Checker

- Check these two cases to generate functional coverage for microcode.

- Cover Point 1 : Condition A == TRUE  $\rightarrow$  Branch

- Cover Point 2 : Condition A == FALSE  $\rightarrow$  Step Next Command

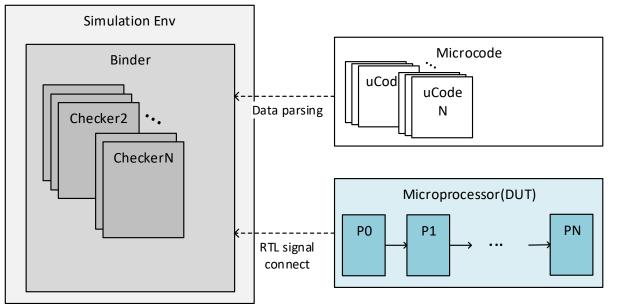

# FC Binder : A file that binds checkers

• Binder file contains SV bind commands which bind multiple checker instances into the simulation environment.

- uCode

- uCode address (PC) with br instruction

- uCode address (PC) after br instruction

- Microcode operation label

- uProcessor

- RTL signal drive

## Implementation of FC checker

module uCodeFcChecker #(parameter SRC\_PC='h0, parameter DST\_PC='h0) ( input i\_clk i rstn input i\_inst\_mem\_csn , input i\_inst\_mem\_wen , input input [15:0] i\_inst\_mem\_a ); wire inst\_mem\_rd = !i\_inst\_mem\_csn & i\_inst\_mem\_wen; property ucode\_step\_next(src\_pc); inst\_mem\_rd & (i\_inst\_mem\_a == src\_pc ) |-> disable iff (!i\_rstn) ##1 inst\_mem\_rd & (i\_inst\_mem\_a == src\_pc+1) |-> ##1 inst\_mem\_rd & (i\_inst\_mem\_a == src\_pc+2); endproperty property ucode\_branch(src\_pc, dst\_pc); disable iff (!i rstn) inst\_mem\_rd & (i\_inst\_mem\_a == src\_pc ) |-> ##1 inst\_mem\_rd & (i\_inst\_mem\_a == src\_pc+1) |-> ##1 inst\_mem\_rd & (i\_inst\_mem\_a == dst\_pc ); endproperty \_COV\_UCODE\_STEP\_NEXT : cover property ( ucode\_step next(SRC PC) ); : cover property ( ucode branch(SRC PC, DST PC) ); COV UCODE BRANCH endmodule

#### • Coverpoints

- ucode\_step\_next

- Case not branched due to unsatisfied condition

- ucode\_branch

- Case branched due to satisfied condition

- Monitoring the memory signals where uCode is loaded.

# Implementation of FC Binder

```

bind `XX TOP UcodeBinder z uCode Checker();

module UcodeBinder();

uCodeFcChecker #(.SRC_PC('h807f), .DST_PC('h808e))

u_CHKR0_SRC_LABEL0_DST_LABEL0 (

.i_clk

( i_clk

),

.i rstn

( i_rstn

.i_inst_mem_csn

o_inst_mem_csn),

.i inst mem wen

o_inst_mem_wen),

.i_inst_mem_a

( o_inst_mem_a

);

uCodeFcChecker #(.SRC_PC('h8082), .DST_PC('h8087))

u_CHKR1_SRC_LABEL1_DST_LABEL1 (

.i_clk

( i_clk

),

.i rstn

( i rstn

.i inst mem csn

o_inst_mem_csn),

( o_inst mem_wen),

.i_inst_mem_wen

( o_inst_mem_a

.i_inst_mem_a

);

endmodule

```

- The number of checker instances is generated as many as the number of branch instructions in the microcode.

- The binder provides the address information required for the FC checker instances as a parameter.

- The binder connects the checker instances and the RTL signal.

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

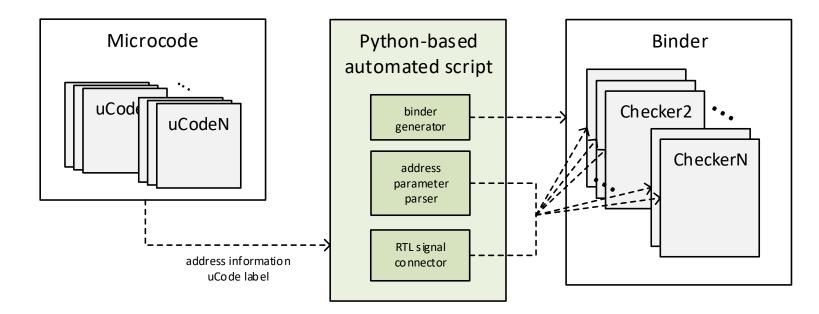

## Automated Checker File Generation

- The high flexibility of microcode leads to frequent modifications, making it difficult for verification engineers to respond every time.

- The driving of inputs and parsing of uCode information particularly increases the workload of verification engineers.

- Therefore, we propose a method of automatically creating an assertion coverage by introducing a Python-based automated script.

# Automated Checker File Generation

• When an uCode file is inputted, the python script generates a checker file and a binder file containing uCode information and RTL connections.

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

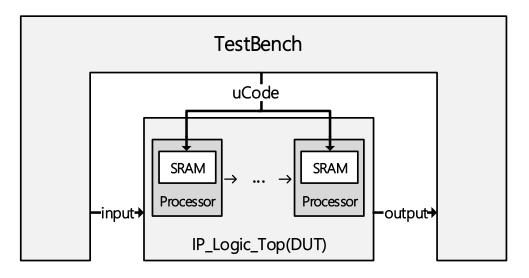

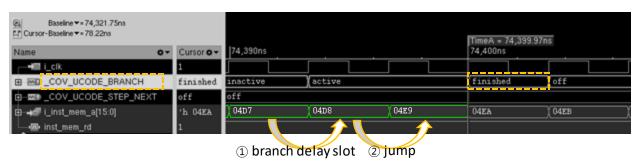

# **Experimental Condition**

- Custom microprocessors in the IP

- Processor has a branch delay slot.

- It is based on RISC-V.

- DUT takes h/w and uCode into consideration together.

- The verification test suite contains many different combinations of external stimuli.

### **Experimental Results**

#### • Branch

• Execute next instruction

| Baseline ▼= 74,321.75ns<br>FT Cursor-Baseline ▼= -115.5ns |            |              |             |              | TimeA = 74,206.25n | a.       |

|-----------------------------------------------------------|------------|--------------|-------------|--------------|--------------------|----------|

| Name o-                                                   | Cursor O - |              | 74,200ns    |              |                    | 74,210ns |

| <b>+</b> ≡ i_clk                                          | 1          |              |             |              |                    |          |

| - D- D _COV_UCODE_BRANCH                                  | inactive   | inactive     | active      |              | inactive           |          |

| COV_UCODE_STEP_NEXT                                       | finished   | inactive     | active      |              |                    | off      |

| ⊕- <b>→</b> ∰ i_inst_mem_a[15:0]                          | 'h 04Dà    | 04D7         | 04D8        | 04D9         | (04DA              | 04DB     |

| - @ inst_mem_rd                                           | 1          | 1) branch de | elay slot 2 | execute next | 1                  |          |

#### **Experimental Results**

- The code coverage of the processor does not indicate whether the IP operation flow has been performed.

- Since it is coverage for the DUT that operates the ucode, it cannot be an indicator for uCode verification.

- Through the ucode checker, we can confirm that **98%** of FC has been achieved.

- The solution is reusable for all IPs that use the processor and has been applied to several projects in practice.

| Type Name    | Overall Average Grade | Overall Covered |

|--------------|-----------------------|-----------------|

| Ucode0Binder | 94.44%                | 34/36 (94.44%)  |

| Ucode1Binder | ✓ 100%                | 58 / 58 (100%)  |

| Ucode2Binder | ✓ 100%                | 26 / 26 (100%)  |

| Ucode3Binder | 97.56%                | 80/82 (97.56%)  |

| Project |           | erbin<br>Total Cover bin) | Code Coverage (%) | Functional Coverage<br>(%) |

|---------|-----------|---------------------------|-------------------|----------------------------|

|         | Processor | Microcode                 | Processor         | Microcode                  |

| IP A    | 673/911   | 198/202                   | 73.8              | 98.0                       |

| IP B    | 852/1143  | 389/422                   | 74.5              | 92.2                       |

| IP C    | 849/1143  | 431/460                   | 74.3              | 93.7                       |

- Motivation

- Problem Statement

- Assertion-based Coverage Checker For Microcode

- Automated Checker File Generation

- Experimental Results

- Conclusion

#### Conclusion

- Universally applicable and easily reused

- Serve as a criterion for signing off on microcode verification

- Significantly reduce the time and effort required for microcode verification

- Improve the quality and reliability of microcode

#### Questions

• <u>ssyeon.yu@samsung.com</u>