# Addressing Advanced Mixed-Signal Verification Scenarios by Developing a UVM Framework for Analog Models

Simul Barua Ulkasemi Inc. 20045 Stevens Creek Blvd, Suite 2B Cupertino, CA 95014 simul@ulkasemi.com Shahriar Kabir Ulkasemi Inc. 20045 Stevens Creek Blvd, Suite 2B Cupertino, CA 95014 shahriar@ulkasemi.com Henry Chang

Designer's Guide Consulting,

Inc.

3043 Meridian Ave #35

San Jose, CA 95124

henry@designers-guide.com

Abstract- With the rise of AI, IoT, and automotive safety applications, the demand for reliable mixed-signal verification in Integrated Circuit (IC) design has become critical. Increasing design complexity, particularly at the interface of analog and digital components, often leads to verification gaps and costly respins. This paper introduces the Analog Mixed-Signal Verification (AMSV) utility framework, which enhances system-level testbenches by integrating analog behavioral models within a Universal Verification Methodology (UVM) environment. Leveraging SystemVerilog's object-oriented programming (OOP) capabilities, the AMSV framework enables precise monitoring and control of analog models, allowing for accurate simulation of real-world conditions, including temperature effects, parametric variations, and subsystem failures. Through detailed case studies, we demonstrate the framework's capacity to address verification needs in advanced applications, significantly improving accuracy and efficiency. Simulation results validate the framework's potential to enhance IC reliability, making it particularly relevant to emerging, high-stake domains.

#### I. INTRODUCTION

The complexity of Integrated Circuit (IC) verification has significantly increased, often outpacing the complexity of the design itself. This trend is particularly evident in modern applications such as Artificial Intelligence (AI), the Internet of Things (IoT), and automotive safety, all of which demand heightened reliability and seamless functionality across both analog and digital domains. Consequently, verification success rates have declined, leading to a rise in costly IC respins [1]. Two significant factors driving these respins are issues in the analog design and bugs in the mixed-signal interfaces, which are crucial components in modern designs. Our previous research [2] addressed these challenges by incorporating basic analog functional models into chip-level verification environments, demonstrating how these models can enhance system-level verification to catch bugs that would otherwise evade detection in traditional digital-focused testbenches.

Despite these advancements, conventional verification methodologies still lack the robustness needed to address more complex system requirements. As IC design complexity evolves, we must account for system performance, safety, and other more complex scenarios that a digital twin, which needs to include analog elements, must address. This could involve simulating the effects of temperature or parametric variations of block non-idealities onto the overall system for performance. For safety, this might mean modeling how analog blocks, subsystems, and systems fail in particular ways.

This is where analog models demonstrate their true value. Besides simulating at feasible speeds compared to transistor-level simulations, models can incorporate complex effects like environmental stress factors and parametric shifts in a straightforward manner. The potential of these analog models is vast, offering greater flexibility, enabling the modeling and simulation of complex real-world scenarios, and allowing broader system assessments, such as evaluating how AI algorithms perform when critical analog components degrade or fail.

However, to fully harness these enhanced analog models, the traditional system-level testbench widely developed in SystemVerilog and/or Universal Verification Methodology (UVM) must also evolve. They require improved capabilities for monitoring, controlling, and interacting with analog models, enabling verification under advanced, real-world conditions.

This paper introduces the Analog Mixed-Signal Verification (AMSV) utility framework, which leverages SystemVerilog object-oriented programming (OOP) constructs to enhance analog models and the system-level testbench. The AMSV utility framework goes beyond simply addressing respin issues; it enables precise modeling and simulation of real-world conditions such as temperature effects, parametric variations, failure conditions, analog impairments, and other intricate scenarios. Thus, it allows for a more comprehensive evaluation of system performance and safety.

## II. MOTIVATION AND PURPOSE OF THE AMSV UTILITY FRAMEWORK

Traditionally, simulating environmental effects required slow, transistor-level simulations, which provided accuracy but were impractical for system-level verification and offered no direct control over environmental impacts from testbenches. This limitation made it challenging to verify critical features, such as the system responses to temperature-induced frequency drift of a Phase Locked Loop (PLL) or the robustness of safety mechanisms like thermal shutdowns. Moreover, verifying safety conditions at the transistor level is notoriously challenging and designing system-level tests to intentionally induce predictable failures is only possible if the design inherently accommodates fault conditions. These limitations highlight the need for a more flexible and efficient verification approach that could seamlessly handle complex, mixed-signal scenarios.

The AMSV utility framework we will present addresses these challenges by enabling analog models to incorporate real-world behaviors. Additionally, the framework empowers the UVM testbench to dynamically set and adjust parameters, offering real-time control and monitoring of environmental conditions and fault scenarios, effectively verifying these features and ensuring that system responses to changes, such as frequency adjustments or safety reactions, are accurate and reliable.

The AMSV framework also facilitates continuous fault detection by enabling block-level analog models to report faults directly to the UVM testbench. This capability enhances fault detection and debugging, allowing verification teams to comprehensively test critical behaviors, from environmental resilience to safety mechanisms, and significantly advance full-chip verification for today's complex systems.

Essentially, what is required in addition to the input/output ports of the blocks in the system is a set of potentially bidirectional ports into the model of the block (not the schematic) that can control the model or from which to make observations for verification purposes. These additional ports cannot be added to the port list of the model as that would invalidate the pin accuracy of the model, which is required for model vs. schematic (MVS) checking [3] and for netlisting. Therefore, a separate mechanism must be introduced for these ports. This is where the AMSV framework plays a role.

In the following sections, we will explore the details of the framework and demonstrate how it enhances both analog models and the system-level testbench, ultimately improving the system-level verification of today's complex mixed-signal designs.

#### III. STRUCTURE OF THE AMSV UTILITY FRAMEWORK

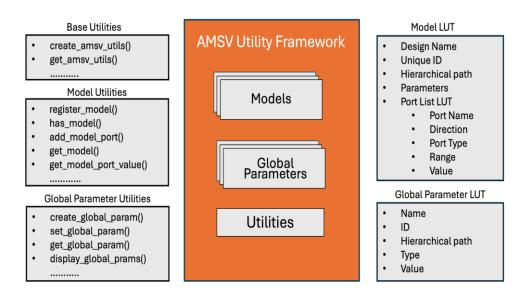

The AMSV utility framework is structured as a SystemVerilog package that includes OOP classes, lookup tables (LUTs), pre-defined macros, and other specialized utilities. This modular design integrates seamlessly with analog models and the UVM testbench, allowing for dynamic parameter control, real-time fault injection, and efficient communication between the analog models and the verification environment. Fig. 1 illustrates the framework's architecture, highlighting the core components: the model and global parameter LUTs, along with the utility methods to help with the communication and management of the components.

Figure 1. Visual illustration of the structure of the AMSV utility framework.

## A. Model LUT

The model LUT contains a comprehensive set of configuration settings and parameters specific to each analog model. This table includes essential information, such as a list of models, port details (including direction, type, and additional settings), and configuration parameters. Moreover, the model LUT facilitates access to the framework's global variables across models, streamlining parameter management and ensuring consistency in system-wide settings.

This structure enables analog models to report input range faults directly to the UVM testbench, allowing for the rapid detection of deviations from expected operating conditions. With capabilities to monitor block-level pin values and track critical metrics, the model LUT is instrumental in real-time model adjustments and fault reporting, making it essential for verifying complex mixed-signal behaviors.

#### B. Global Parameters LUT

The global parameter LUT serves as a centralized resource for storing parameters that affect multiple models or the entire verification environment. It acts as a unified source for environmental variables and system-wide settings. Typical entries include temperature, reference voltages, block failure mechanisms, and other key parameters.

The global parameter LUT allows seamless access and real-time updates from the testbench, enabling the UVM environment to dynamically influence model behavior as needed. Accessible to both the testbench and analog models, it ensures consistent parameter application across the verification environment. This structure guarantees that critical conditions are uniformly maintained, facilitating the reliable verification of complex mixed-signal interactions.

## C. Utility Methods

The AMSV framework includes a suite of utility methods that establish the primary communication channels between the UVM testbench and the analog models. These methods provide essential tools for model management, global parameter control, and signal monitoring, making the framework highly adaptable to various verification scenarios.

- Base Utilities: These methods manage and integrate the AMSV framework itself. They facilitate the creation of singleton class objects within the framework, ensuring a seamless setup and preventing integration errors, which helps maintain consistency and reliability in the use of AMSV utilities.

- Model Utilities: Designed for model management, these utilities register each analog model within the

framework, storing relevant information in the model LUT. This process allows the UVM testbench to

monitor and handle various scenarios by accessing the model data as needed.

- Global Parameter Utilities: These functions enable the testbench to dynamically set global parameters and retrieve real-time values from the models. By providing centralized control over parameters, they allow for real-time adjustments to model behavior, which is essential for simulating complex scenarios.

### D. Code Snippet

Fig. 2 provides an overview of the structure of the AMSV utility framework, illustrating how the main class organizes core components, including lookup tables and utility functions.

The AMSV package is designed to encapsulate the model and global parameter LUTs while providing utility functions that streamline communication between models and the testbench.

```

package amsv_utils_pkg;

// Model LUT

class model_utilities;

// Global Paremeter LUT

class global_utilities;

// Other Helper Signals of the package

// The Base Class of the AMSV Utility Framework

class amsv utilities:

// AMSV utility singleton class

static amsv_utilities amsv_utils = null;

// Lookup table consisting model details

model_utilities models[string];

// Lookup table for global variables

global_utilities globals[string];

// Utilities

// Private constructor to prevent direct instantiation

extern protected function new(string name);

// Create instance of AMSV Utility

extern static function amsv_utilities create_amsv_utils(string name);

// Get instance of AMSV Utility

extern static function amsv_utilities get_amsv_utils();

// Model LUT Utilities

// Registers Analog model in lookup table with name, unique ID and hierarachy

extern function void register_model(string name = "", string id = "", string hier = "");

// Returns 1 when model exists with provided unique ID

extern function bit has_model(string id);

// Adds port information of registered model

extern function void add_model_port(string id, string name, string dir, string port_type);

// Returns model utility based on unique ID

extern function model_utilities get_model(string id);

// Returns the port description of the model based on unique model ID and port name

extern function port_t get_model_port(string id, string port_name);

// Global Parameter Utilities

// Creates global variable with name, data type and value

extern function void create_global_param(string name = "", string data_type = "", real value);

// Sets global value during runtime

extern function void set_global_param(string name, real value);

// Returns global value with provided name

extern function real get_global_param(string name);

// Returns 1 when global value with provided name exists

extern function bit has_global_param(string name);

// Display Utilities

endclass

endpackage

```

Figure 2: AMSV utility framework package.

#### E. Pre-defined Utility Macros

The AMSV framework also includes a set of pre-defined utility macros designed to simplify integration and manage various operations. These macros minimize the need to type repetitive code, ensure consistent usage across analog models and verification environments, and reduce code complexity, making the framework more accessible and efficient.

Key macros provided by the AMSV framework include:

- Model registration macros: These macros streamline the setup of each analog model by initializing modelspecific configurations within the model LUT. This includes pin mappings and parametric settings, ensuring that each model is correctly registered and accessible to the UVM testbench, thereby reducing the setup time for individual models.

- Global parameter synchronization macros: These macros enable continuous observation of global parameters set by the testbench, allowing models to react to parameter changes and adjust their behavior accordingly.

- Signal monitoring macros: These macros facilitate the monitoring of critical signals within analog models, enabling the UVM testbench to detect and report deviations from expected behavior, which streamlines fault detection and debugging.

- Fault reporting macros: These macros simplify block-level fault detection by enabling direct fault reporting from the models to the testbench, allowing the UVM environment to manage fault conditions efficiently.

Fig. 3 shows examples of definitions of some key macros in the AMSV framework. While only the definitions are shown, they illustrate how these macros support streamlined operations within the framework.

```

`amsv_utils_register_model(model_name, unique_id, pin_list, param_list)

// Registers the model with specified pins and parameters in the Model LUT.

`amsv_utils_sync_globals(VAR_NAME, GLOBAL_PARAM_NAME)

// Synchronizes global parameter: GLOBAL_PARAM_NAME value set by the testbench

// for continuous observation by the models.

`amsv_utils_monitor_signal(model_name, hierarchical_path, signal)

// Enables real-time monitoring of a specified signal, allowing the

// testbench to track and debug signals.

`amsv_utils_report_fault(fault_condition, message)

// Reports a fault condition directly from the model to the UVM testbench

```

Figure 3: Key macro definitions for simplified integration of the AMSV utility framework.

These macro definitions illustrate how the AMSV framework simplifies tasks such as model registration, global parameter synchronization, signal monitoring, and fault reporting. By utilizing these macros, both modeling and verification teams can quickly configure the AMSV framework and concentrate on verifying complex behaviors that traditional setups, relying on hierarchical references or fixed testbench names, often struggle to address. This approach saves time and enables a more efficient and reliable verification process.

In the next section, we will examine case studies that showcase the AMSV framework in real-world verification scenarios, illustrating how its components enhance the accuracy and efficiency of system-level mixed-signal verification.

# IV. CASE STUDY: APPLICATION OF AMSV UTILITY FRAMEWORK TO MIXED-SIGNAL SYSTEM DESIGN

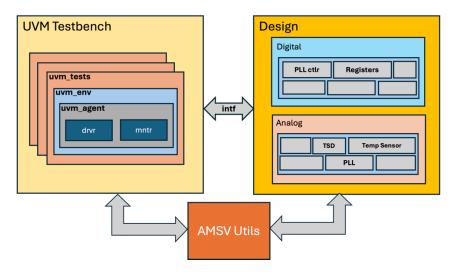

In this section, we demonstrate the application of the AMSV framework using an example System-on-Chip (SoC) design comprising both digital and analog components. Our primary objective is to showcase how to integrate the framework with analog models and the system-level UVM testbench and how this integration enables the verification of complex scenarios.

# A. Overview of the Design and Verification Environment

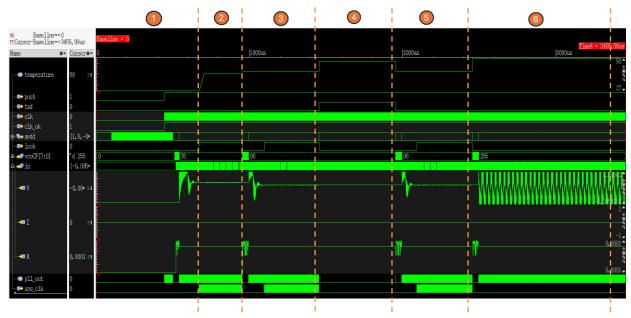

The example design includes critical mixed-signal blocks, specifically a power management unit and a phase-locked loop (PLL). The AMSV framework is employed to model the impact of environmental factors, particularly temperature, on these analog components, allowing for a more thorough verification of system-level responses under varying conditions.

The PLL block in this design is sensitive to temperature fluctuations, which causes its operating frequency to drift from the intended value. This frequency deviation is monitored by a control unit within the digital subsystem, which dynamically adjusts the PLL to maintain its desired frequency. Additionally, the design incorporates a temperature monitoring and thermal shutdown (TSD) block that is responsible for overseeing the system temperature. If the temperature exceeds the operational threshold, the TSD block is designed to shut down the system to prevent overheating and catastrophic failure.

Using the AMSV framework, we model the temperature effect on the PLL to verify whether the control unit appropriately compensates for frequency drifts caused by rising temperatures. Furthermore, to assess the system's response to safety mechanisms, we include a failure mechanism in the thermal shutdown block using the framework. This simulated fault prevents the TSD block from triggering, even when temperatures rise above safe limits. This allows us to analyze how the system reacts under potential safety-compromising conditions.

The AMSV framework facilitates the verification of these complex scenarios by integrating them into the UVM testbench. We will describe how to configure parameters such as temperature and trigger the TSD failure mechanism directly from the UVM testbench. We will then present specific test cases developed to validate these safety and performance features. Fig. 4 provides a block diagram of the verification setup, illustrating the design under test (which includes digital blocks and analog models) and highlighting the role of the AMSV utility framework as an interface between the models and the testbench. The following sections will provide detailed discussions of how the AMSV framework is incorporated into both the analog models and the UVM testbench, as well as the specific test cases developed to validate these complex scenarios.

Figure 4: Block diagram of verification setup for the example SoC design with AMSV framework integration.

# B. Modeling Analog Blocks and Integrating the AMSV Framework

We developed fully functional models for the analog subsystem using the SystemVerilog discrete electrical (also known as the user-defined nettype) approach. These models were generated with the Model-in-Minutes (MiM) tool [4], which produces distinct analog mixed-signal (AMS) and discrete mixed signal (DMS) models in Verilog-AMS and SystemVerilog respectively, and self-checking model-versus-schematic (MVS) testbenches for analog blocks from a specification. MiM allows for incorporating custom user code into model containers (shared settings that all models inherit within a project). This feature was particularly beneficial for integrating the AMSV utility framework into multiple models without modifying each specification independently.

Fig. 5 illustrates the MiM specification used to construct the Voltage Controlled Oscillator (VCO) of the PLL, specifically modeling how the system temperature impacts its behavior. By utilizing the user code section of MiM, we integrated the AMSV framework by embedding the necessary macros directly into the generated models.

| -,                                                      | Name                                      |                                       | vco                                    |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |             |                                   |    |                    |

|---------------------------------------------------------|-------------------------------------------|---------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------|----|--------------------|

| Description                                             |                                           |                                       | PLL V                                  | oltage Controlled Oscillat                                                                                                                | or with AMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SV Utility Framework                                                                                            |             |                                   |    |                    |

| Ports (Hide)                                            |                                           |                                       |                                        |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |             |                                   |    |                    |

| Name 2                                                  | Dir ?                                     | Port type                             | ?                                      | Description 2                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Range 2                                                                                                         | Behavior 2  |                                   |    |                    |

| out                                                     | output ~                                  | digital                               | ~                                      | VCO Output                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 | osc         |                                   |    |                    |

| in                                                      | input ~                                   | voltage                               | ~                                      | Input control voltage of the                                                                                                              | vco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 |             |                                   |    |                    |

| [7:0]vcoCF                                              | input v                                   | nput v digital                        |                                        | Settings for VCO center freq                                                                                                              | uency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | nox                                                                                                             | vcoCF_val w | ith protect                       |    |                    |

| enable                                                  | input v digital                           |                                       | ∨ Enable Pin                           |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 | On = enable | On = enable && !Fault with smooth |    |                    |

| bias                                                    | input v ibias                             |                                       | ∨ Input Bias Current                   |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5uA to 20uA                                                                                                     |             |                                   |    |                    |

| vdda                                                    | input v                                   | supply                                | ~                                      | Supply                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.7V to 1.9V                                                                                                    | I = On*10u  |                                   |    |                    |

| gnda                                                    | input v ground                            |                                       | ~                                      | Ground                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -10mV to 10mV                                                                                                   |             |                                   |    |                    |

| Kvco wro                                                |                                           | ~                                     |                                        | Temperatur Parameter                                                                                                                      | 25M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 |             |                                   |    | MHz                |

| temp                                                    | real                                      | ~                                     |                                        | variable to sync with AMSV                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |             |                                   | 27 | С                  |

|                                                         |                                           |                                       |                                        | •                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |             |                                   |    |                    |

|                                                         |                                           |                                       |                                        | ]                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |             |                                   |    |                    |

|                                                         |                                           |                                       | Tompo                                  | ratura Difference                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TEMP NOMINAL                                                                                                    |             |                                   |    |                    |

| delta_T                                                 | wreal                                     | ~                                     | _                                      | rature Difference                                                                                                                         | (temp+273)-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TEMP_NOMINAL                                                                                                    |             |                                   |    | к                  |

| delta_T<br>temp_freq_dr                                 | wreal                                     | v                                     | Freque                                 | ency drift due to temperature//                                                                                                           | (temp+273)-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FF*delta_T                                                                                                      | posedge opp |                                   |    | K<br>Hz            |

| delta_T<br>temp_freq_dr<br>Ctrl                         | wreal                                     | ·<br>·                                | Freque                                 | ency drift due to temperature///                                                                                                          | (temp+273)-<br>TEMP_COEF<br>clip(V(in) - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FF*delta_T<br>.25, -500m, 500m)                                                                                 | posedge osc |                                   |    | K<br>Hz<br>V       |

| delta_T<br>temp_freq_dr                                 | wreal                                     | ·<br>·                                | Contro<br>Center                       | ency drift due to temperature<br>ol Voltage<br>Frequency                                                                                  | (temp+273)-<br>TEMP_COEI<br>clip(V(in) - 1<br>2.374G + 500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -F*delta_T<br>.25, -500m, 500m)<br>0k*vcoCF_val                                                                 | posedge osc |                                   |    | K<br>Hz            |

| delta_T temp_freq_dr Ctrl F0                            | wreal rift wreal real wreal               | ·<br>·                                | Contro<br>Center                       | ency drift due to temperature<br>ol Voltage<br>Frequency<br>stor Frequency                                                                | (temp+273)-<br>TEMP_COEI<br>clip(V(in) - 1<br>2.374G + 500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -F*delta_T<br>.25, -500m, 500m)<br>0k*vcoCF_val<br>Ctrl)-temp_freq_drift                                        | posedge osc | enable                            | 0  | K<br>Hz<br>V<br>Hz |