# The beginning of new norm: CDC/RDC constraints signoff through functional simulation

Suhas D S, Ponsankar Arumugam, Deepmala Sachan, Ritesh Jain

Intel Technology India Pvt. Ltd.

#### INTRODUCTION

. Cualifiers. SVA capturing and verifying data transfer conditions.

.Reset Ordering: Assertions validating reset ordering to prevent race conditions.

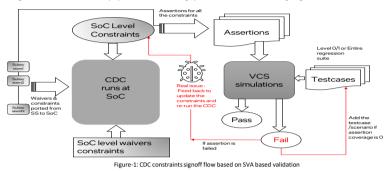

# SVA based functional simulation signoff for CDC/RDC Constraints

Static analysis checks are indispensable in verifying CDC and RDC in complex SoCs. These checks rely on various architectural assumptions to guide analysis. These assumptions play pivotal role in Full chip CDC analysis; hence it is imperative to validate them before final CDC/RDC closure. Following steps have been taken for SVA based functional simulation signoff for all assumptions which has been converted to constraints during static analysis

2. Plugin the SV assertions in functional simulation and Validation of assertions.

rate the SystemVerilog Assertion (SVA) for each architecture assumptions.

Sign-off strategy for Uncovered Assertions: The goal is to get 100% assertion coverage however there would be certain exceptions due to SVA

coding and testbench limitations. Such properties should be thoroughly reviewed with the architect and get sign-off.

### CASE Study: A Practical Exploration

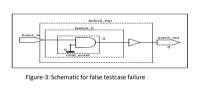

False test failures due to testbenchArchitecture: Testcases are run on various TB models based on use cases where certain portion of design is stubbed out. When a design is stubbed out, a passive value is driven on input signals to avoid "x" propagation. In such cases, if value driven/forced is incorrect, the assertion will fail. In this case the testbench should be modeled to the architectural behavior. Many such instances were corrected in testbanch.

In the Figure-3 the one pin of the AND gate is tied to zero in rtl. So SCA is given w.r.t the RTL tie off value, but during simulation there is force on this signal and the testcase used to toggling from 0-> x -> 0 which resulted in CDC SVA failure.

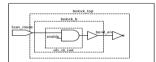

2. Removal of wrongly added set case analysis: These constraints were added on the output port of the unit level runs to match the abstract validation errors at SoC. This need not to be set, as internal logic will set according to the mode of operation.

We can see that in the Figure-4 the "enable" is ANDed with "scan\_mode" inside the "sib\_sti\_inst" module, and in "scan\_mode" that will be"0'in functional test. So, in this case the set case value for "bond\_en" should be 0 for functional model analysis.

Figure-4: Schematic for wrong set case assumption

#### Summary : Methodology recommendations

### As part of this methodology, we recommend having 100% Assertion coverage for constraints signoff however certain exceptions can be taken due to 96.7% SVA coverage however remaining 3.3 % properties are categorized as invalid due to architectural assumptions. Along with the modification of testbench to address uncovered assertions we have made following constraints update to strengthen the CDC analysis. Removal of wrongly added set case analysis: These constraints were added on the output port of the unit level runs to match the abstract validation errors at SOC. this need not to be set, as internal logic will set according to the mode of operation. set\_case\_analysis -name "soc parl.scan\_or\_out" value 0 Removal of wrongly added "reset-filter-path": It was wrongly added during CDC analysis to reduce huge waiver count: this was put to waive only where to\_obj is present, but assertions are generated for from\_sit to to\_sit, which is huge verification overhead. Correction of SCA constraints: Few wrongly added constraint were corrected to its functional values. Correction of data qualifier: All async FiFOs require proper qualifier constraints to avoid false assertions. qualifier -det\_qual -dFFO-empty-signab -from\_obj -your.FiFO-register >-to\_citk <destination-clock> qualifier -det\_qual -dFFO-empty-signab -from\_obj -your.FiFO-register >-to\_citk <destination-clock> count which has drastic impact on simulation TAT.

#### CONCLUSIONS

During our journey of validating assumptions through SVA, we came across many challenges and learning. Some of key validation learnings are:

- Issues with reset initialization: All RDC assertions with respect to reset domain crossing require analysis from time zero as it checks for destination reset to be asserted way before source reset.

- Strategy to preload or initialize memories with in-active values: In certain scenarios this approach has been used to avoid false failures/Uncovered assertions.

- 3. Failures due to power off conditions: some false assertion failures have been noticed in power aware simulations due to "x" propagation during the power off. The Assertions need to be modeled accordingly to disable them during power off condition.

- 4. Assertionshaving in active clocks in functional mode: since our checks are done in functional mode, Test/DFX clocks and logic are not active hence, assertion containing them can't be hit as they are not active. The constraints were reviewed and SVA's were removed for such instances

- Absence of abstract for HIP/Memories: All hard IP and memories should have an abstract model to avoid unnecessary assertions for simulation overhead.

- 6. Testbench Modelling: To avoid false failure, testbench models should be chosen appropriately so that undriven/falsely driven signal doesn't give unwanted coverage or failure.

Next steps: Exploration of formal for assertion validation: Multi die Graphics SOC's with huge complexity has lengthy regression cycles. Hence we will also explore implementing formal tools to achieve shorter runtime and quicker turn around. The challenge will be to have appropriate assumptions.

## REFERENCES

[1]. Amit Kulkarni, Suhas D S, Deepmala Sachan, "Evolution of CDC recipe: Learning through real case studies and methodology improvements", in DVCON 2021

[2]. Rohit Kumar Sinha, "Enhancing Quality and Coverage of CDC Closure in Intel's SoC Design", in DVCON 2020

Intel Technology India Pvt. Ltd.