#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

### Practical Asynchronous SystemVerilog Assertions

**Doug Smith**

### Asynchronous Assertions

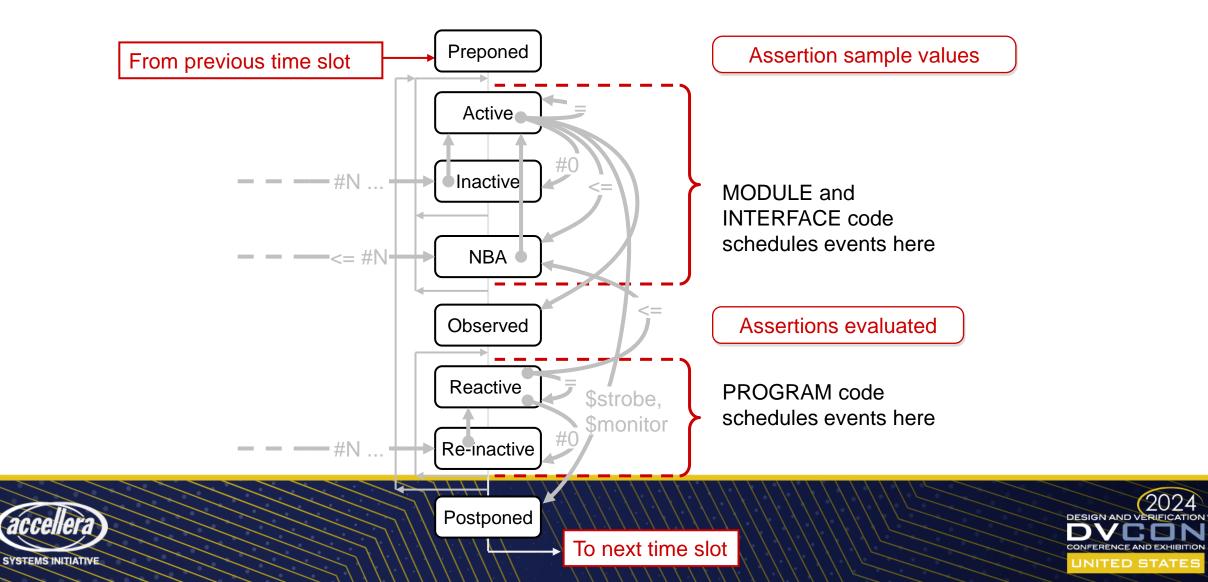

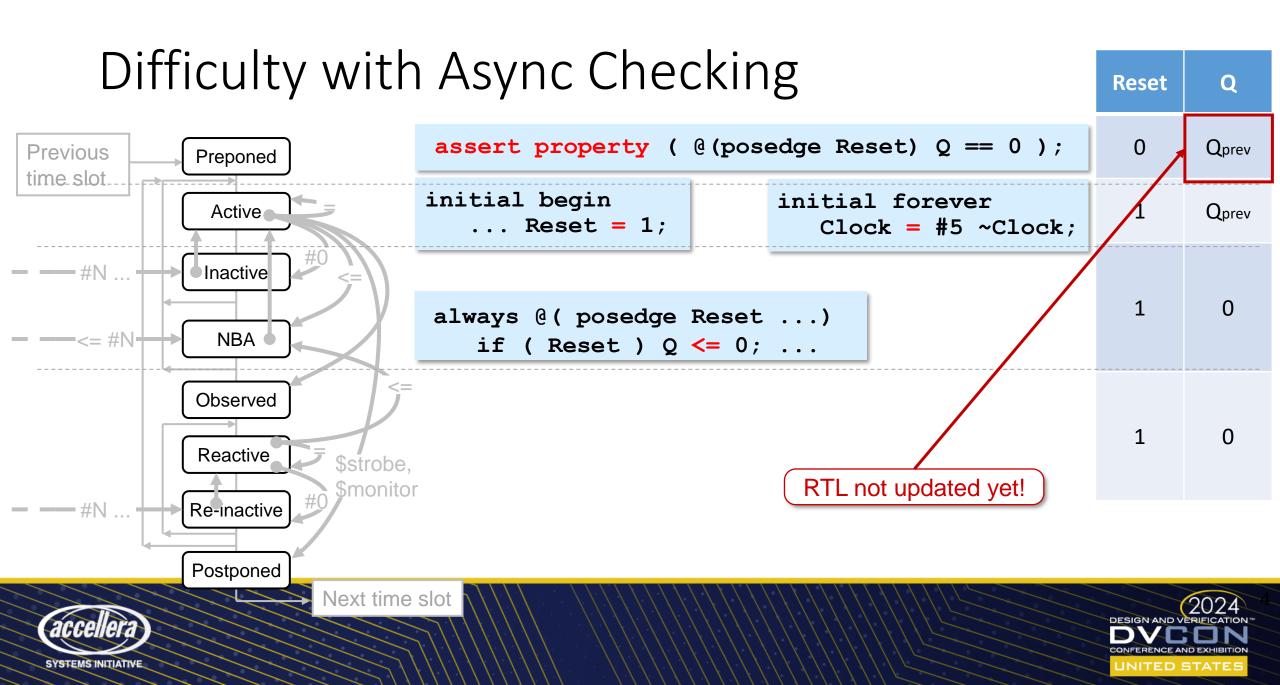

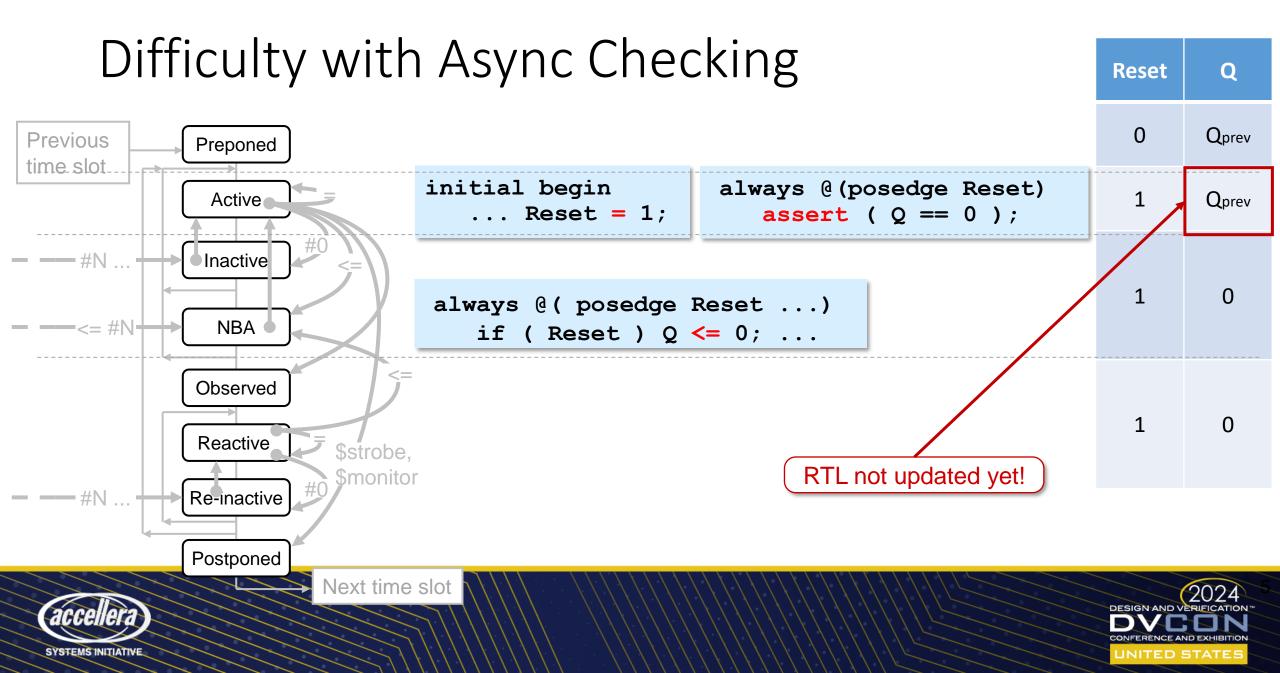

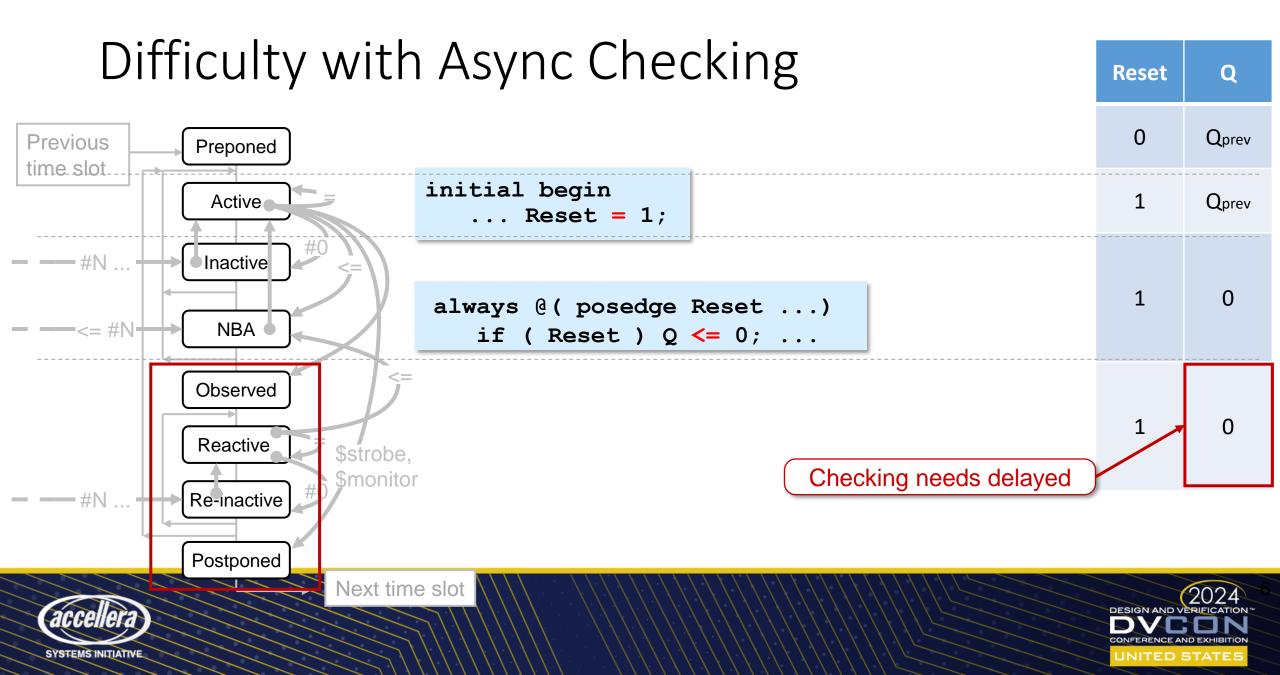

## SystemVerilog Scheduler

### Requirements for Async Assertions

Portable across simulators Deterministic Thorough – checks in both directions

In other words, *practical asynchronous assertions*

See DVCon 2010 paper, <u>"Asynchronous Behaviors Meet Their Match with</u> <u>SystemVerilog Assertions</u>," for other solutions and handling async protocols https://www.doulos.com/knowhow/systemverilog/asynchronous-behaviors-meet-their-match-with-systemverilog-assertions/

#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

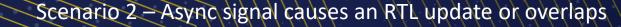

Common Methods for Async Checking

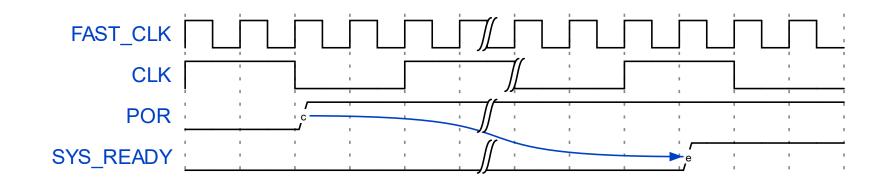

## Synchronous, oversampling, or fast clock

default clocking cb @ (posedge CLOCK) ; endclocking

OR default clocking cb @ (posedge FAST\_CLK) ; endclocking

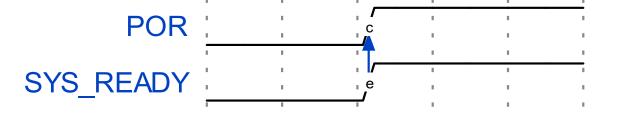

assert property ( \$rose(POR) |-> ##[0:\$] SYS READY );

What about glitches?

### Event based methods

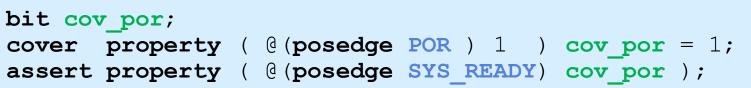

bit cover\_por = 0; cover property ( @(posedge POR) 1 ) cover\_por = 1;

Then ...

assert property ( @(posedge SYS\_READY) cover\_por );

What if SYS\_READY never occurs?

### Pros and Cons

Oversampling

Pro – works with any verification flow (sim, emulation, formal, prototyping) Con – glitchy RTL behavior may go undetected

Coverage

Pro – easy to write sophisticated scenarios

Con – overlapping events undetected or event never occurs

Solution? Delay assertion checking ...

###

#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

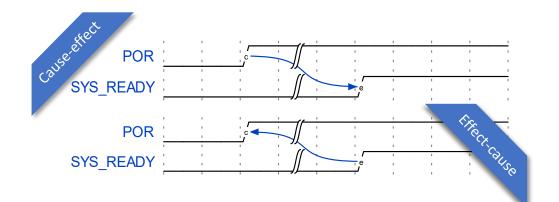

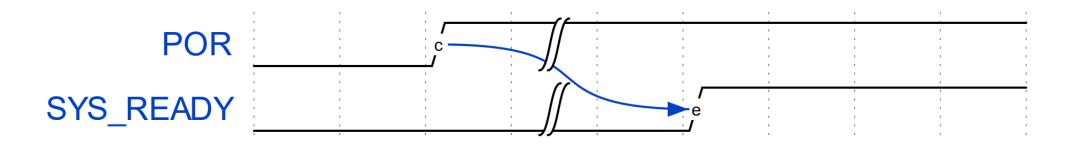

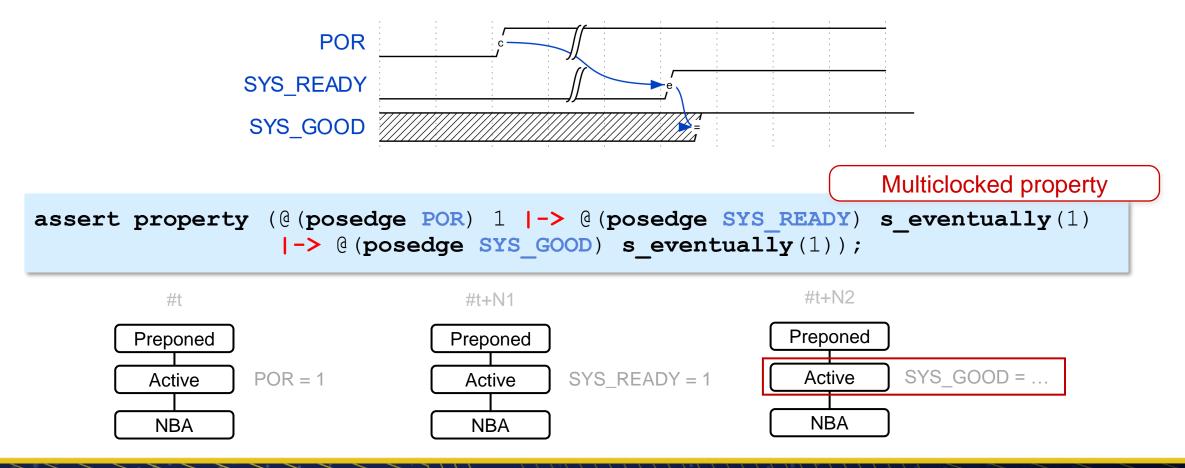

## Cause and Effect

# Async signal causes another async event

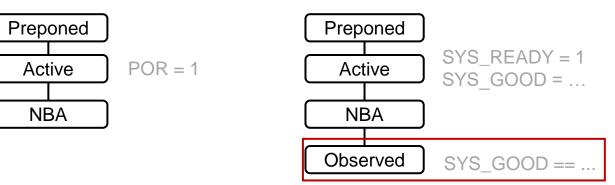

assert property ( @ (posedge POR) 1 |-> @ (posedge SYS\_READY) 1 );

- This is a *weak* property

- Make it strong

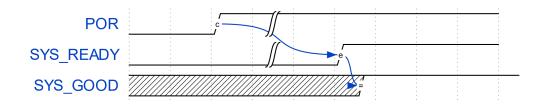

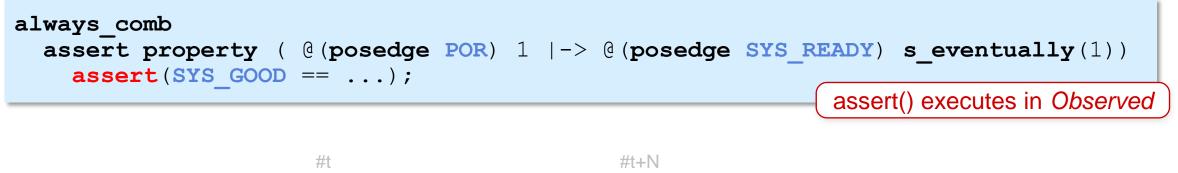

assert property ( @ (posedge POR) 1 |-> @ (posedge SYS\_READY) s\_eventually(1) );

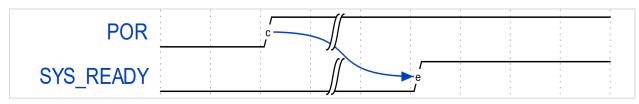

### Coverage Alternative

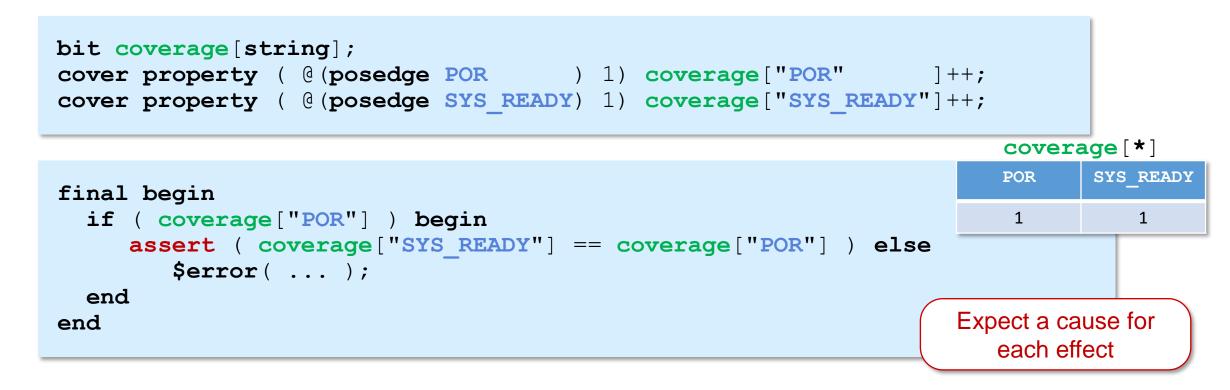

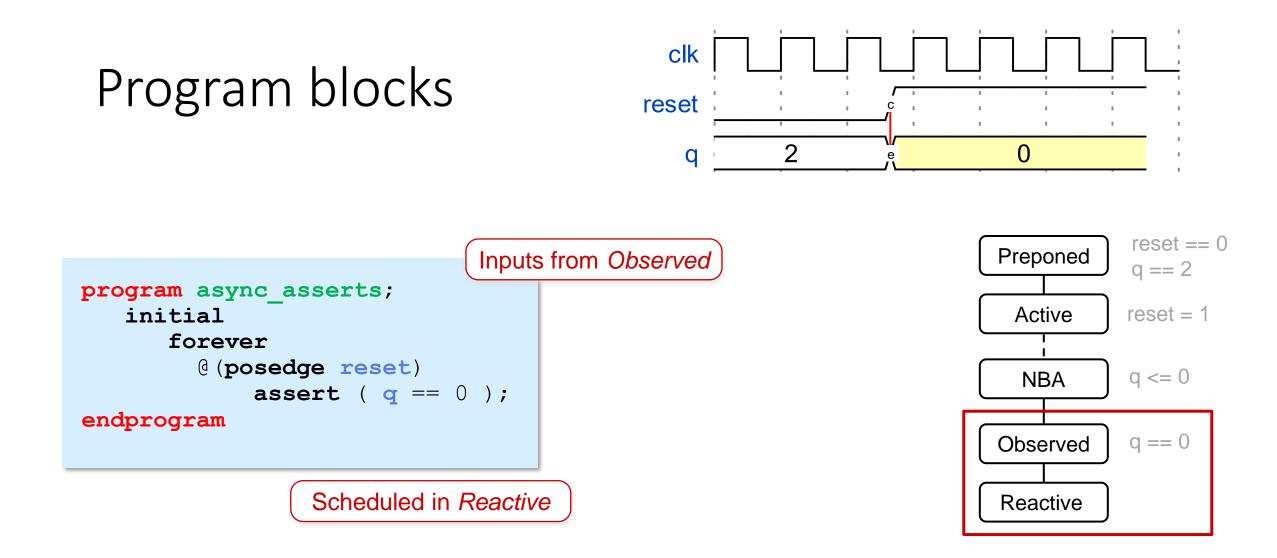

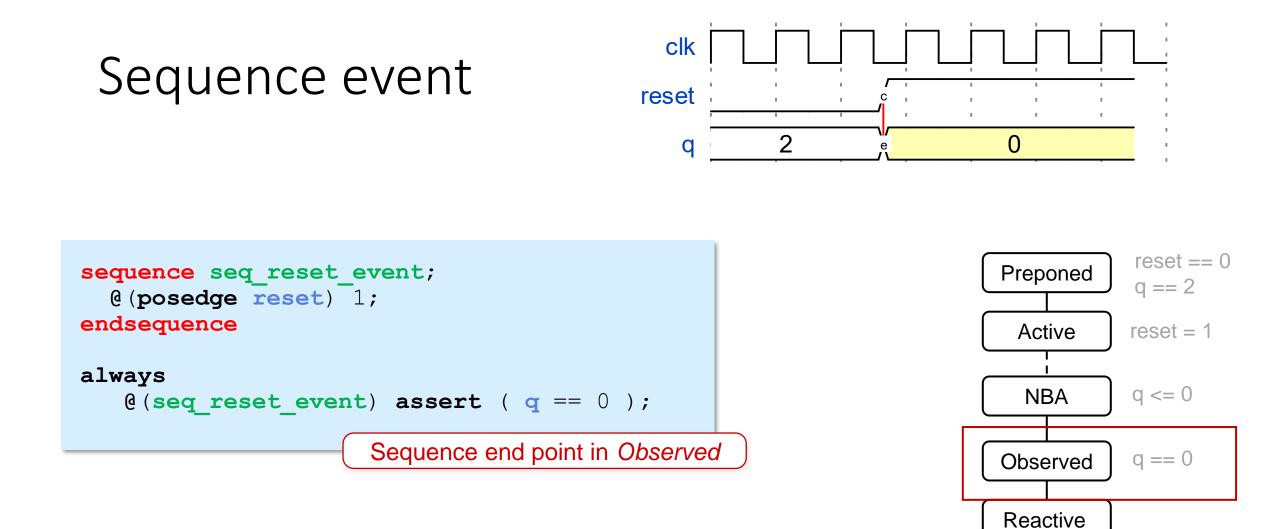

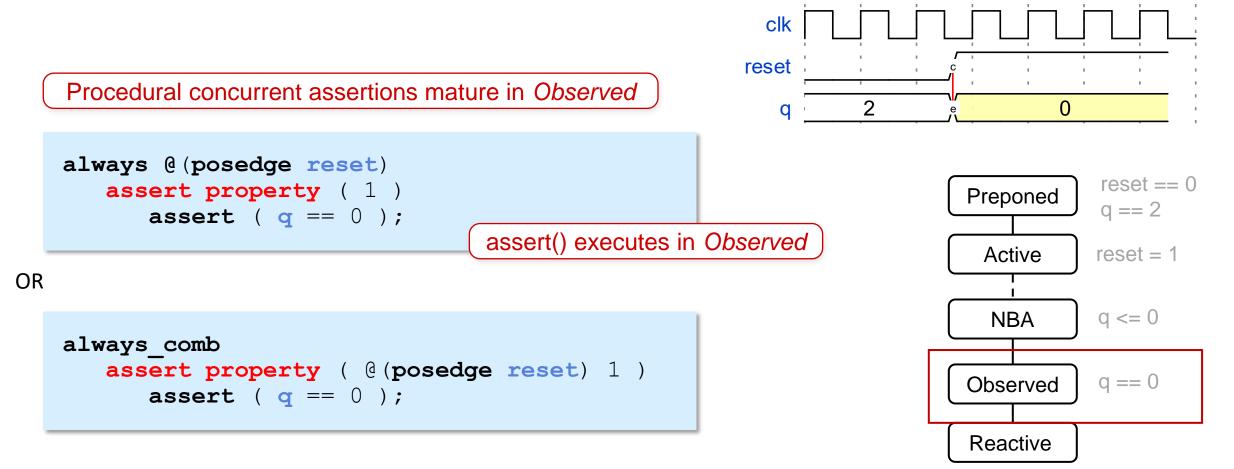

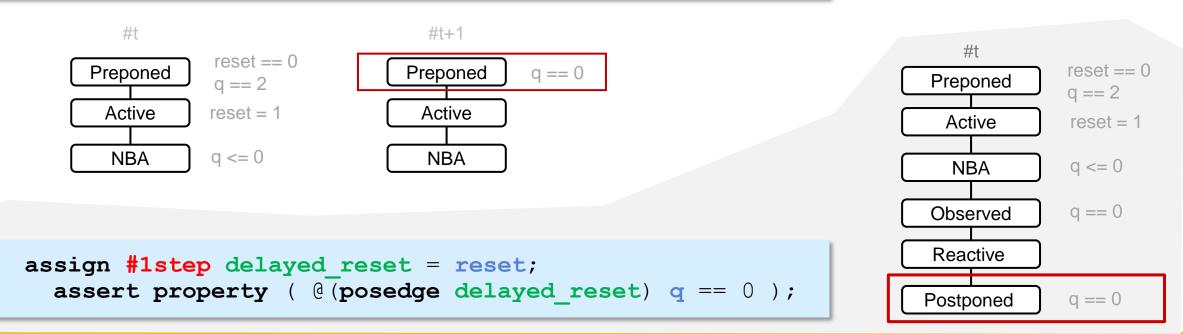

Scenario 2 – Async signal causes an RTL update

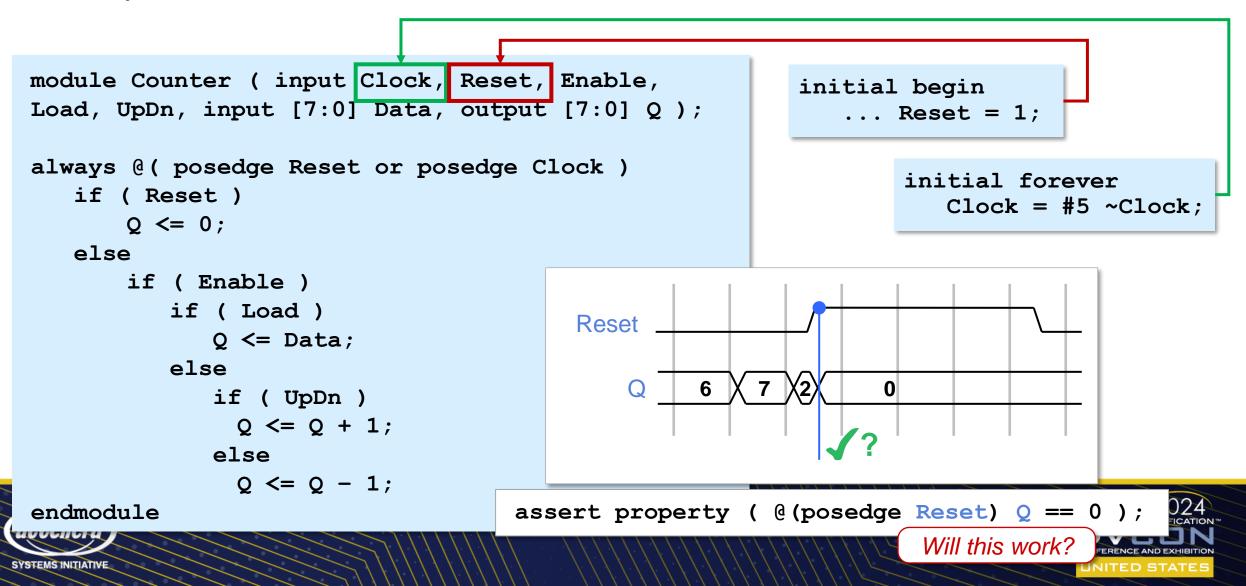

Scenario 2 – Async signal causes an RTL update

accellera

### Procedural concurrent assertions

### A timing delay

# Async event causes async event with updates

## Overlapping behavior

Scenario 3 – Async event causes async event with updates

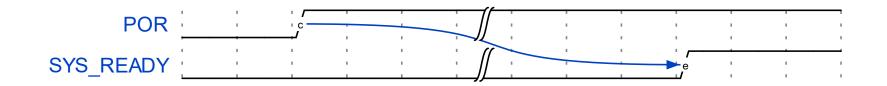

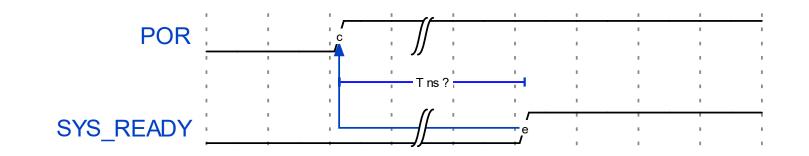

# Async timing window

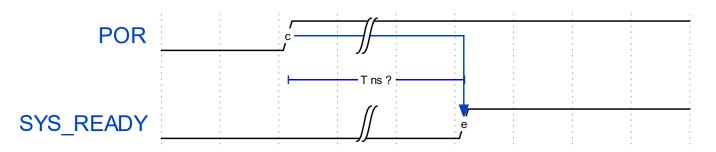

```

property prop_check_timing;

realtime start;

realtime finish;

@(posedge POR) (1, start = $realtime) |->

```

```

@(posedge SYS_READY) (1, finish = $realtime) ##0

(finish - start) == timing_window;

```

```

endproperty

```

assert property ( prop\_check\_timing );

## CONFERENCE AND EXHIBITION

UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

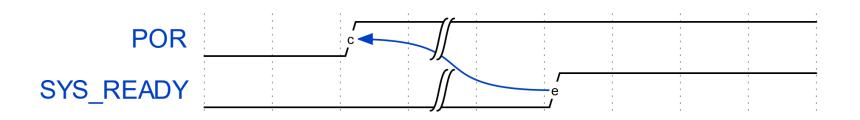

## The Effect and its Cause

assert property ( @(posedge SIS\_READI) Cov\_por );

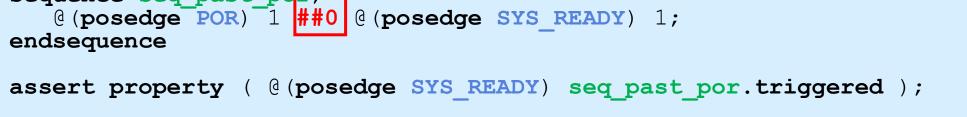

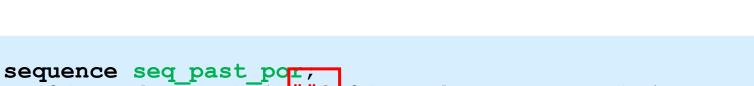

OR sequence seq\_past\_por;

@(posedge POR) 1 ##1 @(posedge SYS\_READY) 1;

endsequence

assert property ( @(posedge SYS\_READY) seq\_past\_por.triggered );

Not as portable

### Async event caused by another event

Avoid - inconsistent support across tools

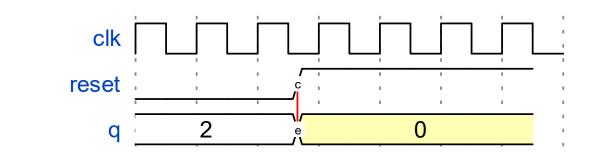

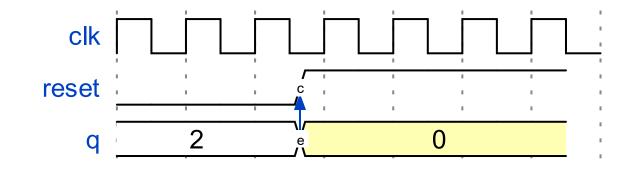

# RTL updated by async event

```

bit cov_reset;

always @ (posedge reset) cov_reset = 1;

always_comb

assert property ( @ (q) 1 )

assert ( cov_reset )

cov_reset = 0;

else $error ( ... );

```

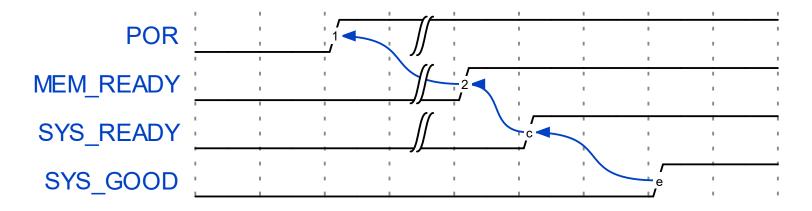

# Multiple causes for a sequence of events

bit cov\_por, cov\_mem\_ready, cov\_sys\_ready; cover property (@(posedge POR) 1) cov\_por = 1; cover property (@(posedge MEM\_READY) 1) cov\_mem\_ready = 1; cover property (@(posedge SYS\_READY) 1) cov\_sys\_ready = 1; assert property (@(posedge SYS\_GOOD) cov\_por && cov\_mem\_ready && cov\_mem\_ready && cov\_sys\_ready );

# Async timing window effect-and-cause

### DESIGN AND VERIFICATION **CONFERENCE AND EXHIBITION**

#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

## Summary

### Recommendations

### Asynchronous bus protocols

Use multi-clocked properties (usually straightforward)

### Asynchronous controls

Oversampling generally good enough

Coverage approach works in most cases (plus bonus of functional coverage)

Other scenarios, find a way to delay the checker's sampling

#### UNITED STATES

SAN JOSE, CA, USA MARCH 4-7, 2024

## Questions?

#### Examples available at: https://edaplayground.com/x/qB72

acce