# A Hybrid Verification Approach for Cache Coherent Systems: Functionality and Performance

Jiang-Tang Xiao<sup>1</sup>, Yung Cheng Chen<sup>2</sup>, Harish Peta<sup>2</sup>, Osmond Yao<sup>1</sup>

<sup>1</sup> MediaTek Inc. <sup>2</sup> Cadence Design Systems

## VERIFICATION GOAL

## Cache coherent systems are critical but challenging to verify:

- Lack of meaningful stimulus to test the cache protocol

- Need for a system coherent checker to guard functionality

- Need for a systematic methodology to evaluate system performance

### Proposes a comprehensive verification approach:

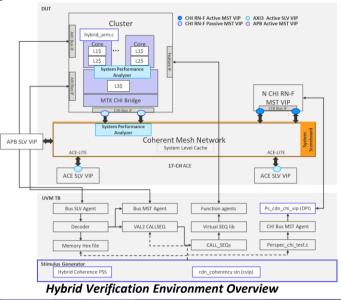

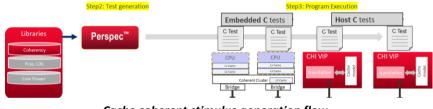

- Perspec-built cache coherent library generates C tests for snoop operations

APB SLV VI

- CHI VIP's protocol coverage reviewed for verification strength

- Custom CHI UVM sequence tested for system performance

- System Verification Scoreboard ensures cache coherency correctness

- System Performance Analyzer measures bandwidth and latency

## **PROPOSED METHODOLOGY (1)**

#### **Proposed Verification Flow**

architecture design.

1. Stress cache coherent stimulus generation for function - Supports 9 scenario groups of cache coherency

- 2. System verification scoreboard connected to guard cache protocol

- 3. System performance analysis to evaluate if there is a performance drop

4. CHI functional coverage development to ensure the quality of test regression

Cache coherent stimulus generation flow

RESULT

-15% bandwidth drop compare to the pr

Identifying corner RTL issues related to incorrect system

•Finding a 15% performance drop due to incorrect micro-

Identification of bandwidth performance drop

cache line state that cause system bus fabric hang.

# PROPOSED METHODOLOGY (2)

#### **Performance Verification Flow**

- 1. Developed for the CHI VIP L3 cache read-hit sequence

- 2. Recorded as input for the System Performance Analyzer

- 3. Analyzes bandwidth of test scenarios between the projects

Trend graphs of CHI VIP bandwidth

## CONCLUSION

1. Describe how the hybrid environment verifies the cache coherency system between cores and CHI-VIP by utilizing Perspec.

2. Introduce the system performance analyzer to obtain the performance raw data for comparison.

3. Collect functional coverage to prove the quality of verification.

| CATEGORY                                                                                                      | EXPECTED       | UNCOVERED    | COVERED  | PERCENT       |                        |       |        |        |       |      |       | Variables for Group Instar | ice           |           |          |

|---------------------------------------------------------------------------------------------------------------|----------------|--------------|----------|---------------|------------------------|-------|--------|--------|-------|------|-------|----------------------------|---------------|-----------|----------|

| Variables                                                                                                     | 1468           | 235          | 1233     | 83.99         |                        |       |        |        |       |      |       | uvm_test_top.infratba_tes  | Lenv.CHI_RN_S | SLV_CMNO  | I.monite |

| Crosses                                                                                                       | 5380           | 536          | 4844     | 90.04         |                        |       |        |        |       |      |       | VARIABLE                   | EXPECTED      | UNCOVERED | COVERS   |

| Source File(s) :<br>/mtklib/soft/verifiCadence/11.30.094-20231220/tools.lnx86/denali_64bit/ddvapi/sv/coverage |                |              |          |               |                        |       |        | Cour   |       |      |       | QoS                        | 16            |           | 5        |

|                                                                                                               |                |              |          |               |                        |       |        | IC ON  | rage. | svn  |       | RegOpCode                  | 70            |           | b        |

| 12 Instances:                                                                                                 |                |              |          |               |                        |       |        |        |       |      |       | WriteDataOpCode            | (             |           | 1        |

| NAME                                                                                                          |                |              |          |               |                        | SCORE |        | T GOAL | AT DI | AUTO | PRINT | CompDataOpCode             | 2             |           | Ó        |

| NAME                                                                                                          |                |              |          |               |                        |       | WEIGHT |        |       | MAX  |       | CompOpCode                 | 4             |           | 2        |

| uvm test top.infratba test.env.CHI RN MST MP0.monitor.coverModel.ltemEndedCover                               |                |              |          |               |                        |       | 1      | 100    | 1     | 64   | 64    | Size                       |               |           | D.       |

| uvm test top                                                                                                  | o.infratba tes | stenv.CHI RN | MST MP1  | monitor.cove  | Model.ltemEndedCover   | 86.99 | 1      | 100    | 1     | 64   | 64    | TagOp                      | 4             |           | ð        |

| uvm test top                                                                                                  | .infratba tes  | Lenv.CHI RN  | MST MP2. | monitor.cove  | rModel.ltemEndedCover  | 86.51 | 1      | 100    | 1     | 64   | 64    | NonSecure                  | 1             |           | ð.       |

|                                                                                                               |                |              |          |               | Model.ltemEndedCover   |       |        | 100    | 1     | 64   | 64    | NonSecureExt               | 2             |           | 1        |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | 1     | 64   | 64    | StashNIDValid              | 1             |           | 0        |

|                                                                                                               |                |              |          |               | erModel.ItemEndedCover |       |        | 100    | 1     | 64   | 64    | StashLPIDValid             |               |           | )        |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | 1     | 64   | 64    | Endian                     | 1             |           | 5        |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | 1     | 64   | 64    | Deep                       |               |           | 2        |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | 1     | 64   | 64    | LikelyShared               |               | <u> </u>  |          |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | 1     | 64   | 64    | Order                      |               |           |          |

|                                                                                                               |                |              |          |               | erModel.ltemEndedCover |       |        | 100    | - 1   | 64   |       | MemAttr<br>SnpAttr         |               |           |          |

|                                                                                                               |                |              |          |               |                        |       |        |        | - 1   |      |       |                            |               |           |          |

| uvm_test_top                                                                                                  | o.infratba_tes | stenv.CHI_RN | SLV_CMN  | 7.monitor.cov | erModel.ltemEndedCover | 77.13 | 1      | 100    | 1     | 64   | 64    | DymDomain                  | 1             |           | ٥.       |

83% single coverpoints and 90% cross coverpoints of the CHI interface protocol

# ΜΕΟΙΛΤΕΚ

## ACKNOWLEDGMENTS

current\_project

A previous\_project

For any further details, please send an email to the following address: Jiang-Tang.Xiao@mediatek.com.

# cādence°

## © Accellera Systems Initiative