### UNITED STATES

SAN JOSE, CA, USA FEBRUARY 27-MARCH 2, 2023

# It's Not Too Late to Adopt: The Full Power of UVM

Kathleen Wittmann

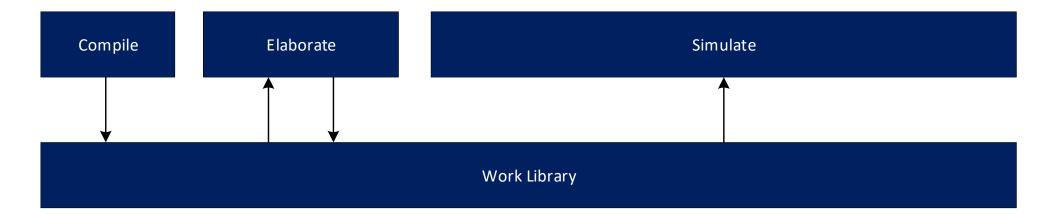

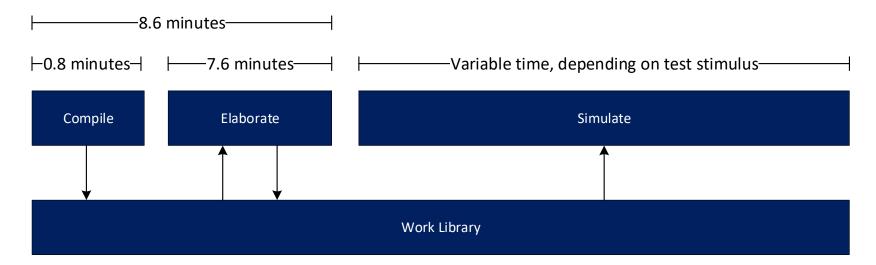

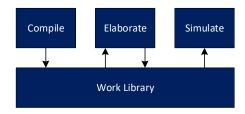

## Simulation Flow

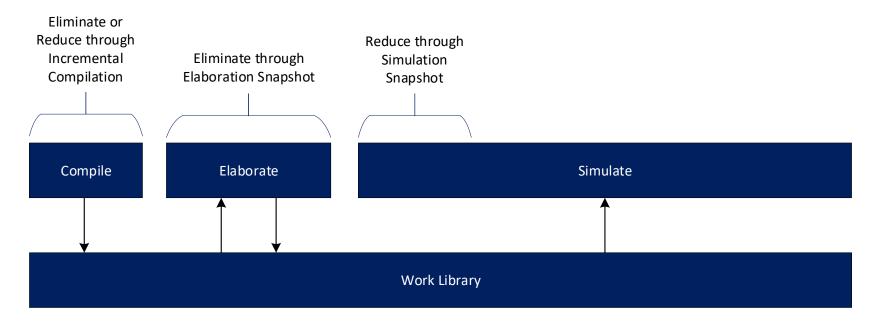

## Methods for Improving Simulation Efficiency

### Incremental Compilation:

- Once compiled, only modified files are recompiled.

- Saves compilation time.

### Elaboration Snapshots:

- Design and testbench are elaborated once. Subsequent testcase runs go straight to simulation.

- Saves compilation and elaboration time.

### Simulation Snapshots:

- A snapshot is taken at some point in a simulation. Subsequent testcase runs begin at that point.

- Saves compilation, elaboration, and simulation time.

# Requirements for Incremental Compilation and Elaboration Snapshots

- Same Work Library across tests

- The same static testbench across tests

```

class dut_env extends uvm_env;

'uvm_component_utils(dut_env)

dut_env_config m_env_cfg;

'ifdef USB VIP

usb_agent m_usb_agent;

endif

(string name, uvm component parent);

extern

extern virtual function void build phase

(uvm phase phase);

extern

function void connect phase (uvm phase phase);

endclass: dut env

function void dut_env::build_phase (uvm_phase phase);

super.build_phase(phase);

if (!uvm confiq db #(dut env confiq)::qet(this,"","dut env confiq", m env cfq)) begin

`uvm_error("CONFIG_DB", "dut_env_config not found")

end

'ifdef USB VIP

m_usb_agent = usb_agent::type_id::create("m_usb_agent", this);

`endif

endfunction: build phase

```

A different static environment results, based on whether USB\_VIP is defined or not

## Simulation Flow

If the testbench is the same from test to test, the flow can be optimized to skip right to simulation.

In a 2000-test regression, this optimization saves nearly 12 days of processing time.

### Rewritten UVM Environment

#### **Statically Configured**

```

class dut env extends uvm env:

`uvm_component_utils(dut_env)

dut env confiq m env cfq;

'ifdef USB UIP

usb_agent m_usb_agent;

endif

function

(string name, uvm_component parent);

extern

extern virtual function void build phase

(uvm phase phase);

extern

function void connect phase (uvm phase phase);

endclass: dut env

function void dut env::build phase (uvm phase phase);

super.build_phase(phase);

if (!uvm confiq db #(dut env confiq)::qet(this,"","dut env confiq", m env cfq)) begin

'uvm error("CONFIG DB", "dut env config not found")

end

'ifdef USB VIP

m_usb_agent = usb_agent::type_id::create("m_usb_agent", this);

endif

endfunction: build phase

```

#### **Dynamically Configured**

```

class dut env extends uvm env;

`uvm_component_utils(dut_env)

dut env confiq m env cfq;

usb agent

m usb agent;

(string name, uvm component parent);

extern

function

extern virtual function void build phase

(uvm phase phase);

function void connect phase (uvm phase phase);

extern

endclass: dut env

function void dut env::build phase (uvm phase phase);

super.build_phase(phase);

if (!uvm_config_db #(dut_env_config)::get(this,"","dut_env_config", m_env_cfg)) begin

'uvm error("CONFIG DB", "dut env config not found")

if (m_env_cfg.has_agent_usb) begin

uvm confiq db #(usb agent confiq)::set( this,

"m_usb_agent",

"usb_agent_config",

m env cfg.m usb agent cfg)

m usb agent = usb agent::type id::create("m usb agent", this);

endfunction: build phase

```

# The UVM Test Configures the UVM Environment

```

class dut env confiq extends uvm object;

`uvm object param utils(dut env confiq)

// Agent Configuration Objects

axi agent config t

m axi agent cfg;

usb agent config

m usb agent cfg;

// Other Variables

bit

has agent axi

bit

has agent usb =

bit

has scoreboard = 1;

hit

has coverage

// Register Block

dut block map

dut rm;

extern function new(string name = "dut env config");

endclass: dut env confiq

```

```

class dut_test_base extends uvm_test;

extern

function void build_phase

(uvm_phase phase);

extern virtual function void configure dut env(dut env config cfg);

endclass: dut test base

function void dut test base::build phase(uvm phase phase);

// Create the Environment Configuration Object

m_dut_env_cfg = dut_env_config::type_id::create("m_dut_env_cfg");

configure_dut_env(m_dut_env_cfg);

// Create and configure the Agent Configuration Objects

// Assign the Agent Configuration Objects in the Environment Configuration Object

// Put the environment configuration in the uvm config db

uvm confiq db #(dut env confiq)::set(this, "*", "dut env confiq", m dut env cfq);

// Create the environment

m env = dut env::type id::create("m env", this);

endfunction: build phase

function void dut test base::configure dut env (dut env config cfq);

cfq.has agent usb = 1;

endfunction: configure dut env

```

### **UVM** Test Inheritance

```

class dut_test_base extends uvm_test;

function void build phase

(uvm phase phase);

extern virtual function void configure dut env(dut env config cfq);

endclass: dut test base

function void dut_test_base::build_phase(uvm_phase phase);

// Create the Environment Configuration Object

m dut env cfq = dut env config::type id::create("m dut env cfg");

configure_dut_env(m_dut_env_cfg);

// Create and configure the Agent Configuration Objects

// Assign the Agent Configuration Objects in the Environment Configuration Object

// Put the environment configuration in the uvm_config_db

uvm_config_db #(dut_env_config)::set(this, "*", "dut_env_config", m_dut env cfq);

// Create the environment

m_env = dut_env::type_id::create("m_env", this);

endfunction: build phase

function void dut test base::configure dut env (dut env config cfg);

cfg.has agent usb = 1;

endfunction: configure dut env

```

#### has agent usb will be 1

class test\_with\_usb extends dut\_test\_base;

super.build\_phase(phase);

endfunction: build phase

```

`uvm_component_utils(test_with_usb)

...

extern function void build_phase (uvm_phase phase);

endclass: test_with_usb

function void test_with_usb::build_phase(uvm_phase phase);

super.build_phase(phase);

endfunction: build_phase

has agent usb will be 0

class test_without_usb extends dut_test_base;

`uvm_component_utils(test_without_usb)

...

endclass: test_without_usb

function void test_without_usb::configure_dut_env (dut_env_config cfg);

cfg.has_agent_usb = 0;

endfunction: configure_dut_env

function void test_without_usb::build_phase(uvm_phase phase);

```

# Requirements for Incremental Compilation and Elaboration Snapshots

- Same Work Library across tests

- The same static testbench across tests

Dynamic Configuration of the UVM Environment enables these requirements to be met.

**Incremental Compilation & Elaboration Snapshots are now a reality!**

## Simulation Snapshots through Sequence Override

```

class test_spi extends dut_test_base;

`uvm_component_utils(test_spi)

...

extern task run_phase(uvm_phase phase);

endclass: test_spi

task test_spi::run_phase(uvm_phase phase);

seq_spi_t t_seq = seq_spi_t::type_id::create("t_seq");

phase.raise_objection(this);

assert(t_seq.randomize());

t_seq.start(null);

phase.drop_objection(this);

endtask: run_phase

```

Instead of the 1:1 UVM Test to UVM Sequence ratio on the left, sequence override enables a 1:N ratio

```

class test usb extends dut test base;

'uvm component utils(test usb )

seq init dut init seq;

usb seq base stim seq;

virtual task run phase(uvm phase phase);

phase.raise objection(this);

'uvm info(get type name(), "Starting initialization", UVM LOW)

init_seq = seq_init_dut::type_id::create("init_seq");

init_seq.start(null);

// Simulation snapshot is created at this point

// Details of creating this snapshot are out of scope for this paper

"uvm info(qet type name(),"Starting stimulus, which can be overriden", UVM LOW)

stim seq = usb seq base::type id::create("stim seq");

stim_seq.start(null);

phase.drop_objection(this);

endtask: run phase

endclass: test usb

```

# Sequence Override through Inherited Sequence Classes Class USD\_SEQ\_Dase extends dut\_SEQ\_Dase; 'uvm\_object\_utils(usb\_seq\_base)

```

class test usb extends dut test base;

'uvm component utils(test usb )

seq init dut init seq;

usb seq base stim seq;

virtual task run_phase(uvm_phase phase);

phase.raise objection(this);

`uvm info(get type name(),"Starting initialization",UVM LOW)

init_seq = seq_init_dut::type_id::create("init_seq");

init seq.start(null);

// Simulation snapshot is created at this point

// Details of creating this snapshot are out of scope for this paper

`uvm info(qet type name(),"Starting stimulus, which can be overriden",UVM LOW)

stim_seq = usb_seq_base::type_id::create("stim_seq");

stim_seq.start(null);

phase.drop_objection(this);

endtask: run phase

endclass: test usb

```

```

class usb_seq_base extends dut_seq_base;

`uvm_object_utils(usb_seq_base)

// Declare USB-SPECIFIC sequencers, sequence items, sequences, and

// register models that can be used by derived classes

// Declare USB-SPECIFIC commonly used functions and tasks

task body();

// Do USB-SPECIFIC stimulus and/or create USB-SPECIFIC transactions

// for use by derived classes

endtask: body

endclass: usb_seq_base

```

```

class seq_exercise_dma extends usb_seq_base;

`uvm_object_utils(seq_exercise_dma)

....

task body();

// Do some stimulus

endtask: body

endclass: seq_exercise_dma

```

```

class seq_suspend_resume extends usb_seq_base;

`uvm_object_utils(seq_suspend_resume)

....

task body();

// Do some stimulus

endtask: body

endclass: seq_suspend_resume

```

## Improved Simulation Efficiency

Embracing the full power of UVM can lead to simulation efficiency

## Institutionalizing the Power of UVM

- 1. Benchmark and share the data to motivate change

- 2. Automate the creation of UVM testbenches

- 3. Document a methodology

- 4. Periodic knowledge share and review of the testbench

Document a Methodology: Sequence Inheritance

```

class dut seq base extends uvm sequence #(uvm sequence item);

`uvm_object_utils(dut_seq_base)

dut env confiq m env cfq;

// Declare sequencers, sequence items, sequences, and

// register models that can be used by derived classes

// Declare commonly used functions and tasks

task body();

// Get the environment configuration object

if(!uvm_config_db #(dut_env_config)::get(null,

{"uvm_test_top.",get_full_name()},

"dut env config",

m env cfq)) begin

`uvm_fatal("body", "dut_env_config configuration object not found")

// Create transactions

spi_txn = spi_frame::type_id::create("spi_txn");

// Prepare the register model for use by the derived test sequences

dut rm = m env cfq.dut rm;

// Connect sequencer handles for each active agent in environment

if (m env cfq.m dut reset agent cfq.is active == UVM ACTIVE) begin

dut_reset_sqr = m_env_cfg.m_dut_reset_sqr;

m spi sqr = new[m env cfq.num agent spi];

for (int i=0; i<m_env_cfg.num_agent_spi; i++) begin</pre>

m spi sqr[i] = m env cfg.m spi sqr[i];

endtask: body

endclass: dut_seq_base

```

```

dut_seq_base

usb_seq_base

spi_seq_base

seq_exercise_dma

seq_suspend_resume

```

```

class usb_seq_base extends dut_seq_base;

`uum_object_utils(usb_seq_base)

// Declare USB-SPECIFIC sequencers, sequence items, sequences, and

// register models that can be used by derived classes

// Declare USB-SPECIFIC commonly used functions and tasks

task body();

// Do USB-SPECIFIC stimulus and/or create USB-SPECIFIC transactions

// for use by derived classes

endtask: body

endclass: usb_seq_base

```

# Document a Methodology: UVM Testbench Generation

```

module dut tb;

UVM Test

import uvm pkq::*;

UVM environment

import dut_test_pkg::*;

// Virtual interfacce for each agent

apb uvc if

vif apb

(clk, rst 1);

spi uvc if

vif spi

(clk, rst 1);

APB Agent

Sequencer

dut_reset_if(.clock(clk), .resetn(rst_1));

Scoreboard

-APB Interface-

wave gen if

reset_gen#(.TIME(200000), .POLARITY(0))

WaveGen Agent

i reset qen(.reset(rst 1));

Agent Config(s)

Coverage

clk qen #(.PERIOD(12500), .POLARITY(0))

i clk qen(.clk(clk));

wave_gen_if-

Confia

Monitor

Register Model

Register Model

dut my_dut(

SPI Agent

.clk (clk),

spi_uvc_if-

Sequencer

.rst_l (dut_rst_l)

Config

Environment Config

);

Confia

Monitor

assign dut rst 1 = dut reset if.InputPin & rst 1;

// Place the virtual interfaces in the uvm_config_db & execute run_test()

initial begin

uvm_config_db #(virtual wave_gen_if)::set(null, "uvm_test_top", "vif_dut_reset", dut_reset_if);

uvm_config_db #(virtual apb_uvc_if)::set( null, "uvm_test_top", "vif_apb",

vif apb);

uvm confiq db #(virtual spi uvc if)::set( null, "uvm test top", "vif spi",

vif spi);

run_test();

end

endmodule: dut tb

```

DUT

dut tb

### **UVM Test Base Class**

- 1) Create the agent configuration

- Get its virtual interface out of the uvm\_config\_db

- 3) Assign the virtual interface to the agent configuration

- 4) Further configure the agent

```

class dut_test_base extends uvm_test;

dut_env

dut_env_config

m_dut_env_cfg;

wave_gen_agent_config m_dut_reset_agent_cfg;

apb_agent_config

m_apb_agent_cfg;

spi_agent_config

m_spi_agent_cfg:

extern

function void build_phase

(uvm_phase phase);

extern virtual function void configure_dut_env(dut_env_config cfg);

endclass: dut_test_base

function void dut_test_base::build_phase(uvm_phase phase);

// Create the Environment Configuration Object

m_dut_env_cfg = dut_env_config::type_id::create("m_dut_env_cfg");

configure_dut_env(m_dut_env_cfg);

// Create and configure the Agent Configuration Objects

// Assign the Agent Configuration Objects in the Environment Configuration Object

m_spi_agent_cfg = spi_agent_config::type_id::create("m_spi_agent_cfg");

if(!uvm_config_db #(virtual spi_uvc_if)::get(this, "", "vif_spi", m_spi_agent_cfg.vif)) begin

`uvm_error("RESOURCE_ERROR", "spi_uvc_if virtual interface not found")

m_dut_env_cfg.m_spi_agent_cfg = m_spi_agent_cfg;

configure_spi_agent(m_spi_agent_cfg);

// Put the environment configuration in the uvm_config_db

uum_config_db #(dut_env_config)::set(this, "*", "dut_env_config", m_dut_env_cfg);

// Create the environment

m_env = dut_env::type_id::create("m_env", this);

endfunction: build_phase

function void dut test base::connect phase(uvm phase phase)

// Connect sequencer handles for each active agent

if (m_dut_env_cfg.m_spi_agent_cfg.is_active == UUM_ACTIVE) begin

m_dut_env_cfg.m_spi_sqr = m_env.m_spi_agent.m_sequencer;

endfunction: connect_phase

```

# Importance of the Configuration Object to

Sequences

```

class dut seq base extends uvm sequence #(uvm sequence item);

`uvm object utils(dut seq base)

dut env config m env cfg;

// Declare sequencers, sequence items, sequences, and

// register models that can be used by derived classes

// Declare commonly used functions and tasks

task body();

// Get the environment configuration object

if(!uvm confiq db #(dut env confiq)::qet(null,

{"uvm test top.",qet full name()}

"dut env confiq",

m env cfq)) begin

`uvm_fatal("body", "dut_env_config configuration object not found")

// Create transactions

spi txn = spi frame::type id::create("spi txn");

// Prepare the register model for use by the derived test sequences

dut rm = m env cfq.dut rm;

// Connect sequencer handles for each active agent in envir

nment

if (m env cfq.m dut reset agent cfq.is active == UVM ACTIVE

begin

dut_reset_sqr = m_env_cfg.m_dut_reset_sqr;

m spi sqr = new[m env cfg.num agent spi];

for (int i=0; i<m env cfq.num agent spi; i++) begin

m_spi_sqr[i] = m_env_cfg.m_spi_sqr[i];

endtask: body

endclass: dut seq base

```

Sequence retrieves sequencers from the environment configuration object

Importance of the Configuration Object to the

Environment

```

class dut env extends uvm env;

'uvm component utils(dut env)

dut env confiq m env cfq;

usb agent

m usb agent;

extern

function

(string name, uvm component parent);

extern virtual function void build phase

(uvm phase phase);

extern

function void connect phase (uvm phase phase);

endclass: dut env

function void dut env::build phase (uvm phase phase);

super.build phase(phase);

(!uvm_config_db #(dut_env_config)::get(this,"","dut_env_config", m_env_cfg)) begin

'uvm error("CONFIG DB", "dut env config not found")

if (m env cfq.has agent usb) begin

uvm confiq db #(usb agent confiq)::set( this,

"m usb agent",

"usb agent config",

m env cfq.m usb agent cfq)

m usb agent = usb agent::type id::create("m usb agent", this);

```

Environment builds components specified in the environment configuration object

endfunction: build\_phase

## Summary

- Some macros do have value (e.g. ASIC vs. FPGA)

- Use UVM to dynamically configure your environment

- The <u>virtual</u> keyword is powerful!

- The configuration object plays a critical part in configuring a UVM Environment for a particular UVM Test

- Sequence override adds even more power to UVM

- Take advantage of methods that improve simulation efficiency

- Realizing "The Full Power of UVM" requires an investment in knowledge, methodology, and infrastructure

# Questions?