#### **UNITED STATES**

SAN JOSE, CA, USA MARCH 4-7, 2024

Automated Formal Verification of a Highly-Configurable Register Generator Shuhang Zhang, Bryan Olmos, Basavaraj Naik Infineon Technologies AG, Neubiberg, Germany

# Outline

- Motivation

- Register Generator

- Verification Challenge

- Automated Formal Verification

- Results

- Conclusion

#### Motivation

- Number of registers increases

- Ensure chips work correctly

- Low complexity

- Manual implementation error-prone

# Implement numerous registers in seconds

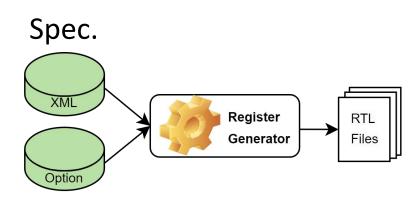

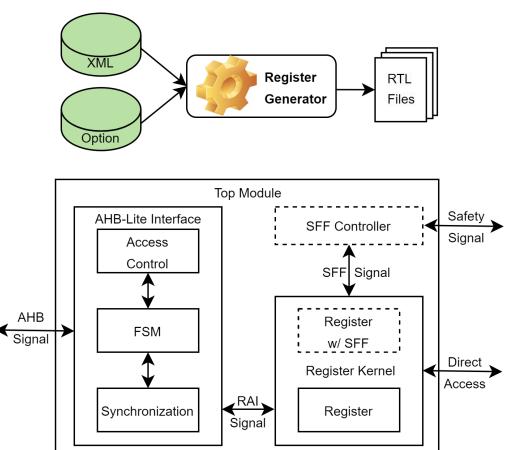

### **Register Generator**

- Bus interface and register kernel

- Optional Safety IP

. . .

- 41 options to support various features

- regAsync (async. Clock for register)

- regBusClock (register still Bus Clock)

- regUnrollAHB (unroll AHB signals)

# Verification Challenge

- Configurability

- 41 different options

- Diverse access policies

- External access via the bus interface

- Internal access via other blocks

- 20PD for one design with UVM

- Incomplete coverage

- Formal fits great

- Automated property generation

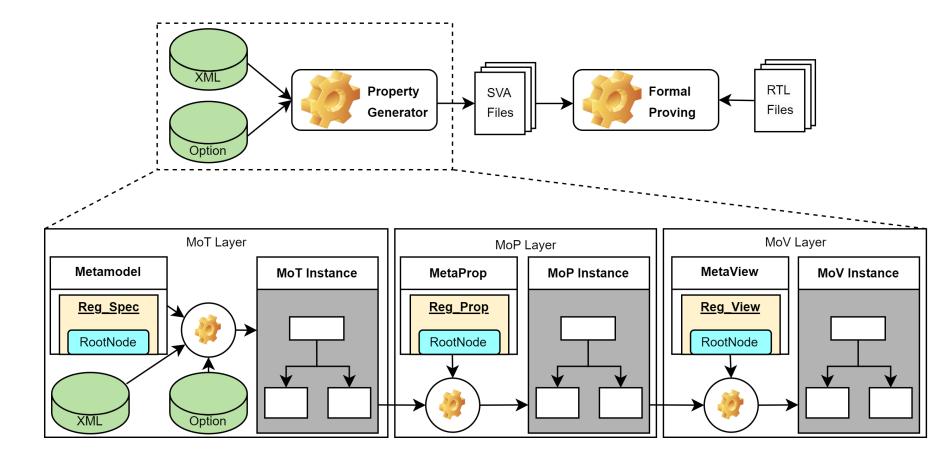

#### Automated Formal Verification

# Generation Option Analysis

- 41 generation options -> Impossible to verify all combinations

- Group generation options

- Dependent option

- regAsync

- regBusClock

- Independent option

- regUnrollAHB

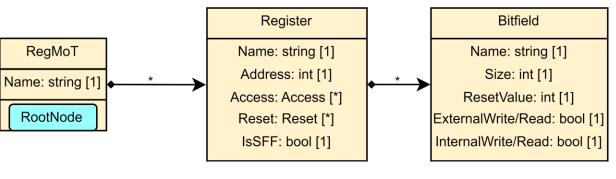

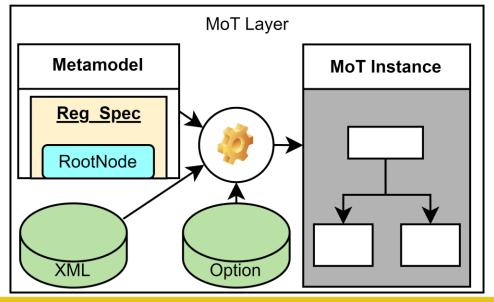

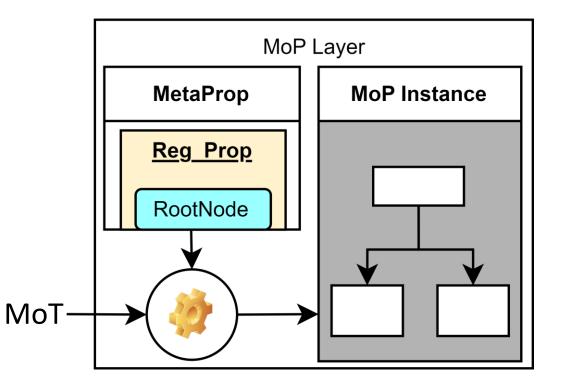

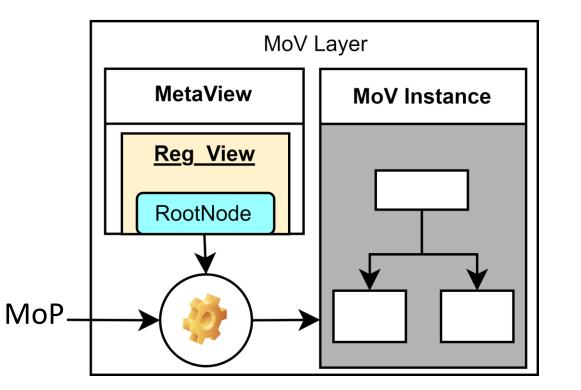

# Specification Extraction

- MetaModel creation

- Define which spec. are extracted

- Both register and bitfield level

- Model of Things (MoT)

- Internal spec.

# **Property Definition**

Property class defined using Python

- Bus protocol

- External Read/Write

- Access violations

- Internal Read/Write

- Dummy write

- Integrated Safety IP

•

### **Property Generation**

#### **External Write:**

property reg\_external\_write; @(posedge hclk\_i) disable iff(!hreset\_n\_i) ... && sx\_ahb\_lite\_slave.haddr == 32'h0000\_0002 && sx\_ahb\_lite\_slave.hwrite == 1'b1 && debug\_on\_i == 1'b1; |-> ##1 sx\_ahb\_lite\_slave.hwdata == register\_kernel\_inst.reg\_bf\_value; endproperty chk reg external write assert: assert property(reg external write);

#### **External Write Error:**

property reg\_external\_write\_error; @(posedge hclk\_i) disable iff(!hreset\_n\_i) ... && sx\_ahb\_lite\_slave.haddr == 32'h0000\_0002 && sx\_ahb\_lite\_slave.hwrite == 1'b1 && debug\_on\_i = 1'b0; |-> ##1 sx\_ahb\_lite\_slave.hreadyout\_o == 1'b1 && sx\_ahb\_lite\_slave.hresp\_o == 1'b0; endproperty

chk\_reg\_external\_write\_error\_assert: assert property(reg\_external\_write\_error);

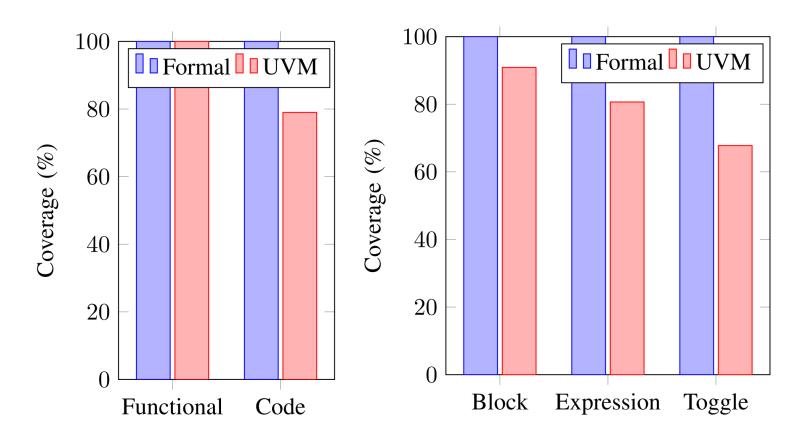

# Results: Effort and Coverage

- Flow applied on a productive project

- Effort reduction

- ~3PD Formal

- One-time 80PD

- ~20PD UVM

- Better coverage

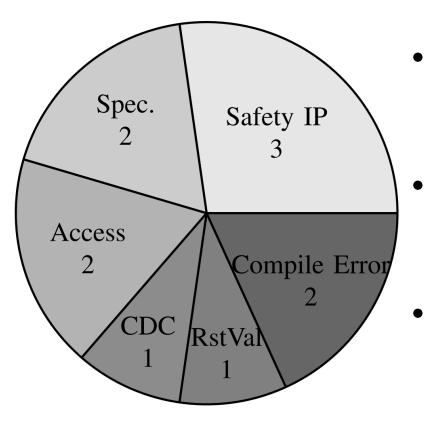

### Results: Detected Bugs

Safety IP – Connectivity issues

Access

Spec.Documented wrongly

**Protection issues**

- CDC

CDC check failure

- RstVal

Wrong reset value

- Compiling Error

#### Conclusion

- Great challenges brought by our in-house register generator

- Traditional UVM approach time-consuming

- Automated formal verification is more efficient

#### Questions?

# Thank you!