## **User Experiences with the Portable Stimulus Standard**

Tom Fitzpatrick, PSWG Vice Chair Prabhat Gupta, AMD Mike Chin, Intel

## **The Biggest Change**

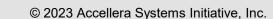

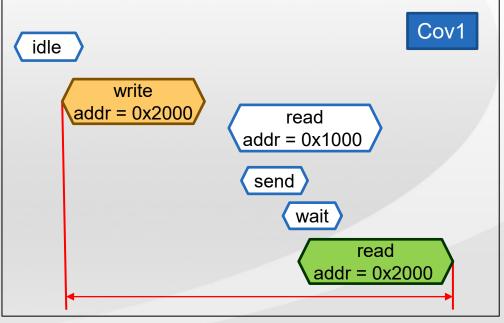

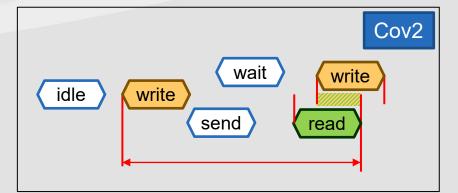

## Introducing Behavioral Coverage (WIP)

- Given a stream of action executions, find out whether a given temporal scenario (query) occurs in this stream

- The cover statement specifies the interesting scenario

- A monitor encapsulates behaviors to be covered

- A monitor may be implicit (in a cover statement) or explicit

## **Behavioral Coverage Tracking**

- Action traversal (e.g., do A with x == 5):

- Match nearest action execution matching imposed constraints

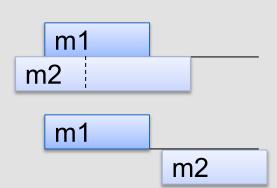

### Concatenation: concat { m1; m2 }

- Match first m2 after m1

- Match m1 from the current point; from every match point of m1 match m2

### Eventually: eventually m

- Some time in the future

- Match m from everywhere, starting from the current point

### Sequence: sequence { m1; m2 } or { m1; m2 }

- Match m2 after m1, not necessarily immediately

- Match m1 from the current point; starting from the match of m1 match m2 from every point

- Equivalent to concat { m1; eventually m2 }

- Overlaps: {m1 overlaps m2}

- Match m1 if m2 executes at any point while m1 is executing

- Select: select { m1; m2 }

- Match either m1 or m2

m

## **Solve/Runtime Messaging**

### New addition to the Core Library

```

- Solve time

solve function void print foo(my struct s) {

print("The context of the struct is:\n");

- format

print("value = %d\nname = '%s'\n", s.value, s.name);

- print

solve function string get foo context string (my struct s) {

return format("value = %d\nname = '%s'\n", s.value, s.name);

- Runtime

exec body {

y = my func();

- message

message(FULL, "The values of the variables x and y are: ");

message(LOW, "%d, %d", x, y);

- Either

package io pkg { // may change to std pkg or ...

- error/fatal

function void error(string format, type... args);

function void fatal( int status, string format, type... args);

returned to calling

environment

```

## **Solve/Runtime Messaging**

### Solve-Time File I/O

- Via file handles

package io\_pkg {

typedef chandle file\_handle\_t;

static const file\_handle\_t nullhandle = /\* implementation-specific \*/;

enum file\_option\_e {TRUNCATE, APPEND, READ};

function file\_handle\_t file\_open(string filename, file\_option\_e opt = TRUNCATE);

function void file\_close(file\_handle\_t file\_handle);

function bool file\_exists(string filename);

function void file\_write(file\_handle\_t file\_handle, string format, type... args);

function string file\_read(file\_handle\_t file\_handle, int size = -1);

- Single Functions

## List randomization

- Lists can now be declared rand

- Randomized when its container is randomized

- Just like other rand fields

- The size is considered a state variable

- *size* cannot be constrained directly

```

struct S {

rand list<bit[8]> lst;

exec pre_solve { // Initialize the list

repeat (100) {

lst.push_back(0);

}

}

constraint {lst.size() in [4..100]; // Error: illegal constraint on size

foreach (lst[i]) {

lst[i] == i+lst.size(); // OK: size is a state variable in foreach

}

}

}

```

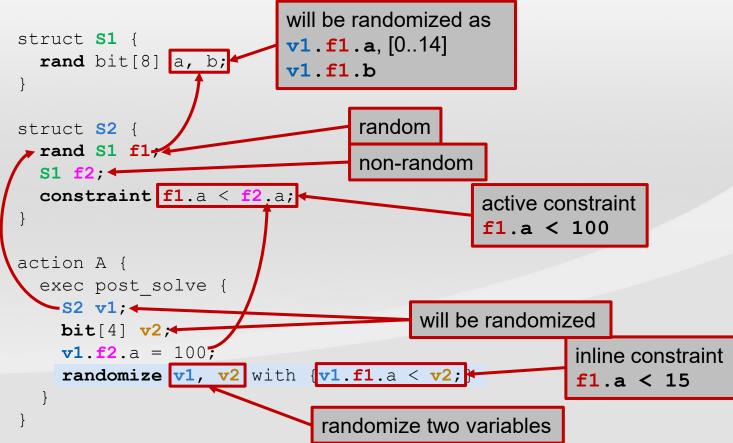

## **Procedural randomization statement**

- Allowed in solve exec blocks

- Subset allowed in target exec

- No struct randomization

- Also supports

- urandom

- urandom\_range

## **Dist randomization constraint**

### Similar to SystemVerilog

- := assigns a specific weight

- : / distributes weight across a list

- Subject to other constraints

- dist only biases values in the legal range

| struct S {      |                              |            |

|-----------------|------------------------------|------------|

| rand bit[32]    | x;                           |            |

| bit             | У;                           |            |

| constraint dist | x in [100102 := 1, 200 := 2, | 300 := 5]; |

|                 | 100:1, 101:1, 102:1, 200:2,  | 300:5      |

constraint dist x in [100..102 :/ 1, 200 := 2, 300 := 5];

|            |        |      | 100:1/3<br>101:1/3,<br>102:1/3 |       | 200: <b>2</b> , |                  | 30  | 300 <b>:5</b> |  |

|------------|--------|------|--------------------------------|-------|-----------------|------------------|-----|---------------|--|

| constraint | dist x | in [ | 100102                         | := 1, | 200             | := 2,            | 300 | <b>:</b> = 5] |  |

| constraint | (y==1) | -> x | x > 300; <b>↓</b>              |       |                 | strain<br>e igno |     | es dis        |  |

DESIGN AND VERI

NITED STA

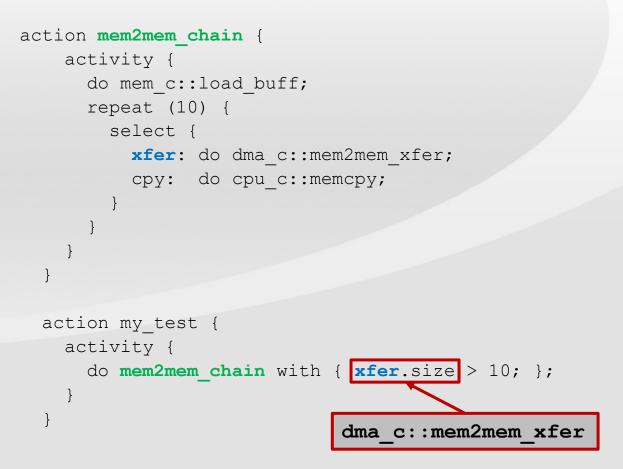

## Labels as action handles

## Labels as action handles

- Create handle for anonymous action traversal

- Can be referenced from above

DESIGN AND VERIFICATION

SYSTEMS INITIATIVE

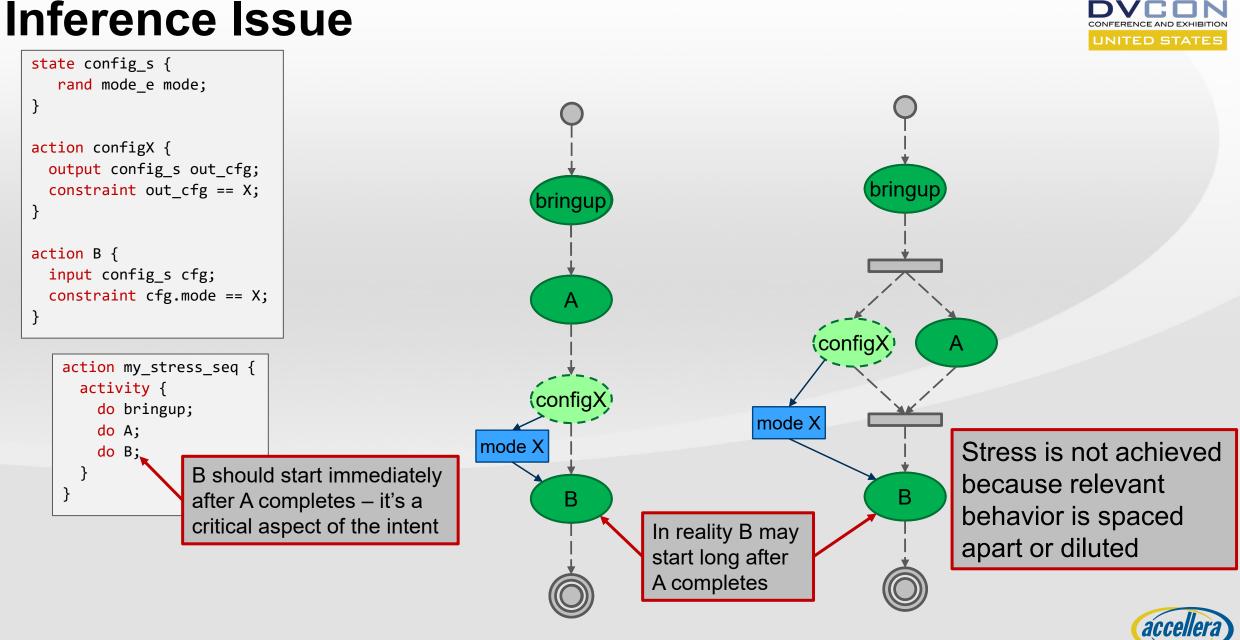

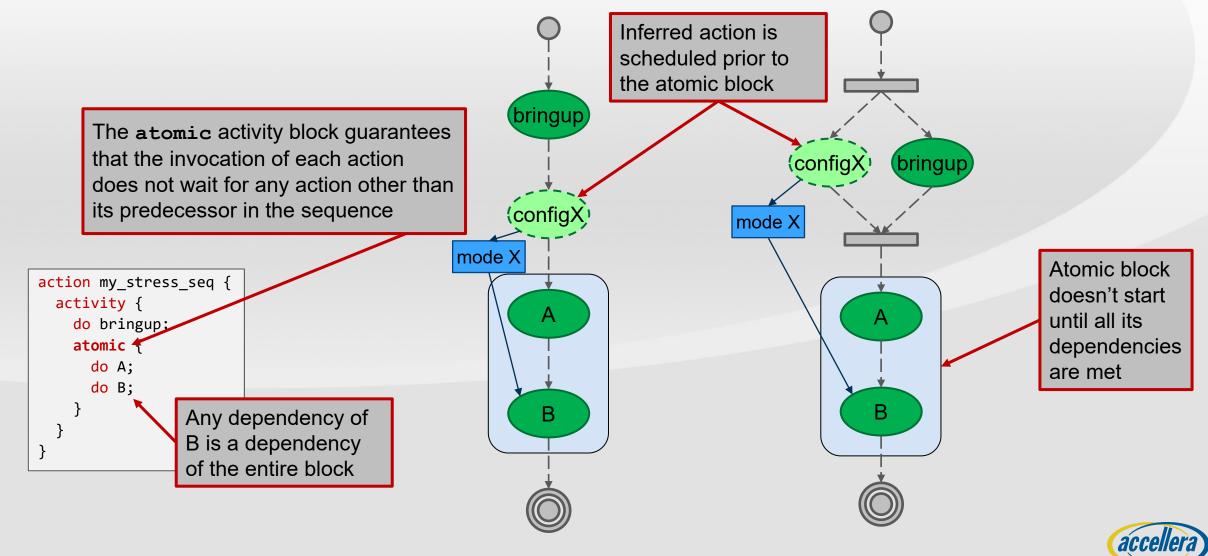

## **Inference For "Atomic" Block**

SYSTEMS INITIATIVE

## **Concise read-modify-write**

### Added a way to read-modify-write in a single operation

```

pure component reg_c < type R,

reg_access ACC = READWRITE,

int SZ = (8*sizeof_s<R>::nbytes)> {

function R read();

```

```

function void write(R r);

```

```

function bit[SZ] read_val();

```

```

function void write_val(bit[SZ] r);

```

```

struct CR : packed_s<> {

bit en;

bit[11] pad;

bit[4] mode;

bit[16] coeff;

}

```

```

component dut_c {

dut_regs_c regs;

```

```

action cfg_a {

rand bit[4] mode;

rand bit[16] coeff;

exec body {

comp.regs.cr.write_masked(

{.mode=~0, .coeff=~0}, {.mode=mode, .coeff=coeff});

```

## **Additional New Features**

### Static functions in components

- Function declaration associated with the component type (not instance)

- Called via the "::" scope operator

- Tag/Addr\_value

- Enum base type

- Floating Point computation and storage types

### UNITED STATES

## **AI Engine Subsystem Verification With PSS**

AMD together we advance\_

Prabhat Gupta - AMD

SYSTEMS INITIATIVE

## Agenda

### Introduction

- PSS initial approach tackle portability

- First-class PSS model

- Constraints

- PSS Methodology

- Conclusion

## Introduction

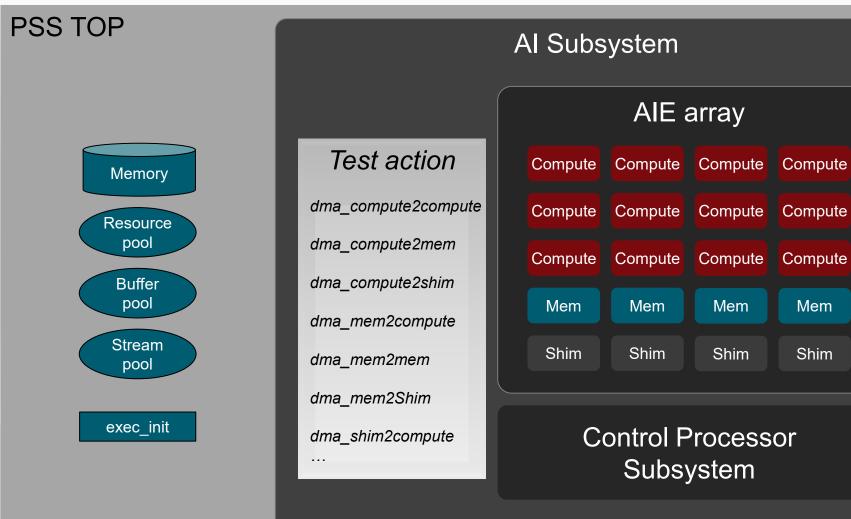

### Verification of a grid of general-purpose AI Engines

AI Engine information is available at https://www.xilinx.com/products/technology/ai-engine.html

### Example use cases of AI Engine array

- Auto framing and eye gaze correction with Microsoft Teams

- Low power background blur, audio noise reduction, etc.

- Highly configurable network fabric

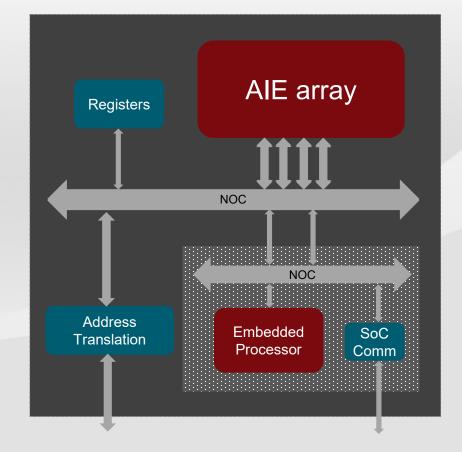

- Compute, Memory, and Shim engines

- Connected to SoC with a high-speed on-chip data network and pervasive control network

- Grid of engines and highly configurable network makes creating functional, performance, and post-silicon validation tests very challenging

Control Processor Subsystem

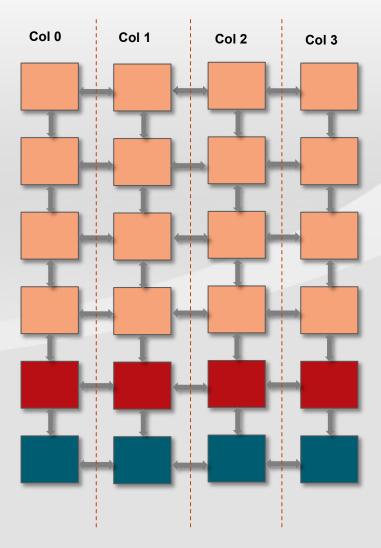

## **Circuit-switched DMA**

- More than one channel going east-west or north-south

- Multi-hop acyclic paths for DMAs

- Adjacent columns can be isolated as a group

- DMAs can't cross the isolation boundary

applications

- Host processor sends work to embedded processor

- Embedded processor sends compute kernels to AIE array

## Al sub-system

- AI Array with embedded control processor

- Al array can be subdivided for isolated parallel work from different

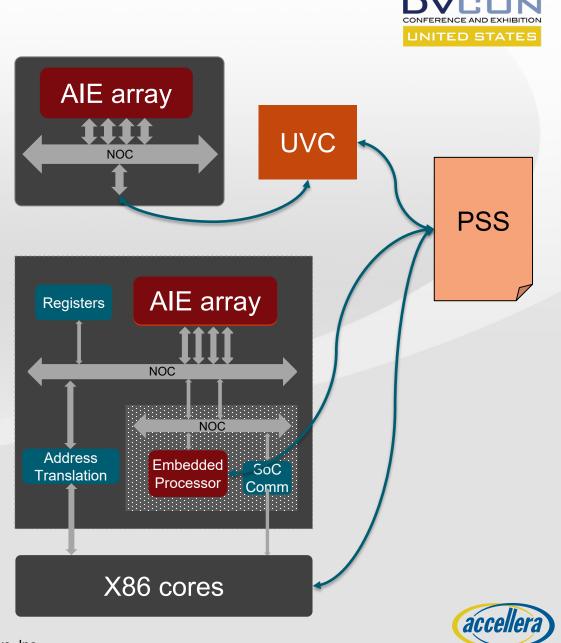

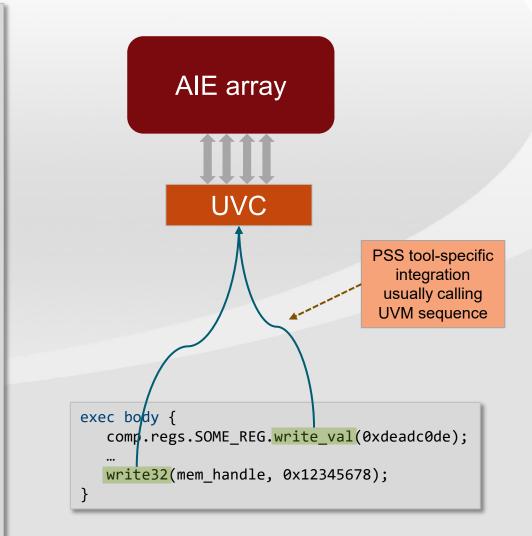

# **Testbench environments**

### IP only

- AIE array UVM/C++ environment

### Subsystem

AIE array with an embedded processor running C code with UVM/C++ environment

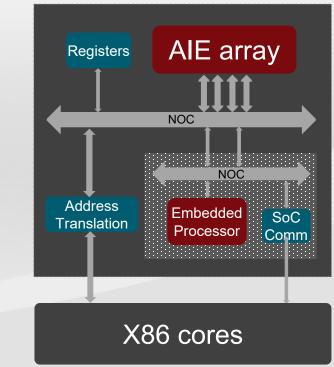

## Full SoC

- X86 processors, AIE subsystem, and rest of chip

- C code running on x86 and embedded processor

- Post-silicon bring-up and validation

- C code running on the main and embedded processor

DESIGN AND VERIF

SYSTEMS INITIATIV

# **Verification Challenges**

#### 2023 DESIGN AND VERIFICATION DVCDN CONFERENCE AND EXHIBITION UNITED STATES

### AIE Array

- Many possible paths through the AI engine array

- Compute array can be configured into different partitions, which impacts routing

- Need to exercise many combinations to verify routing/arbitration throughput/latency

- Legal pseudo-random paths for routing

- Challenging to account for possible parallel DMAs without a lot of procedural code in a complex test

- Lots of boilerplate code for new tests

### Subsystem

- Need to verify new interfaces

- Most tests in UVM, take advantage of randomization/coverage with the embedded processor in bypass

- A lot of boilerplate code for each test

- Some bare-metal content for the embedded processor, but it's a huge barrier, not usually done

## SoC

- Need bare-metal test content, but only have UVM content

- Must develop multi-core tests to exercise key cases  $\rightarrow$  multicore is always a challenge

- Synchronization across AIE and other IP are challenging

# The value – portability **PSS FIRST STEPS**

© 2023 Accellera Systems Initiative, Inc.

# An AIE Test

- Power up and bring the AIE array out of the reset with the UVM testbench

- Boot AIE array

- Initialization sequence in PSS

### Configure AIE array isolation with PSS

- Adjacent columns isolated to work on different applications

- Find a valid random isolation setup, that could be user-supplied, and do isolation programming

### Configure acyclic circuit-switched DMA circuits with PSS

- Find N random valid circuits across all isolation units, program the circuits

### Generate traffic

- Run M parallel DMAs and check the results

- Select valid routes from the last step

- Repeat with new isolation setup

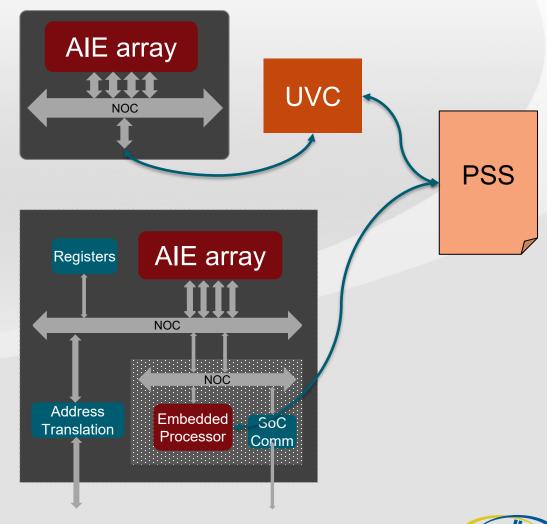

# **PSS first steps for AIE project**

### UVM to PSS – started at IP level

- Mostly procedural code converted from UVM to PSS

- Fixed column isolation setup and DMA circuits

- PSS address spaces and registers

### Portability to the embedded control processor (CP)

- Address space adapted to CP address map and TLBs

### Value

- NOC randomization

- New tests running on the control processor

- Test available for post-silicon bring up

How does the PSS portability work?

# **PSS MODEL INTEGRATION**

© 2023 Accellera Systems Initiative, Inc.

# **AIE IP PSS Integration**

```

exec init_down {

```

```

// Add PSS executors to map to UVCs

// May have some tool-specific setup for integration

// Call to add_executor

```

```

// Memory setup

repeat(col: COMPUTE_TILE_COLS) {

repeat (row: COMPUTE_TILE_ROWS) {

transparent_addr_region_s<aie_mem_trait_s> tile_region;

```

```

aie_tile_region.size = COMPUTE_MEM_SIZE;

aie_tile_region.addr = compute_tile_base(row, col);

```

```

aie_tile_region.trait.mem_block = COMPUTE_TILE;

aie_tile_region.trait.row = row + COMPUTE_TILE_START_ROW;

aie_tile_region.trait.col = col;

```

```

(void)mem.add_region(tile_region);

};

```

```

transparent_addr_region_s<mem_trait_s> sysmem_region;

(void)sysmem.add_region(sysmem_region);

```

DESIGN AND VERIFICATION

INITED STATE

. . .

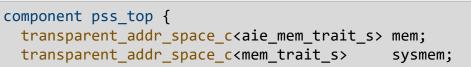

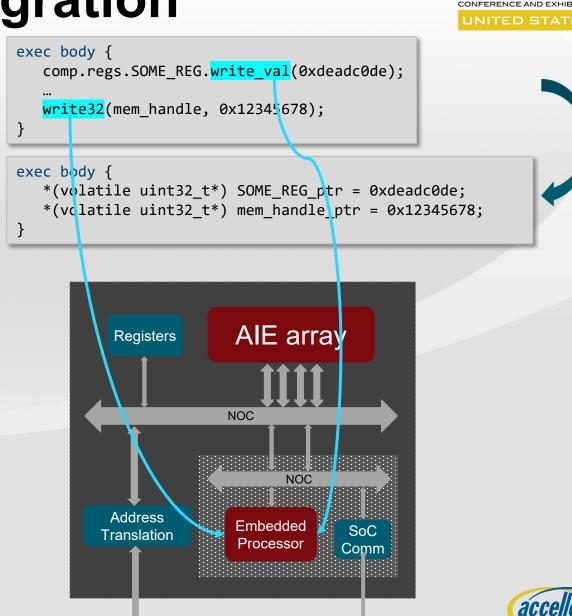

# **AIE Subsystem PSS integration**

SYSTEMS INITIATIV

component pss top { transparent addr space c<aie mem trait s> mem; transparent addr space c<mem trait s> sysmem; exec init down { // Add PSS executors to map to Embedded Processor // May have some tool-specific setup for integration // Call to add executor . . . // Memory setup repeat(col: COMPUTE TILE COLS) { repeat (row: COMPUTE\_TILE\_ROWS) { transparent addr region s<mem trait s> tile region; aie tile region.size = COMPUTE MEM SIZE; aie\_tile\_region.addr = TLB(compute\_tile base(row, col)); aie tile region.trait.mem block = COMPUTE TILE; aie tile region.trait.row = row + COMPUTE TILE START ROW; aie tile region.trait.col = col; (void)mem.add region(tile region); }; }; transparent addr region s<mem trait s> sysmem region; (void)sysmem.add region(sysmem region);

## Two test compilation units

- One embedded processor and a few x86 processors

**SoC PSS integration**

Tool-specific setup to generate test code for x86 and embedded control processor

### PSS action synchronization across executors

- Tool-specific implementation, usually memory-based mailboxes

### PSS Memory setup

Multiple executors

- Shared system memory

- Local AIE memories

## How it should be FIRST-CLASS PSS MODEL

## **Desired PSS model capabilities/example tests**

## **PSS model capabilities**

Setup random isolation groups

Setup multiple acyclic circuits in an isolation group

Multiple parallel DMAs with data checks Enable inference for simple test writer interface A simple PSS Test API that allows random and directed tests

```

action aie_dma_one_group {

activity {

do setup_isolation with {

out_iso_state.num_iso_groups == 1;

}

parallel {

replicate (N) { do aie_c::dma; }

};

};

};

```

### Example tests

N parallel DMAs with random circuits in a random isolation setup

N parallel DMAs with random circuits in an isolation setup with all columns as one group

Maximum parallel DMAs to system memory Validate every point-to-point path in the AIE grid

```

action aie_dma {

```

```

activity {

parallel {

replicate (N) { do aie_c::dma; }

};

};

```

};

## **PSS model**

© 2023 Accellera Systems Initiative, Inc.

## **PSS model**

{

pool [NO\_DMA] dma\_chan\_s chan\_pool;

action configure\_isolation {}

action configure\_switch {}

action stream\_to\_mem {}

action mem\_to\_stream {}

}

component aie tile <int NO DMA,int NO BD>

Abstract base actions in separate files. Allows project-specific action implementation while keeping high-level tests the same

Translation translation;

```

component tile_addr_translation_c {

target function bit[64] translate(

addr_handle_t hndl,

bit[64] base_address)

{

bit[64] addr;

return (addr);

}

}

```

Translation translation;

```

component shim_tile< int NO_DMA, int NO_BD >

: aie_tile<NO_DMA, NO_BD>

{}

```

# **Test composition**

SYSTEMS INITIATIVE

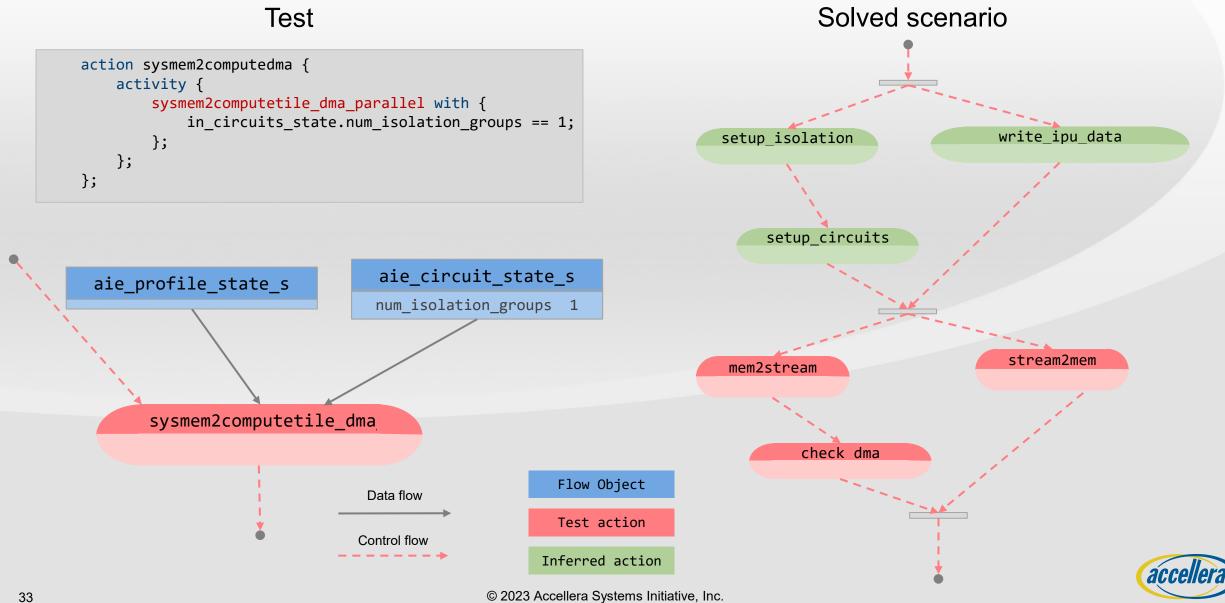

## Test API design process dma\_compute2compute

### State object to store current circuit state

- Max size circuits array in state object

- Most rules about circuits encapsulated in state object

### First try

- Action input current circuit state and output updated circuit state with new circuits

### Problem

- Huge constraint space for doing two DMAs in series

- Sparse solution space with constraints on input and output state objects

```

action two_dma {

activity {

do dma_compute2compute_parallel;

do dma_compute2compute_parallel;

}

```

```

action dma_compute2compute_parallel {

```

```

input circuit_state_s circuits_in;

output circuit_state_s circuits_out;

```

```

// constraint rules to create output circuit state

// from the input circuit state

// ...

```

```

rand array<circuit_node_s, MAX_CIRCUITS> src;

rand array<circuit_node_s, MAX_CIRCUITS> dst;

```

rand int in [1..MAX\_CIRCUITS] parallel\_count;

```

activity {

parallel {

replicate(i: parallel_count) {

do compute_tile::mem_to_stream with {node == src[i];}

do compute_tile::stream_to_mem with {node == dst[i];}

}

}

}

```

## Test API design process dma\_compute2compute

### State object to store current circuit state

- Max circuits array

### Preferred solution

- Constraints for isolation and circuits in the state object

- DMA actions have an input state object but no output state

## Tip

- A generic DMA action, that inputs the current state manipulates it, and then outputs it, is not always a good solution for high-level test space modeling with PSS

- This generic action is very procedural that unnecessarily adds to constraint-solving complexity

- Be cognizant of PSS global constraint-solving semantics

```

action dma compute2compute parallel {

input circuit state s circuits in; // Only INPUT

rand array<circuit node s, MAX CIRCUITS> src;

rand array<circuit node s, MAX CIRCUITS> dst;

rand int in [1..MAX CIRCUITS] parallel count;

activity {

parallel {

replicate(i: parallel count) {

do compute tile::mem to stream with {node == src[i];}

do compute tile::stream to mem with {node == dst[i];}

```

DESIGN AND VERIFI

# Test API – building block actions

### Test API design

- Constraint space and usability concerns affect the Test API design most

- Quick iterations on API design is highly desirable

### Three levels of test API – building block actions

- Level 1

- Fully encapsulated sub-IP or IP model with registers, initialization, and programming sequences

- E.g., compute, mem, and shim tile PSS components with mem\_to\_stream and stream\_to\_mem actions

- Not directly used to create tests

- Level 2

- Main test writers' interface

- For example, sysmem2computetile\_dma\_parallel action from AIE component

- Level 3

- Simplified high-level test interface used by the architect, SoC DV, and post-silicon

- DMA action to do DMA from a given tile to another tile

They are powerful and dangerous **CONSTRAINTS**

© 2023 Accellera Systems Initiative, Inc.

## **Constraint efficiency**

#### Constraints are the backbone of the PSS model

- Allows for action inference, flow object binding inference, describe state and resource rules

### PSS models formulate a global constraint-solving problem

- Local randomization in PSS 2.1 should contain the constraint-solving problem for data-only randomization

- Efficient constraints are extremely important for PSS models

### TIPS

- Only expose important attributes of test space as rand for test space exploration

- E.g., random DMA channel allocation is important as a model attribute but not so much the data for DMA

- Explicitly restrict the domain of a random attribute

- E.g., DMA channel number shouldn't be 'rand int' but 'rand int in [0..MAX\_DMA-1]'

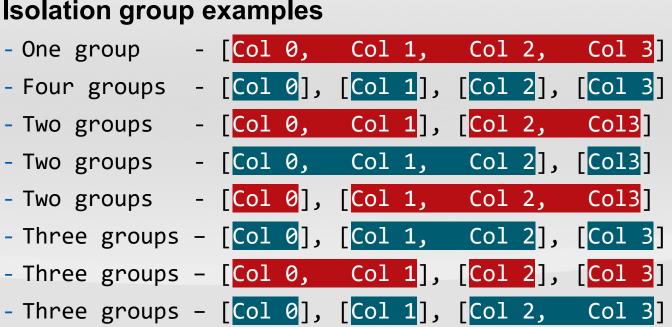

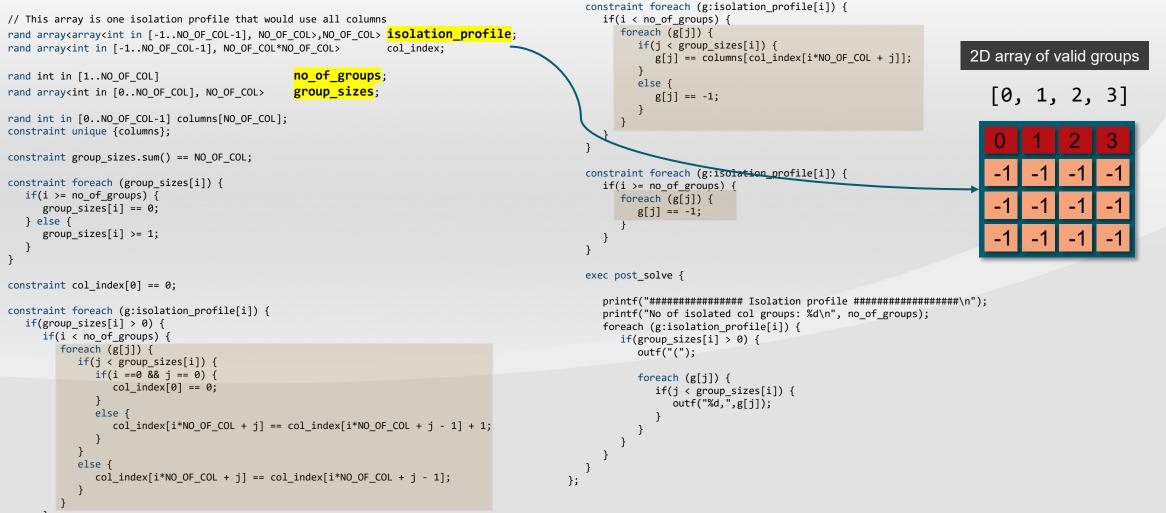

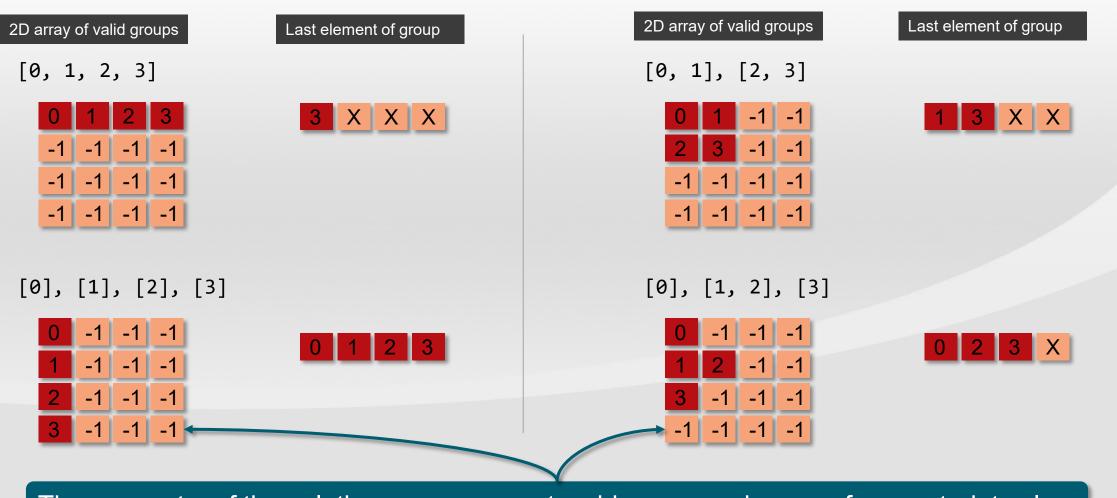

## **Constraint efficiency – example problem**

- Group adjacent columns as an isolation group

- Problem create random legal isolation groups

- Isolation group examples

- One group

- Four groups

- Two groups

- Two groups

- Two groups

- Three groups -

- Three groups -

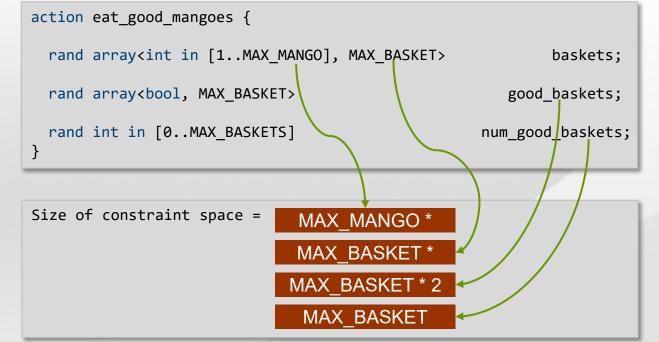

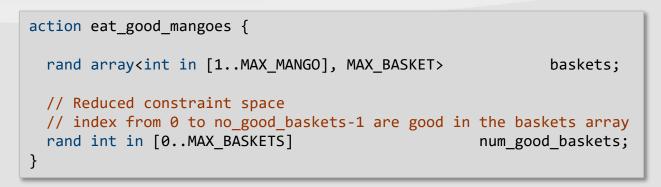

## **Constraint search space**

- Get N good mango baskets from M baskets

- Which basket is bad is not important

- Constraint solver needs to find values of all rand attributes that satisfy the constraints

- The possibility space of the cross of rand attributes domain size is the constraint space

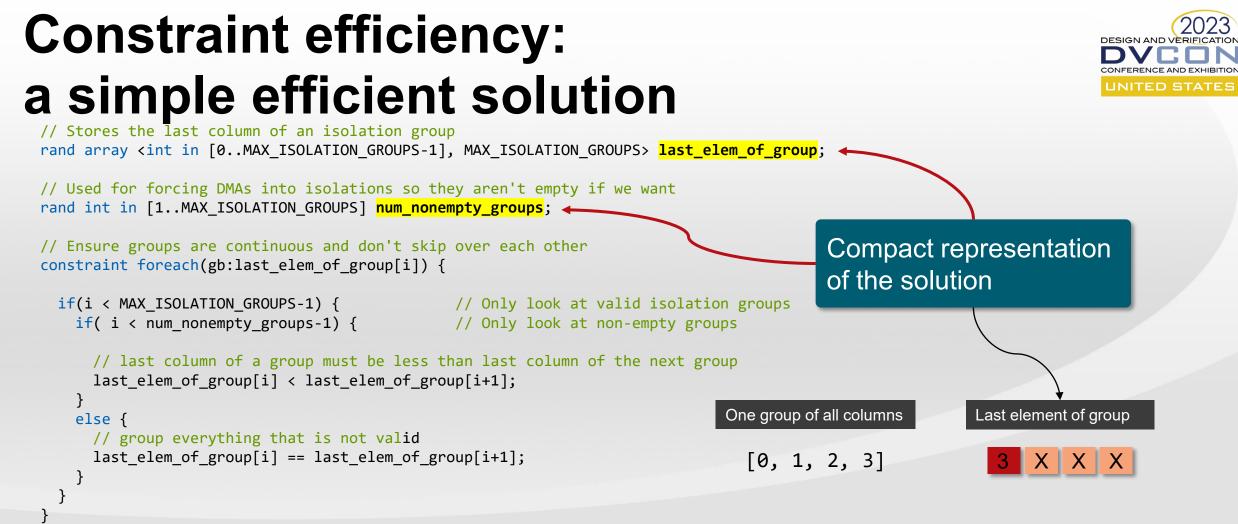

## Constraint efficiency – a complex solution

action setup\_isolation {

}

// Last element of the last isolation group must be the last column

constraint last\_elem\_of\_group[MAX\_ISOLATION\_GROUPS-1] == MAX\_ISOLATION\_GROUPS-1;

## **Constraint space comparison**

The symmetry of the solution space presents a bigger search space for constraint solver

## **Constraint - conclusion**

#### Design symmetry-free solution space when possible

- Only one possible representation of the solution in the constraint model

### Minimize action inference for test writer interface actions

- If a compound action always causes inference of another action, add that action explicitly

### • Use explicit binds where possible

- Usually, a constraint solver is used for the possible binding of inputs and output

- Explicit binding reduce constraint complexity

### Avoid chaining of complex constraints from input to output

- For example, avoid, constraining all output flow object fields except a few equal to input flow object fields

#### Design PSS model to only expose important random attributes to the next integration level

- A poorly designed constraint model could easily overwhelm current and future constraint solvers

- Only allow free random attributes at system-level that are important for system-level tests

# A language can only do so much **PSS METHODOLOGY**

© 2023 Accellera Systems Initiative, Inc.

## **PSS methodology - call to action**

- Create industry-wide PSS methodology library like UVM

- Common types to facilitate smooth multi-IP and third-party integration

- Support virtualization and address translation to work across IPs including third part IPs

- Create high-level open action libraries for the standard protocols that work across vendors

- PCIe, CXL, UCIe, etc.

- Create a forum for community-maintained design patterns

- For example, Power state transitions with interleaved traffic

#### Publish best practice guidelines

- Constraint modeling

- Code structuring

#### Improve PSS action export methodology for use in the production firmware

## **PSS deployment strategies**

#### Start small and provide immediate value

- Refactor initial design to create a first-class PSS model

### Starting a PSS project at any integration level is good

- SoC with processors

- It's difficult to create random, multi-IP tests manually in C for the processors

- Use PSS for random, multi-engine functional, stress, and power tests

- Sub-system UVM and/or SystemC

- New tests can be created quickly. Reduced boilerplate for tests

- Scenario randomization as compared to data randomization

- Focus on describing system rules and encapsulated functionality then use PSS automation to create new tests

- IP

- PSS allows better reasoning of resource modeling and config space for an IP (see DVCON US 2022 presentation)

- PSS-based portable programming sequences help your friends at SoC and post-silicon (if they are friends)

## Conclusion

#### Reduced test development costs with portability

- IP programming sequence can be used in post-silicon bring-up, validation, and manufacturing tests

- PSS enables the rapid creation of complex tests that identify functional, power, performance, and firmware bugs in heterogeneous multi-processor systems through randomized, multi-IP testing

- PSS improves communication among Architecture, Firmware, DV, and Post-silicon teams through formal high-level language, leading to fewer bugs

- Describe and share SoC configuration, Inter-IP initialization, and power sequencing at high-level

- The PSS language allows for effective communication through its semantics and constructs, serving as an executable specification

#### Better post-silicon bring-up and validation

- Generate a range of tests, from simple to complex, in thousands, for effective bring-up, validation, and optimization

- Collect generation-time and runtime reports to demonstrate and analyze coverage

#### Creating new tests is fun with PSS

- Reduced friction for creating new tests, especially multi-IP tests

- Understanding every detail of SoC is not required with PSS partial scenario specification

- Improved productivity is personally satisfying for engineers

**Q & A**

### Approaches and Challenges to Scalable Modeling DVCon 2023

Mike Chin, Principal Engineer, Intel Corporation (michael.a.chin@intel.com)

## **Motivation/Need for Portable Stimulus**

#### Lower ramp up cost for new validation engineers

- Simplify content creation

- Hide complexity realization layer

- Drive efficient productivity!

### Grow expertise from "user" to "power user"

- User verification engineer

- Power users model developers, backend developers, debuggers

### Correct by construction validation content

- Drive accurate modeling to ensure test content correctness through implicit actions

Portable Stimulus has the promise to accelerate verification through ease of creation and accuracy of verification content!

Testbench/

Realization

Layer

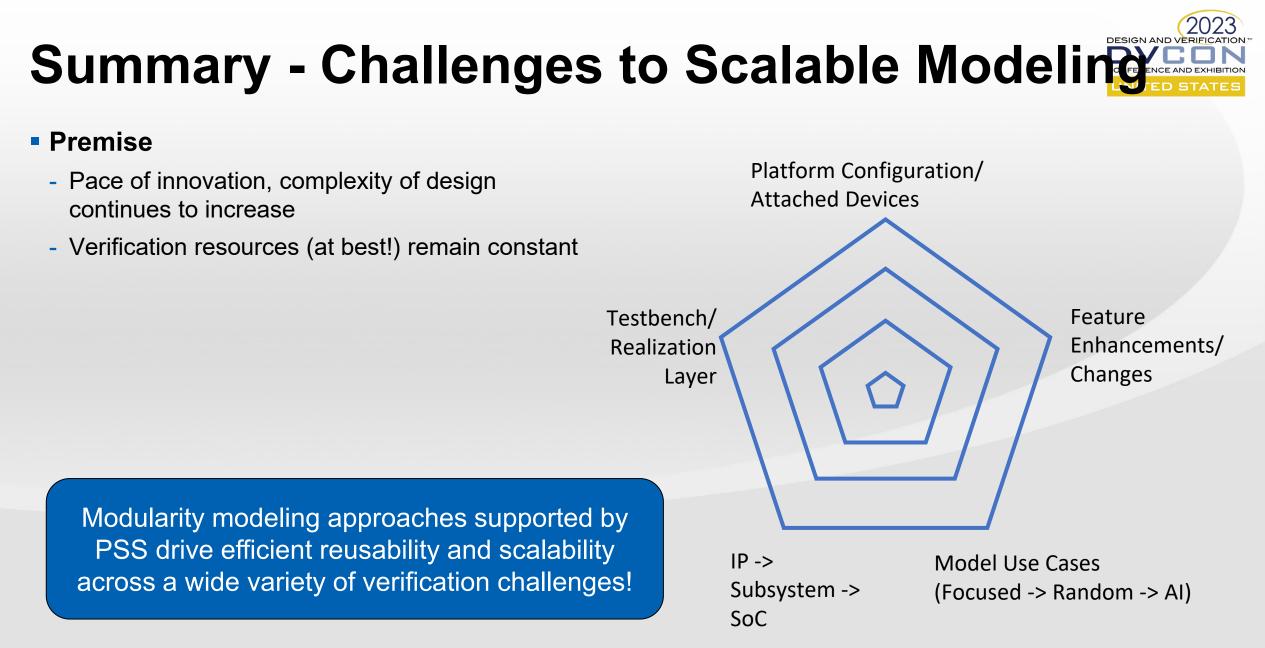

## **Challenges to Scalable Modeling** - Premise

- Pace of innovation, complexity of design continues to increase

- Verification resources (at best!) remain constant

- How do we effectively validate across the continuum?

How do we comprehend this problem? What methodologies can we use to maximize development ROI?

Feature Enhancements/ Changes

IP -> Subsystem -> SoC

Platform Configuration/

Attached Devices

Model Use Cases (Focused -> Random -> AI)

## **Our Modeling Problem**

### Simple state machine IP

- States:

- On

- Ready

- Off

- Actions:

- PowerUp

- PowerDown

- Initialize

- Read

- Support 2 independent FSM instances

How do we create scalability in our model? How do we deal with the same model executing on different platforms? Enhancements for a new project?

| T  | L package dvcon2023 {             |            |                               |

|----|-----------------------------------|------------|-------------------------------|

| 2  | 2 enum fsm_state { On, Off, Read  | ly };      |                               |

| 3  | 3 state state_t {                 |            | UNITED STATES                 |

| 4  | fsm_state cacheState;             |            |                               |

| 5  | 5    };                           |            |                               |

| 6  | 5                                 |            |                               |

| 7  | 7 component BasicIP {             |            |                               |

| 8  | <pre>pool state_t fsmState;</pre> |            |                               |

| 9  | e action PowerUp {                |            |                               |

| 10 | ) output state_t outState;        | constraint | <pre>outState == On;</pre>    |

| 11 | L };                              |            |                               |

| 12 | 2 action PowerDown {              |            |                               |

| 13 | 3 input state_t inState;          | constraint | <pre>inState == Ready;</pre>  |

| 14 | a output state_t outState;        | constraint | <pre>outState == Off;</pre>   |

| 15 | 5    };                           |            |                               |

| 16 | action Initialize {               |            |                               |

| 17 | <pre>input state_t inState;</pre> | constraint | inState == On;                |

| 18 | B output state_t outState;        | constraint | <pre>outState == Ready;</pre> |

| 19 | <pre> 9 }; </pre>                 |            |                               |

| 20 | ) action Read {                   |            |                               |

| 21 | l input state_t inState;          | constraint | <pre>inState == Ready;</pre>  |

| 23 | B output state_t outState;        | constraint | <pre>outState == Ready;</pre> |

| 24 | 1 };                              |            |                               |

| 25 | 5    };                           |            |                               |

| 26 | 5 };                              |            | <i>Cáccellera</i>             |

()))

SYSTEMS INITIATIVE

© 2023 Accellera Systems Initiative, Inc.

## Extend vs. Override in modeling logic

### "Base" model

- Reusable, core modeling logic consisting of:

- Actions

- Buffers, Streams, States

- Resources, pools

- Scalable models address different execution platforms, model configurations, and use cases

- A scalable realization layer is challenging to implement

### How do we build reusability and scalability into our models?

- Use SW best practices!

- Extend models

- Support new capabilities through "extend" language syntax

- Override settings

- Constrain model settings to reflect project/configuration values

## Extend

- Use to support capabilities not present in the base model

- Optional features/New enhancements

- Platform-specific configuration support

- SoC/Subsystem integration

- Support for new logic capabilities

- Actions

- Enum/struct members

- Resources

| 1  | package dvcon2023 {               |            |                               |

|----|-----------------------------------|------------|-------------------------------|

| 2  | extend enum fsm_state [ Busy      | ];         |                               |

| 3  | extend component BasicIP {        |            |                               |

| 4  | action Write {                    |            |                               |

| 5  | <pre>input state_t inState;</pre> | constraint | <pre>inState == Ready;</pre>  |

| 6  | output state_t outState;          | constraint | <pre>outState == Busy;</pre>  |

| 7  | };                                |            |                               |

| 8  | action PollCompletion {           |            |                               |

| 9  | <pre>input state_t inState;</pre> | constraint | inState == Busy;              |

| 10 | output state_t outState;          | constraint | <pre>outState == Ready;</pre> |

| 11 | };                                |            |                               |

| 12 | };                                |            |                               |

| 13 | };                                |            |                               |

## Override

- Configurable parameters in the base model that are overridden per project/configuration

- Number of subdevice instances

- Agent count

- Target types

- Additional constraints to specify component variable value ranges or specific values

- Base models must be written to be configurable!

- // Platform 1 (Post-si)

- 1 package dvcon2023 {

- 2 extend component BasicIP

- 3 function IPPowerDown();

- 4 };

- 5 extend action BasicIP::PowerDown {

- 6 exec body { comp.IPPowerDown(); }

- 7 };

- 8 };

- // Platform 2 (Pre-si testbench)

- 1 package dvcon2023 {

- 2 extend component BasicIP {

- 3 function SidebandShutOffClocks();

- 4 function SidebandVerifyControllerPowerState();

- 5 action PreSiPowerDown : PowerDown {

exec body {

comp.SidebandShutOffClocks();

super;

- comp.SidebandVerifyControllerPowerState();

- 11 };

6

8

9

10

DESIGN AND VERIFIC

TED STAT

© 2023 Accellera Systems Initiative, Inc.

## Challenges to Extend vs. Override

### Realization Layers

- Scalable support for all permutations:

- Model scope (IP -> Subsystem -> SoC)

- Platforms

- Devices

- Traffic generators

- Use cases (focused tests, randomization, AI)

- Extend/Override mechanisms need to be carefully managed!

### Base vs. Extend vs. Override

- Extend/Override are useful mechanisms for expanding model support

- When do we make the decision to put something back into the base model?

## **Challenges to Scalable Modeling**

### Modeling capabilities

- Dynamic hardware problems still pose challenges to scalable modeling

- Dynamic bandwidth calculation/throttling

- Reconfigurable transport layer modeling

### Vendor/use case specialization

- Working in 2 languages is cumbersome

- Language support for vendor tool capabilities

- Randomization tools

- AI workflows/tools

### Scalable Subsystem/SoC support

- Intuitive model composition with multiple IP models

- Layered support for subsystem/SoC features

### Input collateral for model configuration

- Leveraging non-PSS config files

- Convert to PSS is the only option

**Q & A**

## **Panel Discussion**

SYSTEMS INITIATIVE